概述

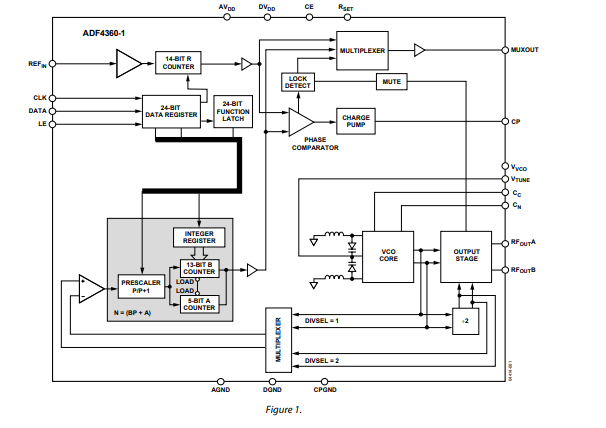

ADF4360-1是一款完全集成式整數(shù)N分頻頻率合成器和電壓控制振蕩器(VCO),設(shè)計的中心頻率為2250 MHz。此外,該器件還提供2分頻選項,用戶可以利用它獲得1025 MHz至1225 MHz的RF輸出。所有片內(nèi)寄存器均通過簡單的三線式接口進行控制。該器件采用3.0 V至3.6 V電源供電,不用時可以關(guān)斷。

數(shù)據(jù)表:*附件:ADF4360-1集成式整數(shù)N分頻頻率合成器和VCO,輸出頻率為2050至2450MHz技術(shù)手冊.pdf

特性

- 輸出頻率范圍:2050 MHz至2450 MHz

- 2分頻輸出

- 3.0 V至3.6 V電源供電

- 1.8 V邏輯兼容

- 整數(shù)N分頻頻率合成器

- 可編程雙模預(yù)分頻器:8/9、16/17、32/33

- 可編程輸出功率水平

- 三線式串行接口

- 模擬和數(shù)字鎖定檢測

- 硬件和軟件省電模式

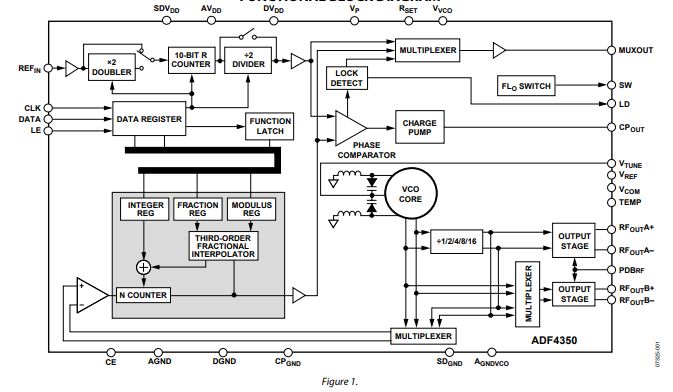

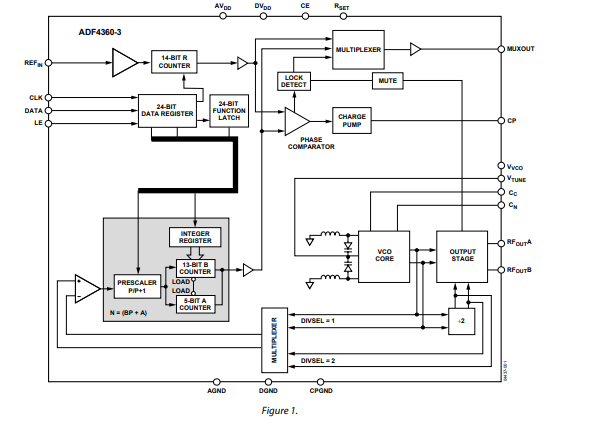

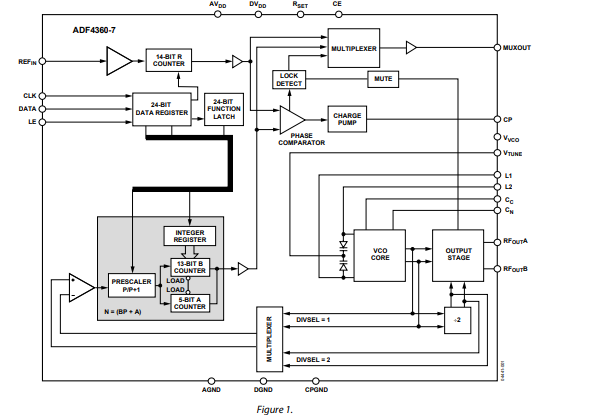

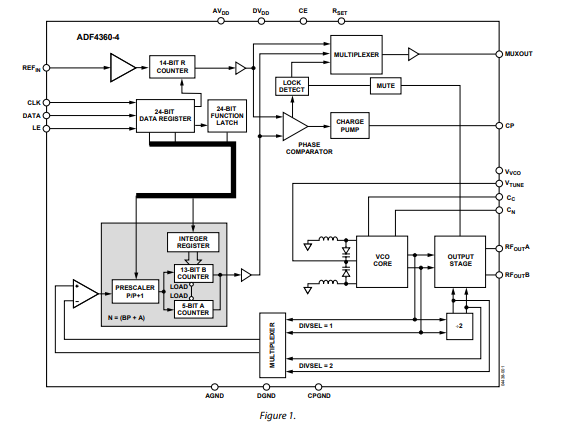

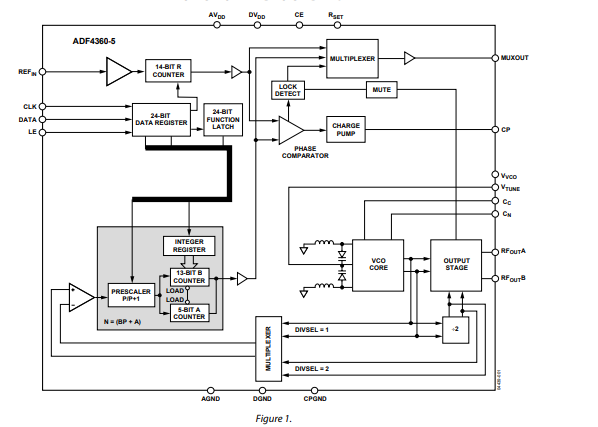

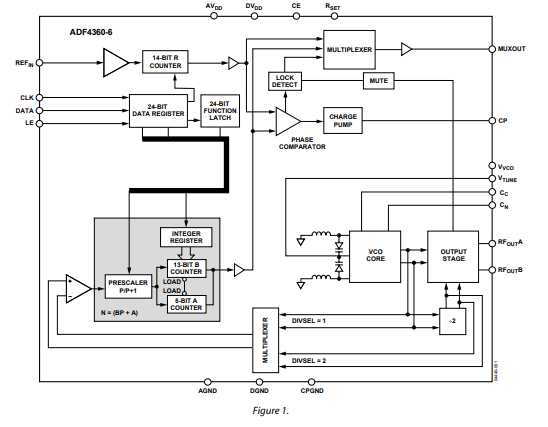

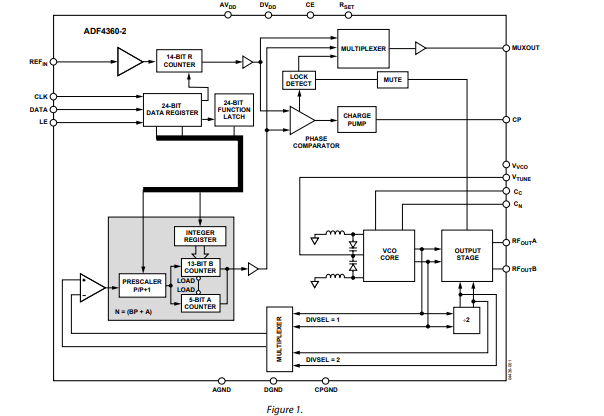

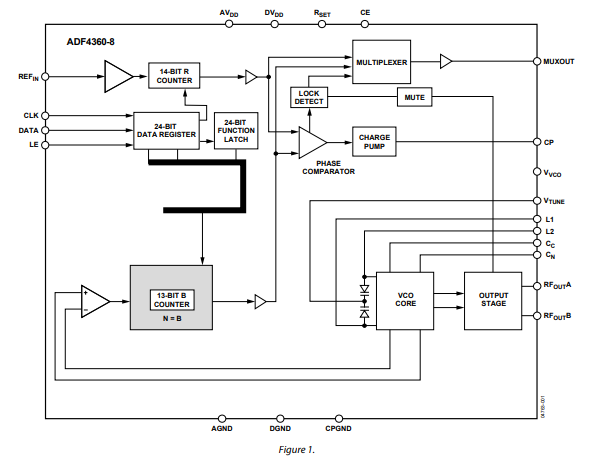

框圖

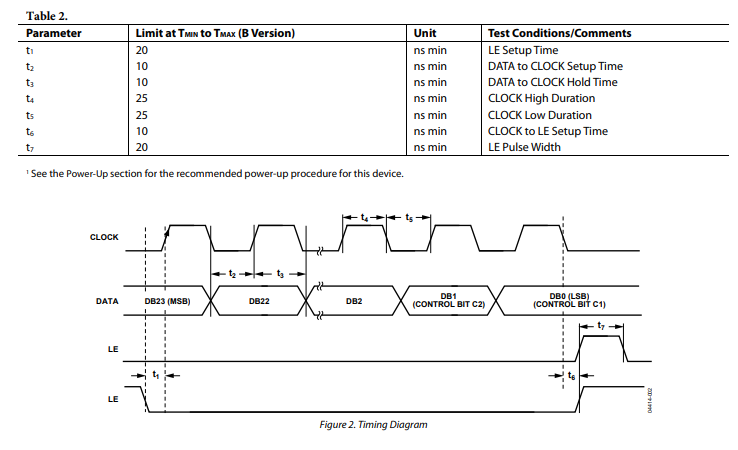

時序特征

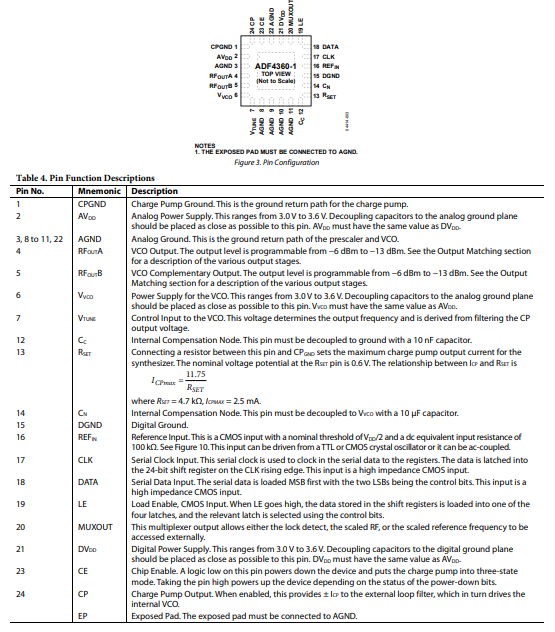

引腳配置描述

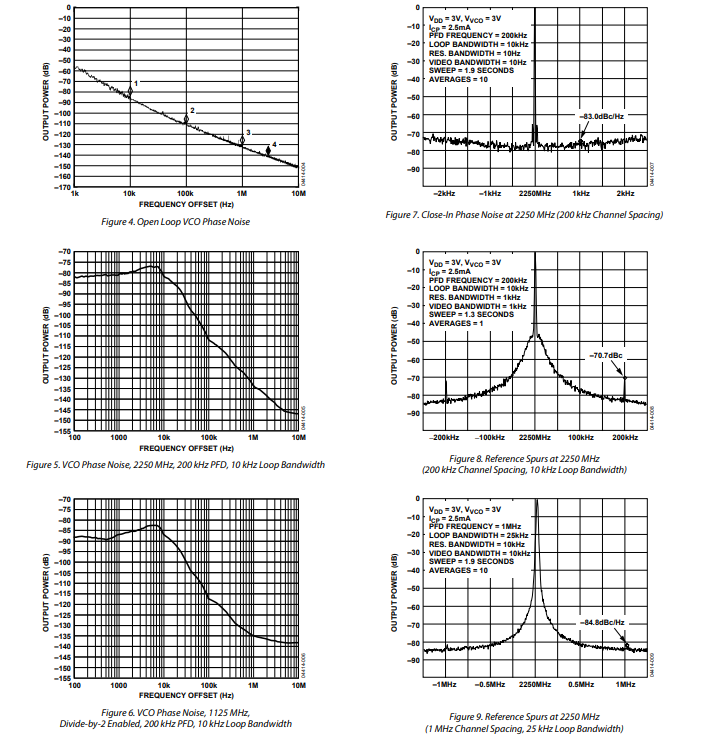

典型性能特征

電路說明

參考輸入部分

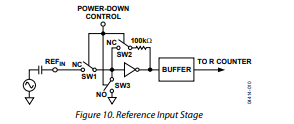

參考輸入級如圖10所示。SW1和SW2通常處于閉合狀態(tài),SW3通常處于斷開狀態(tài)。當啟動掉電模式時,SW3閉合,SW1和SW2斷開。這確保了在掉電時參考引腳((REF_{IN}))不會有負載。

預(yù)分頻器(P/P + 1)

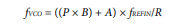

雙模數(shù)預(yù)分頻器(P/P + 1)與A計數(shù)器和B計數(shù)器配合,可實現(xiàn)較大的分頻比N((N = BP + A) )。雙模數(shù)預(yù)分頻器以電流模式邏輯(CML)電平工作,從壓控振蕩器(VCO)獲取時鐘信號,并將其分頻到適合CMOS A計數(shù)器和B計數(shù)器處理的頻率。預(yù)分頻器在軟件中可設(shè)置為8/9、16/17、32/33 ,基于同步4/5核心。對于完全連續(xù)的輸出頻率,存在一個由P(預(yù)分頻器值)決定的最小分頻比,其值為((P^2 - P)) 。

A計數(shù)器和B計數(shù)器

A計數(shù)器和B計數(shù)器(采用CMOS工藝)與雙模數(shù)預(yù)分頻器配合,可在鎖相環(huán)(PLL)反饋回路中實現(xiàn)較寬范圍的分頻比。當預(yù)分頻器的輸出為300 MHz或更低時,這些計數(shù)器可正常工作。因此,對于2.5 GHz的VCO頻率,預(yù)分頻器值16/17有效,但8/9無效。

脈沖吞咽功能

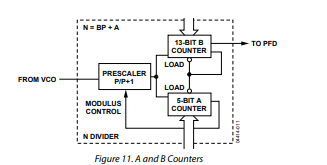

A計數(shù)器和B計數(shù)器與雙模數(shù)預(yù)分頻器配合,能夠生成間隔僅為參考頻率除以R的輸出頻率。壓控振蕩器(VCO)頻率的計算公式為:

其中:

- (f_{VCO})是壓控振蕩器(VCO)的輸出頻率。

- (P)是雙模數(shù)預(yù)分頻器的模數(shù)(如8/9、16/17等 )。

- (B)是13位二進制計數(shù)器的預(yù)設(shè)分頻比(3到8191)。

- (A)是6位吞咽計數(shù)器的預(yù)設(shè)分頻比(0到31)。

- (f_{REFIN})是外部參考頻率振蕩器的頻率。

- (R)是14位二進制可編程參考計數(shù)器的預(yù)設(shè)分頻比(1到16,383)。

R計數(shù)器

14位R計數(shù)器可對輸入?yún)⒖碱l率進行分頻,以產(chǎn)生送往鑒頻鑒相器(PFD)的參考時鐘。允許的分頻比范圍是1到16,383 。

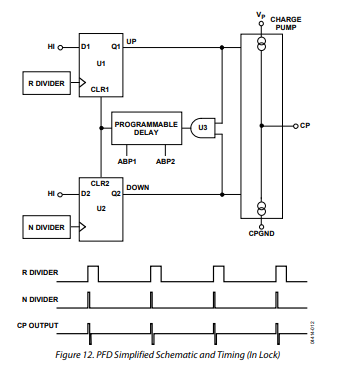

鑒頻鑒相器(PFD)和電荷泵

鑒頻鑒相器接收來自R計數(shù)器和N計數(shù)器((N = BP + A) )的輸入,并輸出一個與兩者之間相位和頻率差成正比的信號。圖12是簡化示意圖。鑒頻鑒相器包含一個可編程延遲元件,用于控制抗反沖脈沖的寬度。此脈沖功能確保了鑒頻鑒相器傳遞函數(shù)中不存在死區(qū),并將相位噪聲以及參考雜散降至最低。R計數(shù)器鎖存(ABP2和ABP1)中的兩位控制脈沖寬度(見表9)。

-

頻率合成器

+關(guān)注

關(guān)注

5文章

295瀏覽量

32728 -

VCO

+關(guān)注

關(guān)注

13文章

311瀏覽量

70022 -

分頻

+關(guān)注

關(guān)注

0文章

253瀏覽量

25087

發(fā)布評論請先 登錄

ADF4360-1 集成式整數(shù)N分頻頻率合成器和VCO,輸出頻率為2050至2450 MHz

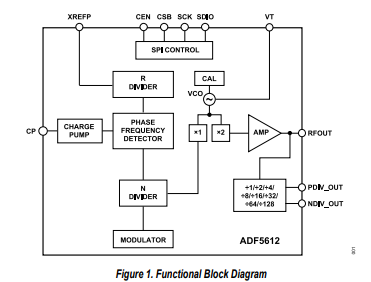

ADF5612集成VCO的微波寬帶頻率合成器技術(shù)手冊

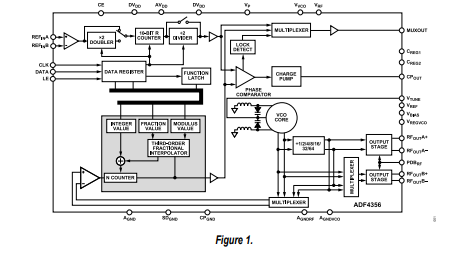

ADF4356集成VCO的6.8 GHz寬帶頻率合成器技術(shù)手冊

ADF4360-1集成式整數(shù)N分頻頻率合成器和VCO,輸出頻率為2050至2450MHz技術(shù)手冊

ADF4360-1集成式整數(shù)N分頻頻率合成器和VCO,輸出頻率為2050至2450MHz技術(shù)手冊

評論