概述

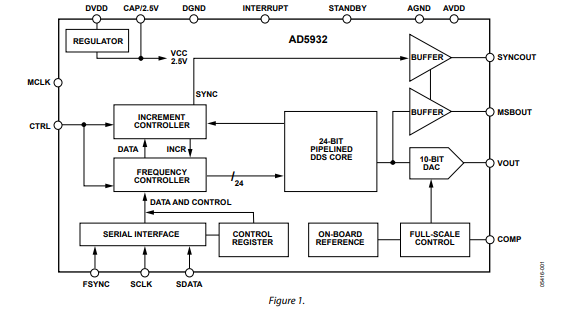

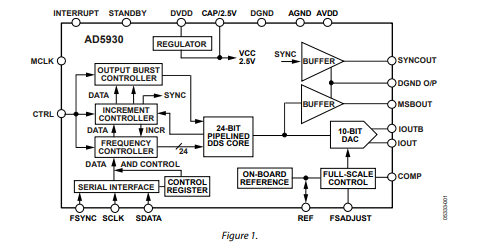

AD5932是一款提供可編程頻率掃描的波形發(fā)生器。這款器件采用支持增強(qiáng)型頻率控制的嵌入式數(shù)字處理技術(shù),能夠生成合成的模擬或數(shù)字頻率步進(jìn)波形。采用預(yù)先編程的頻率配置文件可以避免連續(xù)的寫周期,從而釋放了重要的DSP/微控制器資源。波形從已知相位開始,并可以連續(xù)地增加相位,因此能夠輕松的確定相移。AD5932功耗僅為6.7 mA,為波形產(chǎn)生提供方便的低功耗解決方案。

數(shù)據(jù)表:*附件:AD5932可編程單掃描波形發(fā)生器技術(shù)手冊(cè).pdf

AD5932在目標(biāo)范圍內(nèi)的定義時(shí)長(zhǎng)內(nèi)輸出各頻率,然后在掃描范圍內(nèi)步入下一頻率。可對(duì)該器件輸出特定頻率的時(shí)長(zhǎng)進(jìn)行預(yù)先編程并讓器件自動(dòng)遞增該頻率;或者,頻率通過CTRL引腳進(jìn)行外部遞增。在范圍結(jié)束時(shí),AD5932繼續(xù)輸出最后一個(gè)頻率直至重置器件。另外,AD5932還通過MSBOUT引腳提供數(shù)字輸出。

對(duì)AD5932進(jìn)行編程時(shí),用戶需要輸入起始頻率、頻率步進(jìn)、增量數(shù)量,以及器件輸出各頻率的時(shí)間間隔。頻率掃描配置文件可通過切換CTRL引腳來啟動(dòng)和執(zhí)行。

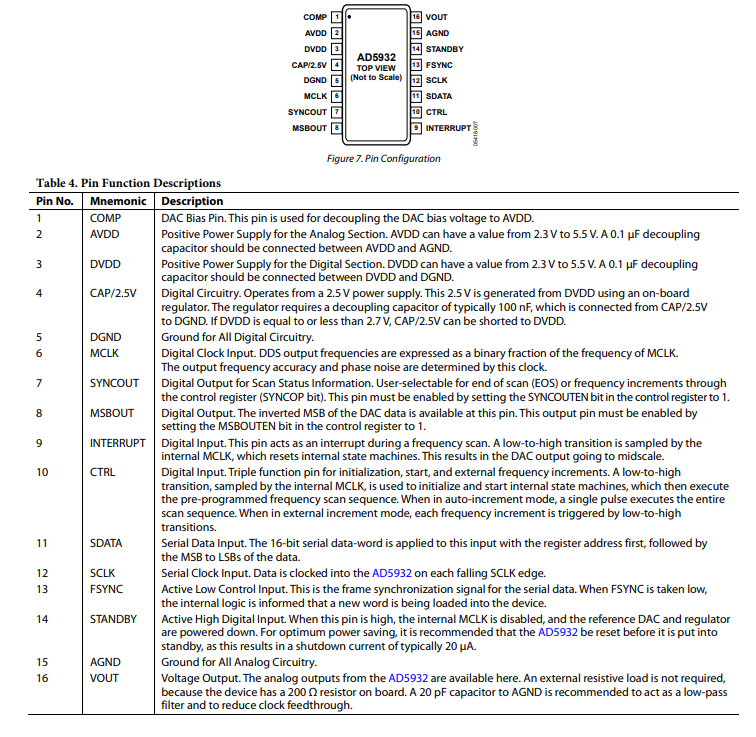

AD5932通過三線式串行接口寫入數(shù)據(jù),能夠在高達(dá)40 MHz的時(shí)鐘速率下工作。該器件采用2.3 V至5.5 V電源供電。

請(qǐng)注意,AVDD和DVDD彼此獨(dú)立并可采用不同的電壓工作。AD5932還具有待機(jī)功能,能夠關(guān)斷器件中沒有使用的部分。

AD5932提供16引腳、無鉛TSSOP封裝。

應(yīng)用

- 頻率掃描/雷達(dá)

- 網(wǎng)絡(luò)/阻抗測(cè)量

- 增量式頻率激勵(lì)

- 傳感器應(yīng)用

– 近距和運(yùn)動(dòng)

特性

- 可編程頻率配置文件;無需外部元件

- 輸出頻率高達(dá)25 MHz

- 預(yù)編程的頻率配置文件能將DSP/微控制器的寫操作次數(shù)減到最少

- 正弦波/三角波/方波輸出

- 頻率步進(jìn)的自動(dòng)或單引腳控制

- 關(guān)斷模式:20 μA

- 電源:2.3 V至5.5 V

- 汽車應(yīng)用溫度范圍:-40°C至+125°C

- 16引腳、無鉛TSSOP封裝

框圖

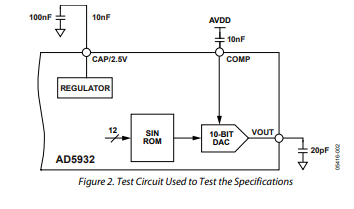

規(guī)格測(cè)試電路

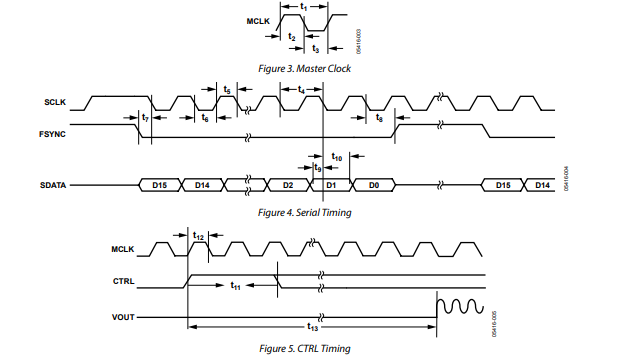

主時(shí)鐘和時(shí)序圖

引腳配置描述

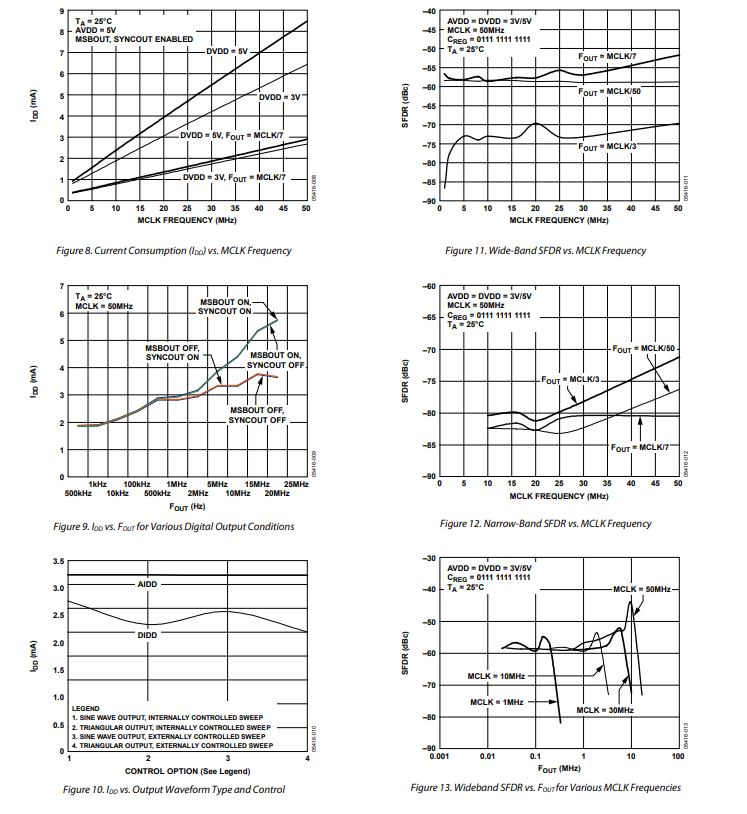

典型性能特征

AD5932是一款通用型合成波形發(fā)生器,能夠提供數(shù)字可編程波形,涵蓋頻率和時(shí)域范疇。該器件內(nèi)置嵌入式頻率處理功能,可對(duì)用戶可編程的頻率曲線進(jìn)行掃描,從而增強(qiáng)頻率控制能力。由于該器件具備預(yù)編程特性,它能從數(shù)字信號(hào)處理器(DSP)/微控制器的連續(xù)寫周期中解脫出來,以生成特定波形。

頻率曲線

頻率曲線由起始頻率(FSTART)、頻率增量(Δf)和頻率掃描中的增量數(shù)(NSTEP)定義。頻率增量之間的時(shí)間間隔(TINT),可由器件自動(dòng)確定(自動(dòng)增量模式),也可通過硬件引腳(外部增量模式)進(jìn)行外部控制。對(duì)于自動(dòng)更新,時(shí)間間隔可以是固定數(shù)量的時(shí)鐘周期,或是固定數(shù)量的輸出波形周期。

在自動(dòng)增量模式下,CTRIL引腳的單個(gè)脈沖會(huì)啟動(dòng)并執(zhí)行頻率掃描。在外部增量模式下,CTRIL引腳同樣會(huì)啟動(dòng)掃描,但頻率增量間隔由CTRIL引腳上連續(xù)0/1轉(zhuǎn)換之間的時(shí)間間隔決定。

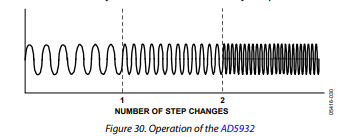

圖30展示了一個(gè)2步頻率掃描的示例。請(qǐng)注意,AD5932的頻率輸出信號(hào)是連續(xù)可用的,因此在所有頻率增量下相位都是連續(xù)的。

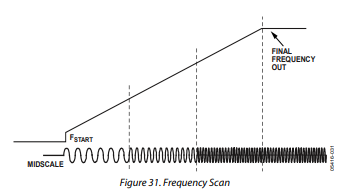

當(dāng)AD5932完成從起始頻率到最終頻率的頻率掃描時(shí)(見圖31),從FSTART開始,以增量方式增加(FSTART + NSTEP × Δf),它會(huì)持續(xù)輸出掃描中的最后一個(gè)頻率。需注意,頻率掃描時(shí)間由(NSTEP + 1)× TINT給出。

串行接口

AD5932具有標(biāo)準(zhǔn)的三線串行接口,與SPI*、QSPI*、MICROWIRE*和DSP接口標(biāo)準(zhǔn)兼容。

在串行時(shí)鐘輸入SCLK的控制下,數(shù)據(jù)以16位字的形式加載到器件中。此操作的時(shí)序圖如圖4所示。

FSYNC輸入是一個(gè)電平觸發(fā)輸入,起到幀同步和芯片使能的作用。只有在FSYNC為低電平時(shí),才能將數(shù)據(jù)傳輸?shù)狡骷小R_始串行數(shù)據(jù)傳輸,F(xiàn)SYNC應(yīng)拉低,并遵循最小的FSYNC到SCLK下降沿建立時(shí)間ts。在FSYNC變?yōu)榈碗娖胶螅赟CLK的下降沿,數(shù)據(jù)會(huì)移入器件的輸入移位寄存器。在第16個(gè)SCLK下降沿之后,F(xiàn)SYNC可以拉高,但需遵循最小的SCLK到FSYNC上升沿建立時(shí)間tu。或者,F(xiàn)SYNC可以在多個(gè)16個(gè)SCLK脈沖期間保持低電平,然后在數(shù)據(jù)傳輸結(jié)束時(shí)拉高。這樣,F(xiàn)SYNC就是一個(gè)連續(xù)的16位字的數(shù)據(jù)流。在這種情況下,F(xiàn)SYNC應(yīng)在第16個(gè)SCLK下降沿之后拉高。最后一個(gè)字只能在FSYNC拉高后加載。

SCLK可以是連續(xù)的,或者,SCLK可以空閑為高電平或低電平,以進(jìn)行寫操作。

給AD5932上電

AD5932上電時(shí),器件處于未定義狀態(tài),因此在使用前必須進(jìn)行復(fù)位。七個(gè)寄存器(控制寄存器和頻率寄存器)必須重置為已知值。控制寄存器組應(yīng)是用戶編程的第一個(gè)寄存器,這樣可以設(shè)置器件。需注意,對(duì)控制寄存器的寫入會(huì)自動(dòng)重置內(nèi)部狀態(tài)機(jī),并提供模擬輸出的中間刻度,因?yàn)樗cINTERRUPT引腳執(zhí)行相同的功能。通常,接下來是加載所有所需的頻率參數(shù)。在頻率掃描開始之前,DAC輸出保持在中間刻度,直到在CTRIL引腳處觸發(fā)。

-

發(fā)生器

+關(guān)注

關(guān)注

4文章

1403瀏覽量

62641 -

波形發(fā)生器

+關(guān)注

關(guān)注

3文章

307瀏覽量

31903 -

AD5932

+關(guān)注

關(guān)注

0文章

3瀏覽量

6517

發(fā)布評(píng)論請(qǐng)先 登錄

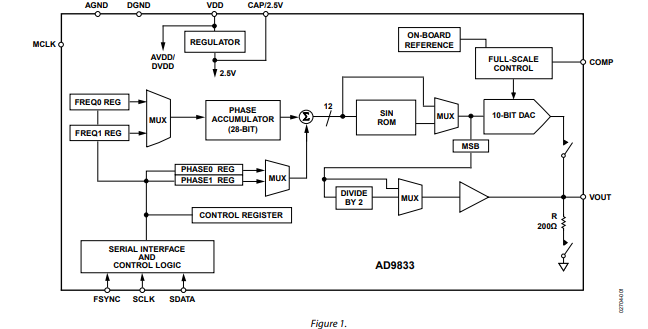

基于AD9833的高精度可編程波形發(fā)生器系統(tǒng)設(shè)計(jì)

AD9833型高精度可編程波形發(fā)生器設(shè)計(jì)方案

基于DDS的可編程的波形發(fā)生器

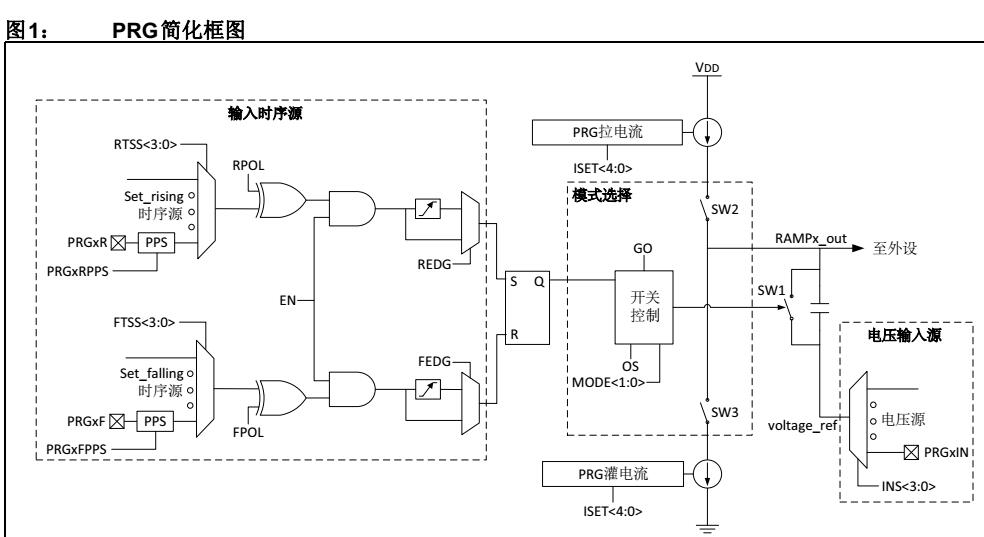

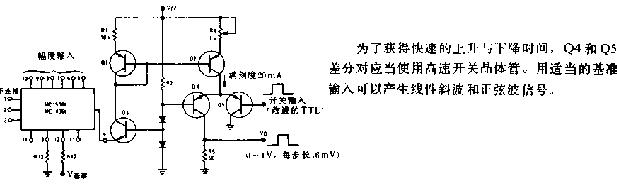

TB3140- 可編程斜坡發(fā)生器

AD5932 可編程單掃描波形發(fā)生器

AD9837: 低功耗、8.5 mW、2.3 V至5.5 V可編程波形發(fā)生器

AD5930:可編程掃頻和輸出猝發(fā)波形發(fā)生器數(shù)據(jù)表

EVAD5932 AD5932 評(píng)估板

任意波形發(fā)生器的基本架構(gòu)

AD5930可編程頻率掃描及輸出突發(fā)波形發(fā)生器技術(shù)手冊(cè)

AD9833低功耗、12.65 mW、2.3 V至+5.5 V可編程波形發(fā)生器技術(shù)手冊(cè)

AD5932可編程單掃描波形發(fā)生器技術(shù)手冊(cè)

AD5932可編程單掃描波形發(fā)生器技術(shù)手冊(cè)

評(píng)論