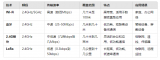

2.4GHz芯片通過射頻信號實現無線通信,其核心原理涉及物理層信號處理、協議控制與系統(tǒng)優(yōu)化,具體機制如下:

一、物理層架構

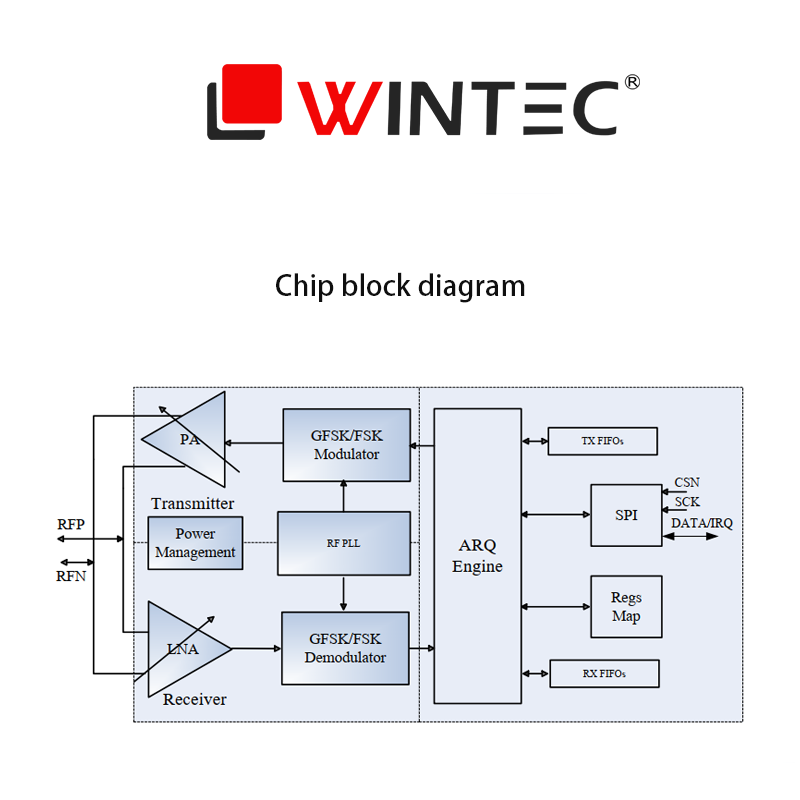

射頻前端?

混頻器與調制?:將基帶信號與2.4GHz載波混頻,完成頻譜搬移,常用GFSK/FSK調制技術實現信號編碼?。

功率放大器(PA)?:提升發(fā)射信號功率至-5dBm~+20dBm范圍,確保有效傳輸距離?。

低噪聲放大器(LNA)?:接收端放大微弱射頻信號(如-90dBm級),噪聲系數需<3dB以保證靈敏度?。

頻率合成器?

鎖相環(huán)(PLL)?:通過外置晶振生成精確的2.4GHz載波,相位噪聲<-100dBc/Hz@1MHz偏移?。

跳頻控制?:在79個1MHz信道間快速切換(如1600跳/秒),規(guī)避Wi-Fi等干擾源?。

二、信號處理流程

發(fā)射鏈路?

數據封裝?:將應用層數據添加包頭、CRC校驗等字段,形成協議幀?。

調制編碼?:采用GFSK調制(藍牙)或QPSK(Wi-Fi),頻偏±250kHz(1Mbps速率)?。

上變頻與功率控制?:基帶信號混頻至2.4GHz頻段,動態(tài)調整PA輸出功率以降低功耗?。

接收鏈路?

下變頻與AGC?:接收信號經混頻恢復基帶,自動增益控制(AGC)動態(tài)調節(jié)60dB以上增益?。

同步與解調?:通過前導碼實現載波同步(頻率偏移<±150kHz)和符號同步,解碼后執(zhí)行CRC校驗?。

三、協議控制機制

狀態(tài)與時序管理?

連接狀態(tài)機?:控制芯片在掃描、連接、休眠等狀態(tài)間切換,時隙分配精度達μs級(如BLE的625μs時隙)?。

低功耗策略?:休眠模式下電流低至μA級,喚醒時間<1ms?。

干擾規(guī)避?

自適應跳頻?:實時檢測信道誤碼率(PER),動態(tài)屏蔽干擾信道?。

沖突避免?:采用CSMA/CA機制(載波偵聽多路訪問/沖突避免),隨機退避窗口減少數據碰撞?。

四、系統(tǒng)設計要點

頻率穩(wěn)定性?:依賴高精度晶振(±10ppm~±40ppm),確保跳頻同步與低誤碼率?。

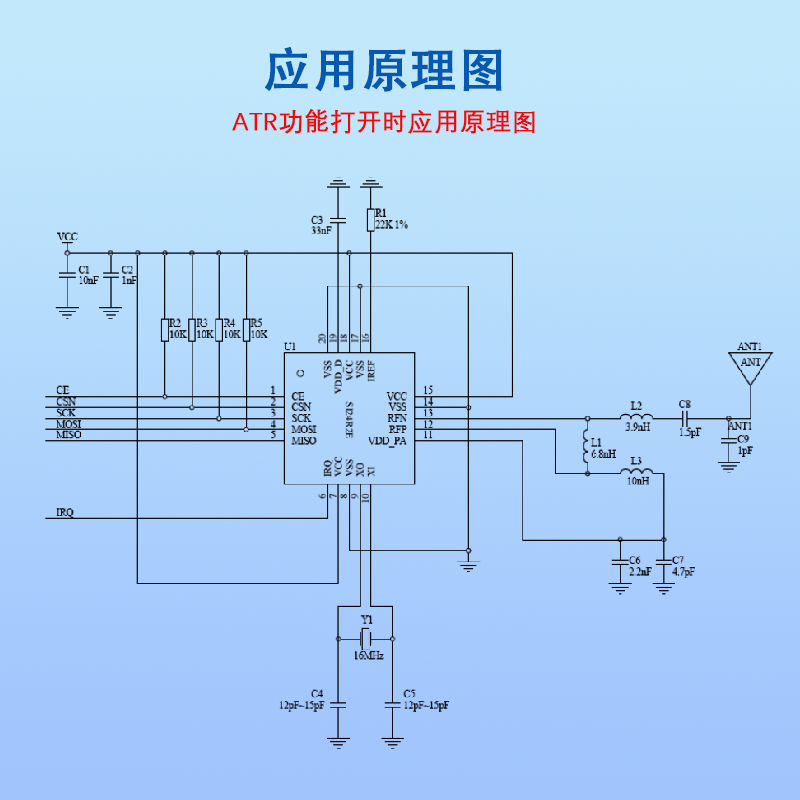

天線設計?:通過巴倫電路實現差分信號轉單端,阻抗匹配至50Ω,駐波比<2:1?。

功耗優(yōu)化?:分時啟閉PA/LNA模塊,平均功耗可降至nW級(如Zigbee芯片)?。

2.4GHz芯片通過上述技術協同實現高速、低功耗、抗干擾的無線通信,廣泛應用于物聯網、消費電子及工業(yè)控制領域?。

審核編輯 黃宇

-

芯片

+關注

關注

459文章

52323瀏覽量

438203 -

2.4G

+關注

關注

1文章

113瀏覽量

40393

發(fā)布評論請先 登錄

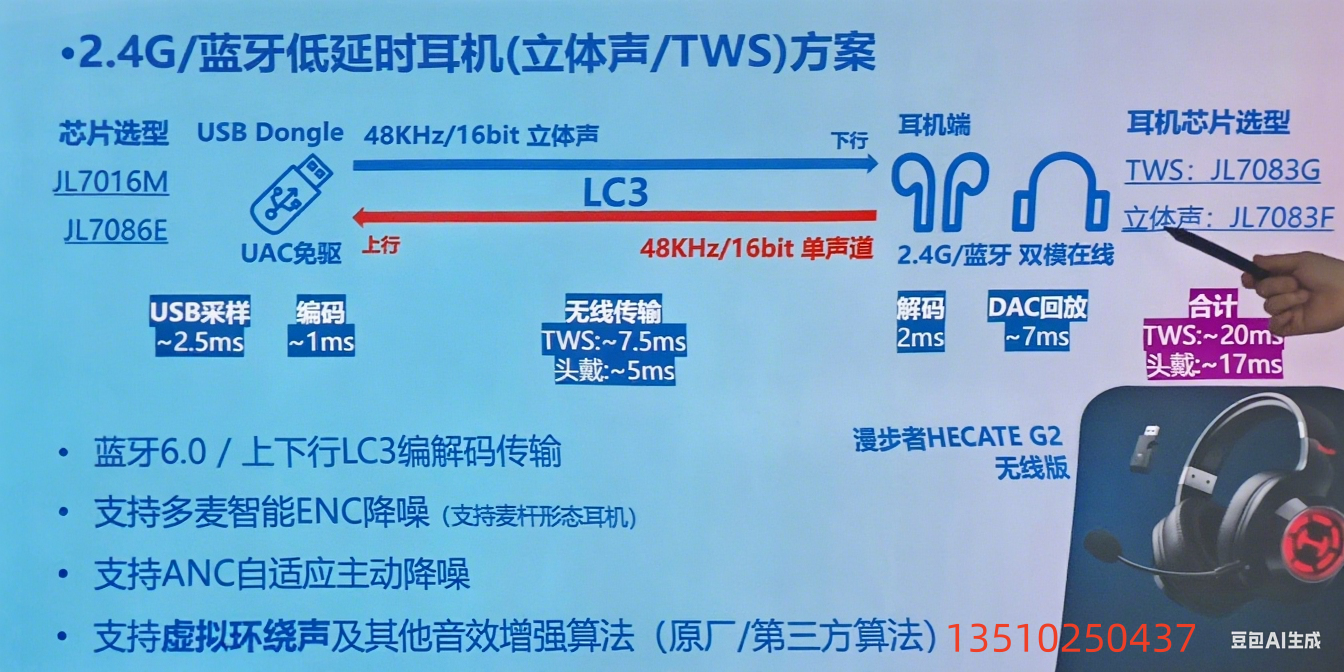

杰理 2.4G 藍牙音頻低延時耳機方案:芯片選型 延時 硬件設計

國產 2.4G 芯片:從技術突破到產業(yè)應用的國產化之路

2.4g芯片方案

2.4g芯片無晶振影響大不大?

2.4G芯片DFN封裝的作用是什么

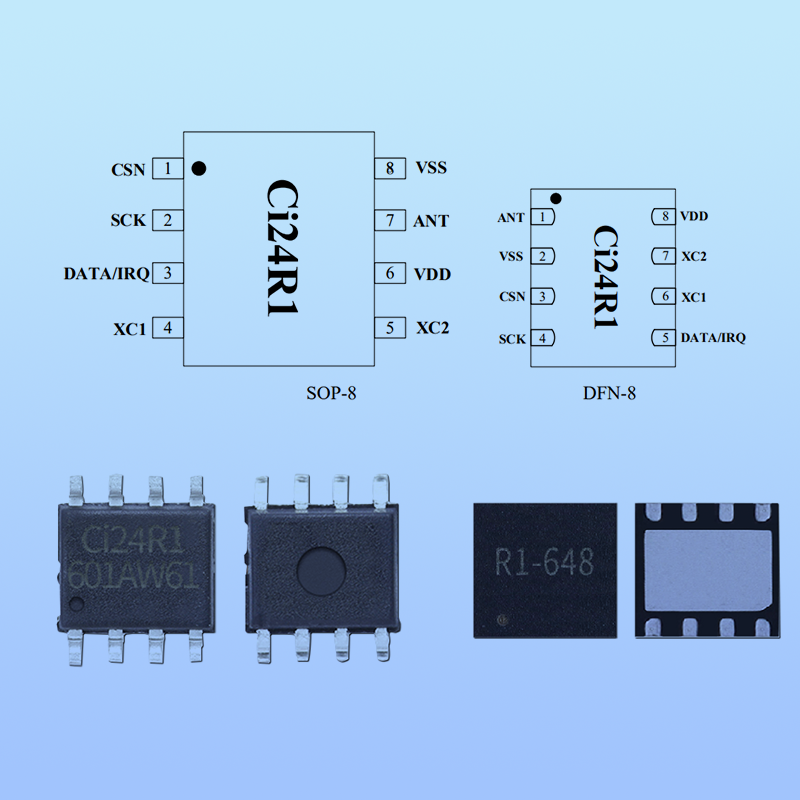

基于CI24R1的2.4G無線門鈴應用方案概述

安信可推出2.4G LoRa模塊!高線性度抗干擾強!

安信可推出2.4G LoRa模塊Ra-05/Ra-05U

AT2401C 功率放大器(PA)2.4g集成芯片 完全取代替代RFX2401C兼容軟件硬件

通信模塊兼容SUB-GHz 和2.4G 通信會帶來哪些優(yōu)勢

將WiFi芯片和BT芯片或Lora 2.4G Hz芯片放在同一個板上會有問題嗎?

Ci24R1:低功耗、高性能的2.4G射頻芯片特性及應用領域解讀

2.4g芯片工作原理詳解

2.4g芯片工作原理詳解

評論