NVMe需要用AXI總線進(jìn)行高速傳輸。這里,AXI總線是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)協(xié)議中的重要組成部分,主要面向高性能、高帶寬、低延時(shí)的片內(nèi)互連需求。AXI4總線則是AXI總線的第四代版本,主要包含三種類型的接口,分別是面向高性能地址映射通信的AXI4接口、面向輕量級(jí)單次地址映射通信的AXI4-Lite接口和面向高速數(shù)據(jù)流傳輸?shù)腁XI4-Stream接口。如表1所示展示了三種類型接口的主要特點(diǎn)對(duì)比。

表1 三種類型AXI4接口對(duì)比

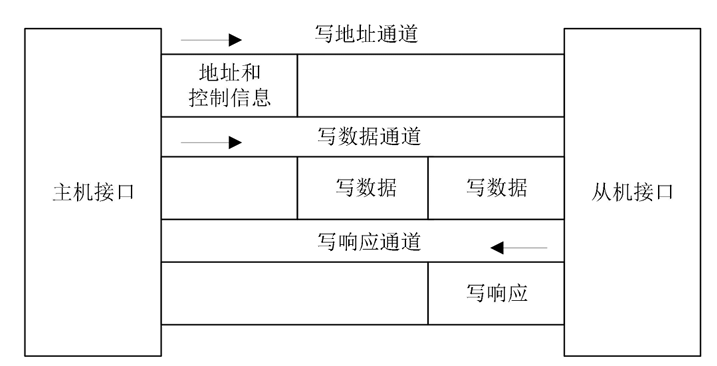

AXI4總線具有讀寫(xiě)地址、數(shù)據(jù)通道分離的特性,使控制通道與數(shù)據(jù)通道分離、讀通道與寫(xiě)通道分離,從而具有并行處理的能力,大幅提高了總線傳輸帶寬和傳輸效率。AXI4總線可分為寫(xiě)通道和讀通道。寫(xiě)通道由寫(xiě)地址通道、寫(xiě)數(shù)據(jù)通道、寫(xiě)響應(yīng)通道組成。寫(xiě)地址通道數(shù)據(jù)流從主機(jī)指向從機(jī),主要傳遞地址和控制信息;寫(xiě)數(shù)據(jù)通道數(shù)據(jù)流從主機(jī)指向從機(jī),主要傳遞數(shù)據(jù)信息;寫(xiě)響應(yīng)通道數(shù)據(jù)流從從機(jī)指向主機(jī),主要反饋寫(xiě)請(qǐng)求事務(wù)的響應(yīng)信息。如圖2所示為寫(xiě)通道組成結(jié)構(gòu)。

AXI 寫(xiě)通道架構(gòu)示意圖

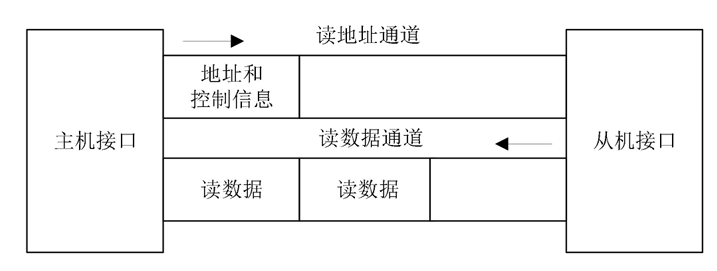

讀通道與寫(xiě)通道有相似的結(jié)構(gòu),由讀地址通道和讀數(shù)據(jù)通道組成。讀地址通道數(shù)據(jù)流從主機(jī)指向從機(jī),實(shí)現(xiàn)地址和控制信息的傳遞;讀數(shù)據(jù)通道數(shù)據(jù)流由從機(jī)指向主機(jī),實(shí)現(xiàn)數(shù)據(jù)的傳輸。與寫(xiě)通道相比,讀通道沒(méi)有單獨(dú)的響應(yīng)通道,讀響應(yīng)信息包含在讀數(shù)據(jù)通道中由從機(jī)反饋到主機(jī)。如圖3所示為讀通道組成結(jié)構(gòu)。

圖3 AXI 讀通道架構(gòu)

審核編輯 黃宇

-

接口

+關(guān)注

關(guān)注

33文章

8990瀏覽量

153639 -

總線

+關(guān)注

關(guān)注

10文章

2959瀏覽量

89679 -

AXI

+關(guān)注

關(guān)注

1文章

136瀏覽量

17223 -

nvme

+關(guān)注

關(guān)注

0文章

251瀏覽量

23214

發(fā)布評(píng)論請(qǐng)先 登錄

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)之十:NVMe初始化狀態(tài)機(jī)設(shè)計(jì)

NVMe IP高速傳輸擺脫XDMA設(shè)計(jì)之四:系統(tǒng)控制模塊設(shè)計(jì)

NVMe IP高速傳輸卻不依賴便利的XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

RDMA簡(jiǎn)介9之AXI 總線協(xié)議分析2

RDMA簡(jiǎn)介8之AXI 總線協(xié)議分析1

NVMe協(xié)議研究掃盲

NVMe IP之AXI4總線分析

NVMe協(xié)議簡(jiǎn)介之AXI總線

NVMe協(xié)議簡(jiǎn)介2

NVMe控制器IP設(shè)計(jì)之接口轉(zhuǎn)換

NVME控制器之隊(duì)列管理模塊

NVMe控制器設(shè)計(jì)1

Xilinx NVMe AXI4主機(jī)控制器,AXI4接口高性能版本介紹

NVMe簡(jiǎn)介之AXI總線

NVMe簡(jiǎn)介之AXI總線

評(píng)論