在工業通信領域,技術革新與突破始終是推動行業發展的核心動力。今天,為大家帶來基于DSMC/FlexBus并口的RK3576J與FPGA通信方案,核心板國產化率高達100%,為工控場景帶來高效、穩定的通信新體驗。下面一起來看看! 開發環境與測試數據 本文主要介紹RK3576J與FPGA的通信案例,適用開發環境如下:

Windows開發環境:Windows 7 64bit、Windows 10 64bit

Linux開發環境:VMware16.2.5、Ubuntu22.04.5 64bit

U-Boot:U-Boot-2017.09

Kernel:Linux-6.1.115

Buildroot文件系統版本:Buildroot-2024.02

LinuxSDK:LinuxSDK-[版本號](基于rk3576_linux6.1_release_v1.1.0)

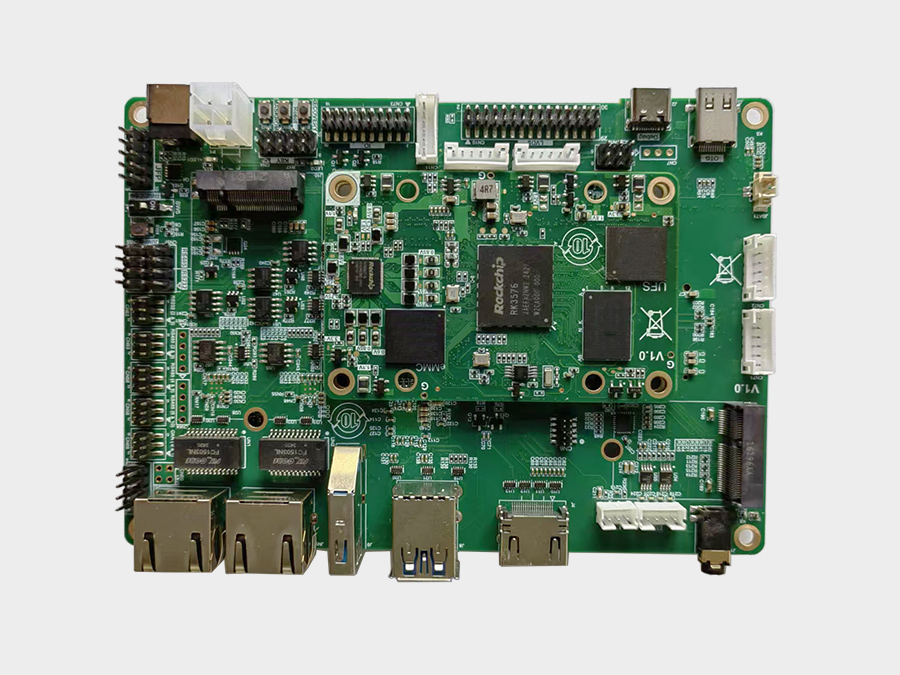

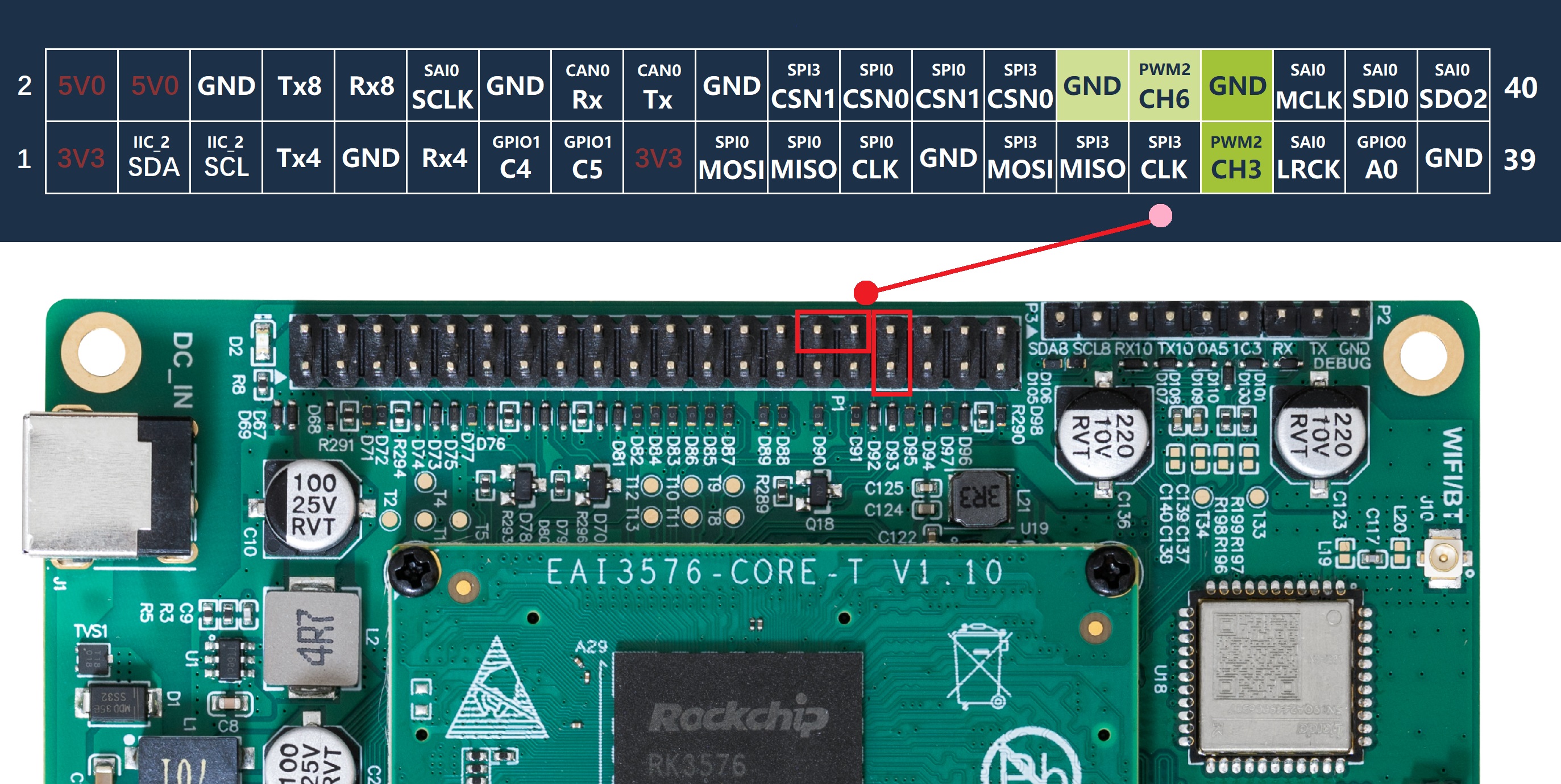

硬件平臺:創龍科技TL3576-EVM工業評估板(基于瑞芯微RK3576J)

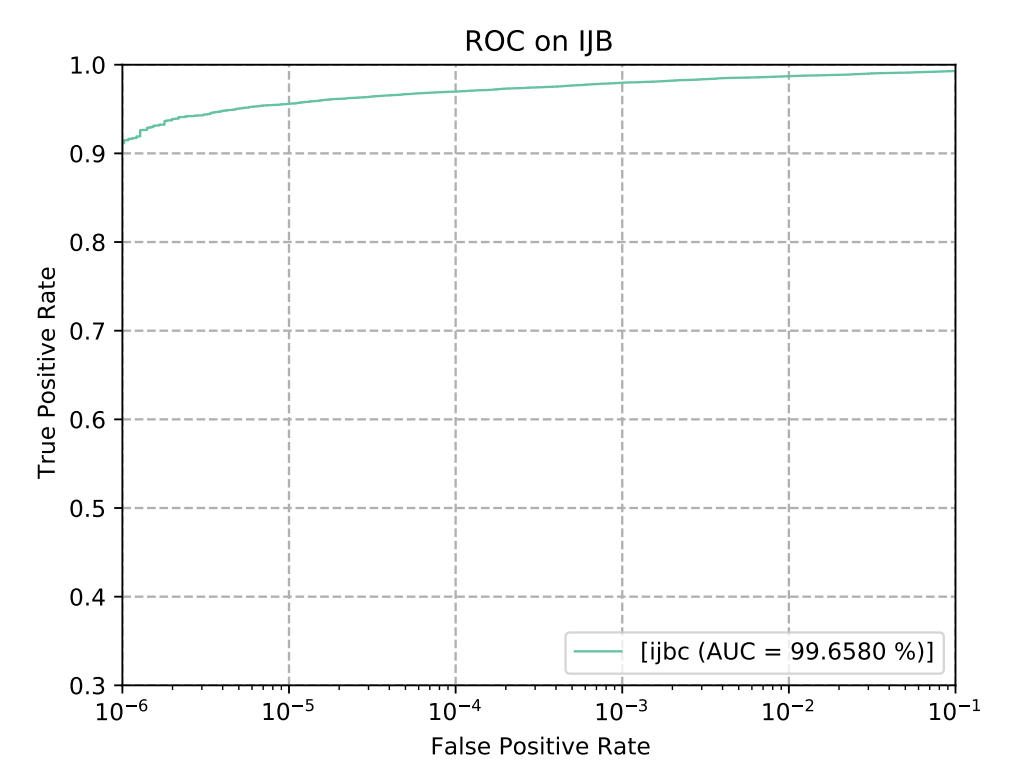

為了簡化描述,本文僅摘錄部分方案功能描述與測試結果,詳細產品資料請掃描文末二維碼下載。 通過實測我們發現,基于DSMC和FlexBus的通信方案具備了出色性能,數據如下表所示:

| 案例 | 理論速率 | 測試結果 |

| 基于DSMC的ARM與FPGA通信案例(dsmc_localbus_dma_rw) |

讀速率:400MB/s 寫速率:400MB/s |

讀速率:216MB/s 寫速率:280MB/s |

| 基于FlexBus的ARM與FPGA通信案例(flexbus_rw) |

讀速率:200MB/s 寫速率:200MB/s |

讀速率:166MB/s 寫速率:165MB/s |

FPGA數采模塊簡介

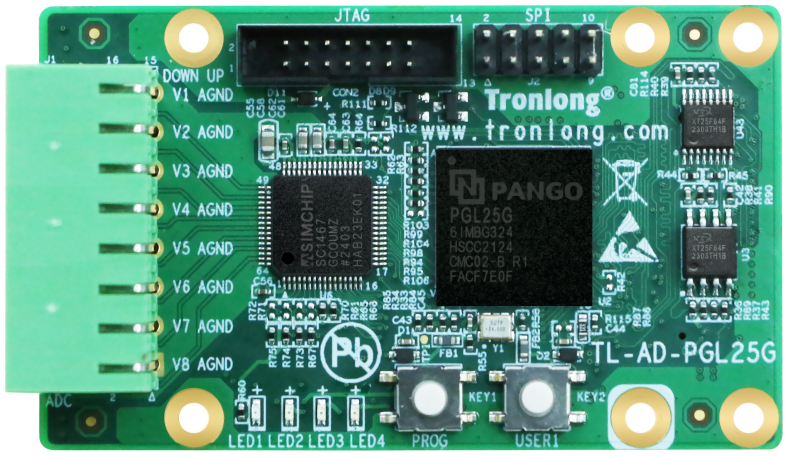

創龍科技TL-AD-PGL25G是一款基于紫光同創Logos PGL25G FPGA與芯熾科技SC1467/核芯互聯CL1606/ADI AD7606 ADC設計的數據采集模塊,支持8通道、200KSPS串行/并行采樣,可與ARM端通過DSMC、FlexBus、Local Bus、SPI等總線進行通信,滿足客戶多樣化數據采集需求。

TL-AD-PGL25G模塊正面圖

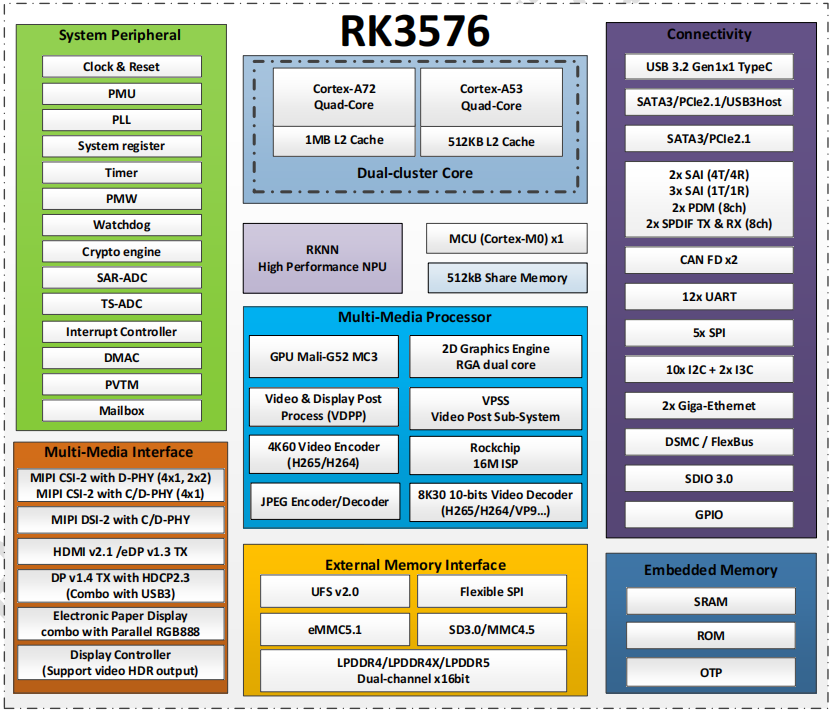

DSMC與FlexBus并口簡介 專為工業應用設計,DSMC(Double Data Rate Serial Memory Controller)作為高速并行總線接口,兼容多種傳輸協議,包括HyperBus PSRAM、Xccela PSRAM和Local Bus。對于RK3576J處理器,DSMC接口若使用Local Bus協議,從設備需使用瑞芯微開發的slave模型,或者傳輸協議相同。DSMC接口支持8/16bit串行傳輸模式,時鐘速率高達100MHz,可實現FPGA低成本連接,具有低延遲、高帶寬和靈活配置的特點,廣泛應用于需要高速通信的工業控制領域。 FlexBus是一個高度靈活的并行總線接口,可模擬標準或不規則的協議,能夠適應各種復雜的通信場景。對于RK3576J處理器,FlexBus支持2/4/8/16bit并行傳輸,時鐘速率高達100MHz,可實現高速AD/DA拓展,可以在保障數據穩定性的同時實現高效、低延遲的數據交互。這一特性使其在高速數據采集場景中具有顯著優勢。

RK3576J典型應用場景

高端工業PLC

運動控制器

工業計算機

無人機

電力監測裝置

4K醫療內窺鏡

基于DSMC的ARM與FPGA通信案例

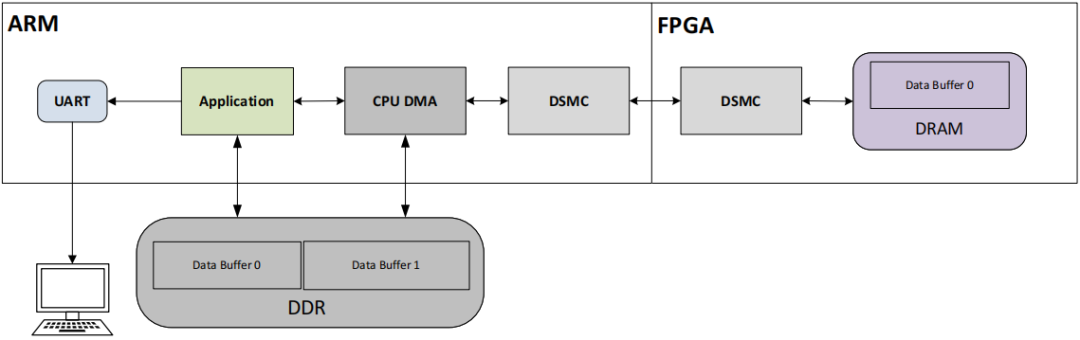

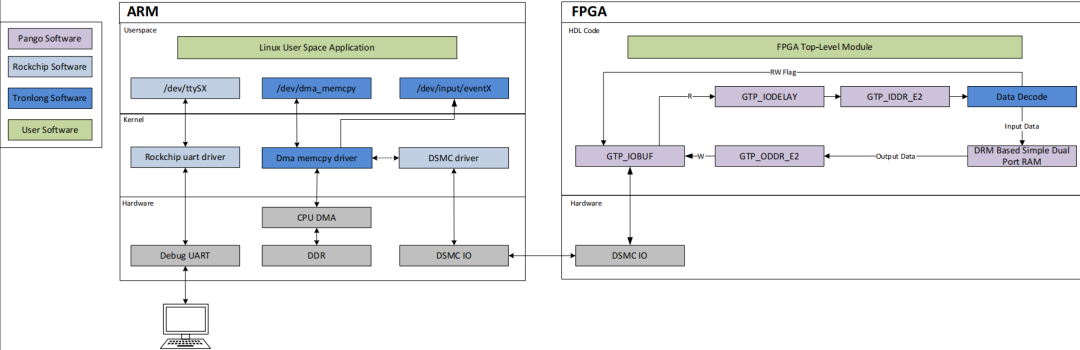

案例說明

ARM端運行Linux系統,基于DSMC總線對FPGA DRAM進行讀寫測試。 程序原理說明如下:

ARM端:

ARM端使用CPU DMA通過DSMC總線(作為Local Bus Master)來對FPGA DRAM進行讀寫測試。

通過參數設置數據包大小(數據包數據每次循環均為新的隨機數)、數據傳輸的循環次數。

對讀寫的數據進行校驗,并打印誤碼率和讀寫速率。

FPGA端:

實現Local Bus Slave功能。

將Local Bus Master(ARM)發送的64KByte數據保存到DRAM。

當Local Bus Master(ARM)讀取64KByte數據時,FPGA從DRAM讀取64KByte數據發送至Local Bus。

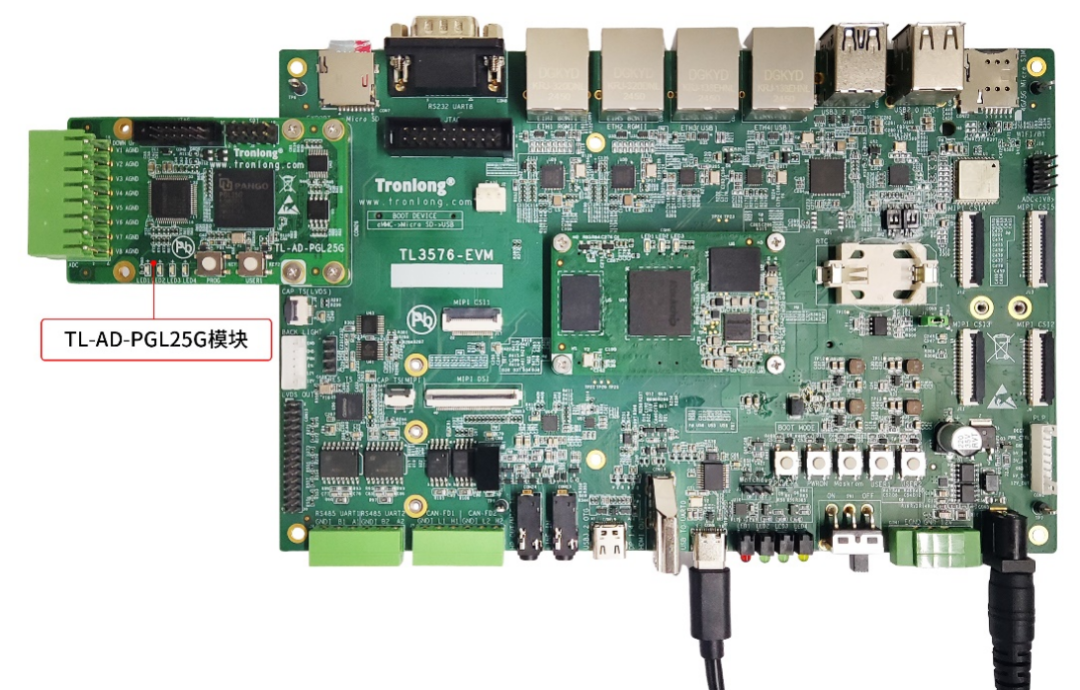

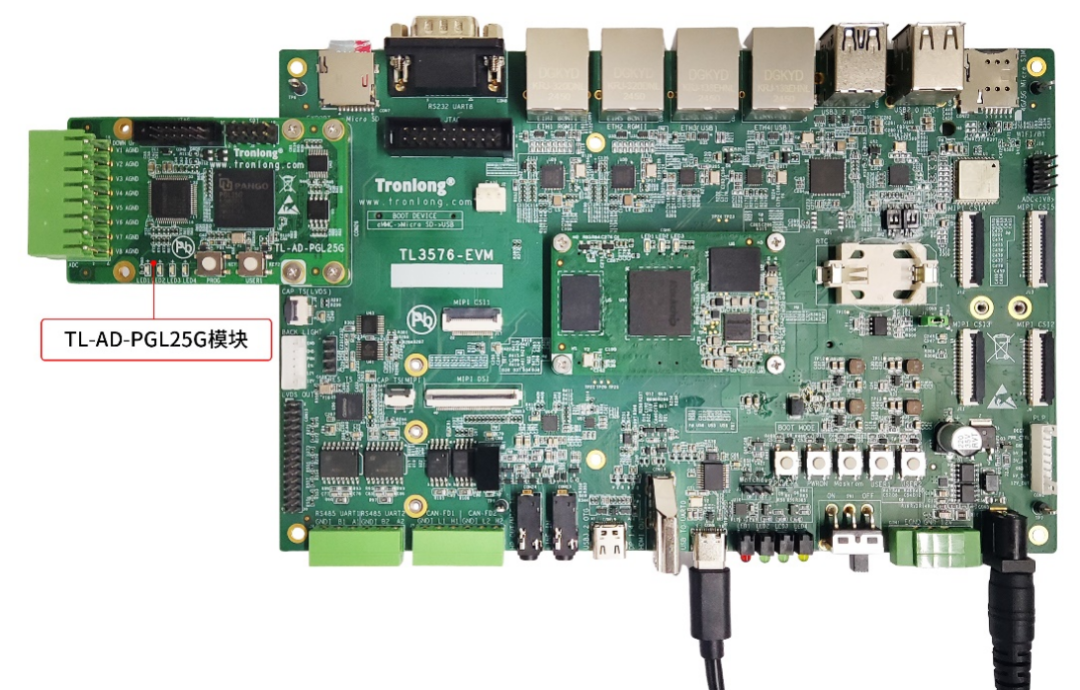

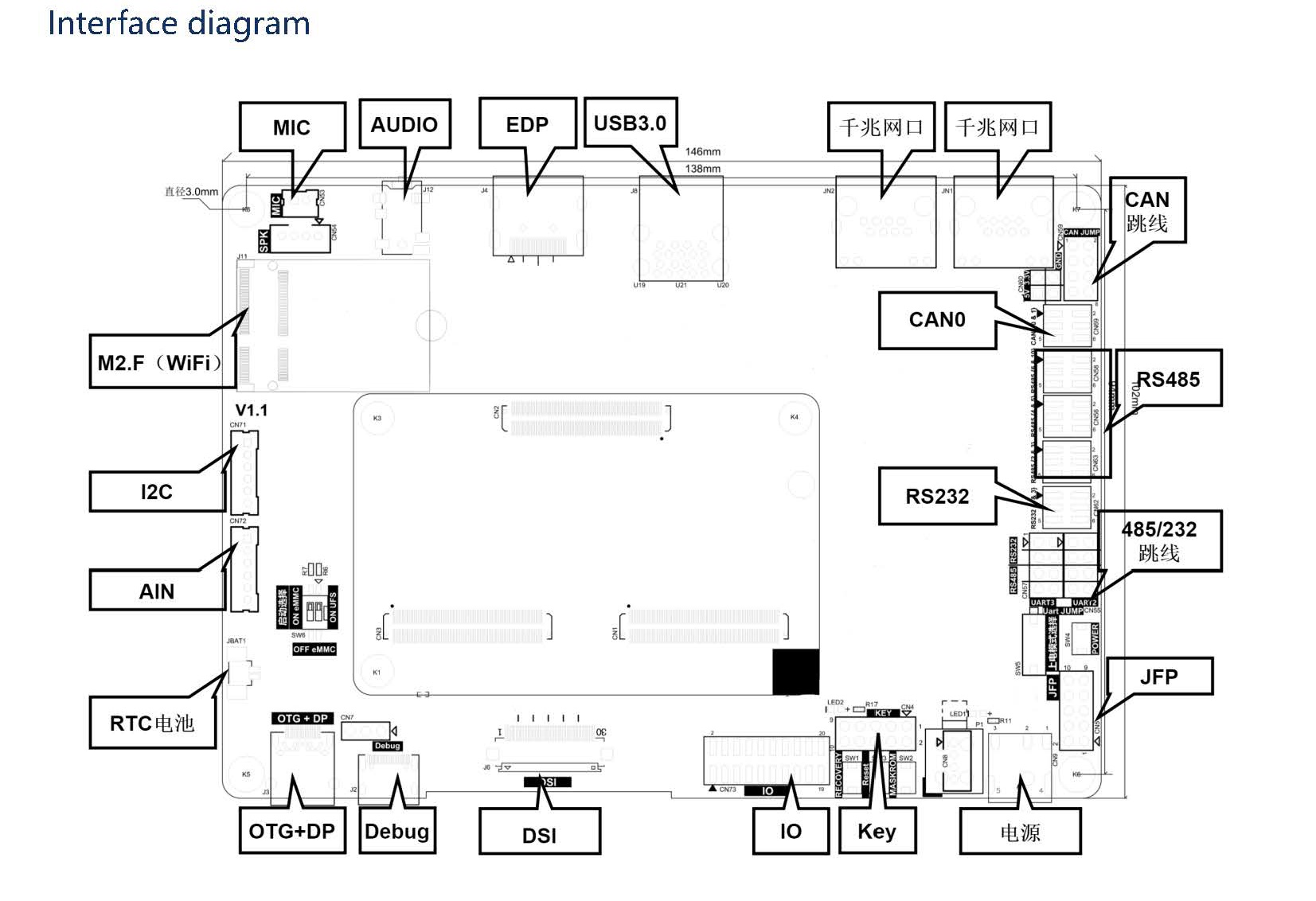

案例演示 請將創龍科技TL-AD-PGL25G模塊連接至評估板EXPORT接口,如下圖所示。

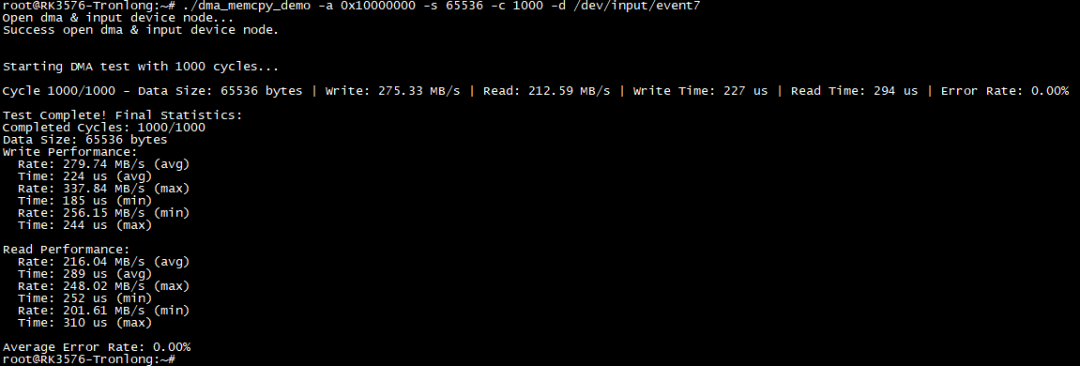

TL-AD-PGL25G模塊連接圖 請參考產品資料用戶手冊完成內核鏡像替換,將FPGA可執行程序固化至SPI FLASH,并加載驅動。 執行如下命令運行程序,ARM通過DSMC總線寫入65536Byte隨機數據至FPGA DRAM,然后讀出數據、進行數據校驗,同時打印DSMC總線讀寫速率和誤碼率,如下圖所示。 Target#./dma_memcpy_demo -a 0x10000000 -s 65536 -c 1000 -d /dev/input/event7

從上圖可知,本次實測平均寫速率約為280MB/s,平均讀速率約為216MB/s,誤碼率為0.00%。

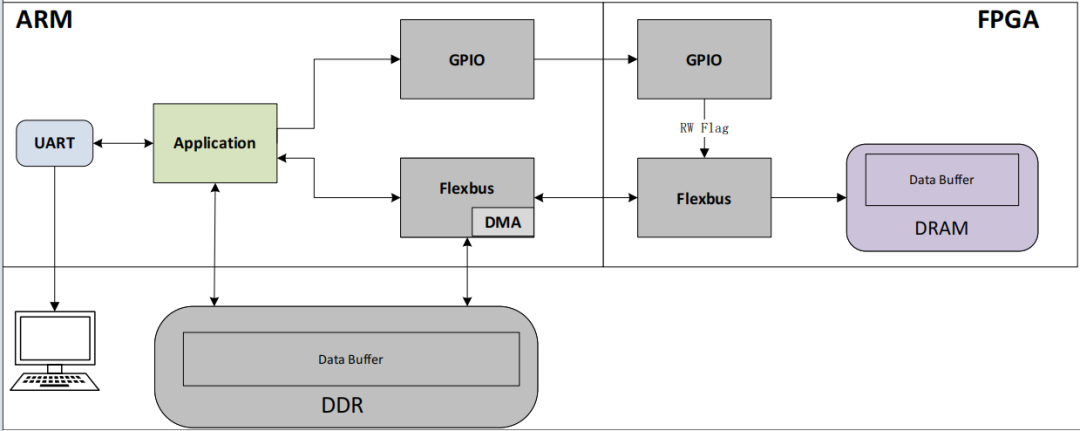

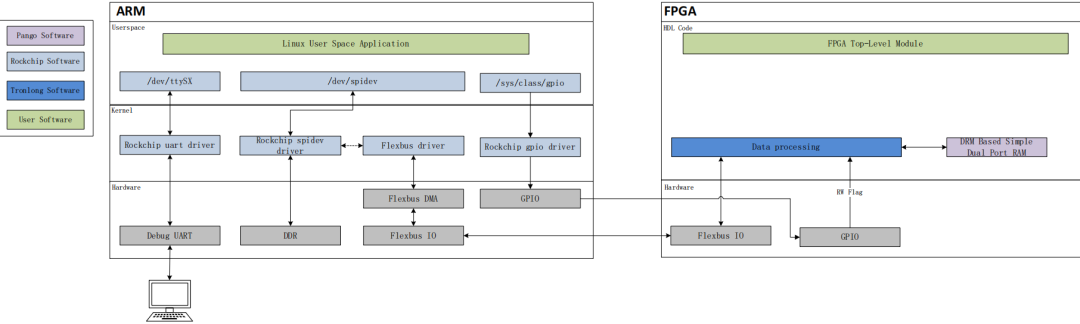

基于FlexBus的ARM與FPGA通信案例 案例說明 案例功能:ARM端運行Linux系統,基于FlexBus總線對FPGA DRAM進行讀寫測試。 程序原理說明如下: ARM端:

通過FlexBus總線對FPGA DRAM進行讀寫測試。

支持通過參數設置數據包大小(每次循環數據包的數據均為新的隨機數)、數據傳輸的循環次數。

對讀寫的數據進行校驗,并打印誤碼率和讀寫速率。

FPGA端:

實現FlexBus Slave功能。

默認將FlexBus Master(ARM)發送的64KByte數據保存到FPGA DRAM。

FlexBus Master(ARM)讀取64KByte數據時,FPGA從DRAM讀取64KByte數據通過FlexBus傳輸給FlexBus Master(ARM)。

案例演示 請將創龍科技TL-AD-PGL25G模塊連接至評估板EXPORT接口,如下圖所示。

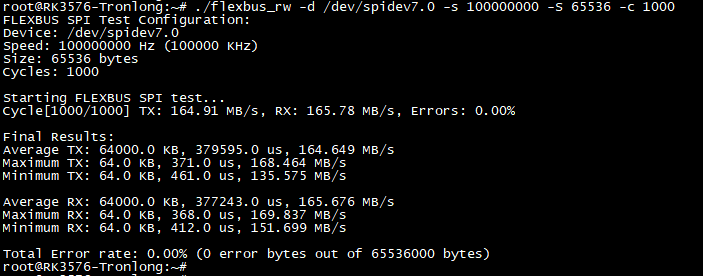

TL-AD-PGL25G模塊連接圖 請參考產品資料用戶手冊完成內核鏡像替換,并將FPGA可執行程序固化至SPI FLASH。 執行如下命令運行程序,ARM通過FlexBus總線寫入65536Byte隨機數據至FPGA DRAM,然后讀出數據、進行數據校驗,同時打印FlexBus總線讀寫速率和誤碼率,如下圖所示。 Target#./flexbus_rw -d /dev/spidev7.0 -s 100000000 -S 65536 -c 1000

從上圖可知,本次實測平均寫速率約為165MB/s,平均讀速率約為166MB/s,誤碼率為0.00%。

-

FPGA

+關注

關注

1643文章

21940瀏覽量

613244 -

并口通信

+關注

關注

0文章

5瀏覽量

2875 -

flexbus

+關注

關注

0文章

2瀏覽量

3060 -

rk3576

+關注

關注

1文章

142瀏覽量

516

原文標題:RK3576 + 紫光同創FPGA并口通信方案

文章出處:【微信號:gh_31fabce82e7f,微信公眾號:紫光同創官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瑞芯微 RK3576S工業評估板規格書

探索 RK3576 方案:卓越性能與靈活框架,誠邀開發定制合作!

米爾RK3576和RK3588怎么選?-看這篇就夠了

【米爾RK3576開發板評測】+項目名稱【米爾RK3576開發板評測】一個視頻和你共同認識一下米爾RK3576開發板

【米爾RK3576開發板評測】帶你初步了解米爾RK3576這塊開發板

RK3588與RK3576區別解析

RK3576單板發布倒計時:RK3399與RK3576對比

國產!瑞芯微RK3576(八核@2.2GHz+6T NPU)工業核心板規格書

國產!瑞芯微RK3576(八核@2.2GHz+6T NPU)工業開發板規格書

新品體驗 | RK3576開發板

RK3576+紫光同創FPGA并口通信方案 基于DSMC/FlexBus并口的RK3576J與FPGA通信方案

RK3576+紫光同創FPGA并口通信方案 基于DSMC/FlexBus并口的RK3576J與FPGA通信方案

評論