SiC MOSFET產(chǎn)業(yè)柵極氧化層可靠性挑戰(zhàn)與破局之路

碳化硅(SiC)MOSFET因其高耐壓、低損耗等特性,在新能源、電動汽車等領(lǐng)域備受關(guān)注。然而,柵極氧化層可靠性問題始終是制約其大規(guī)模應用的核心瓶頸。英飛凌(Infineon)與基本股份(BASiC Semiconductor)作為進口器件與國產(chǎn)器件行業(yè)代表,通過技術(shù)文檔揭示了當前產(chǎn)業(yè)面臨的共性挑戰(zhàn),并提出了各自的解決方案。本文將結(jié)合兩家公司的技術(shù)路徑,探討柵極氧化層可靠性的關(guān)鍵問題及破局方向。

一、柵極氧化層可靠性問題的核心挑戰(zhàn)

材料界面缺陷的先天劣勢

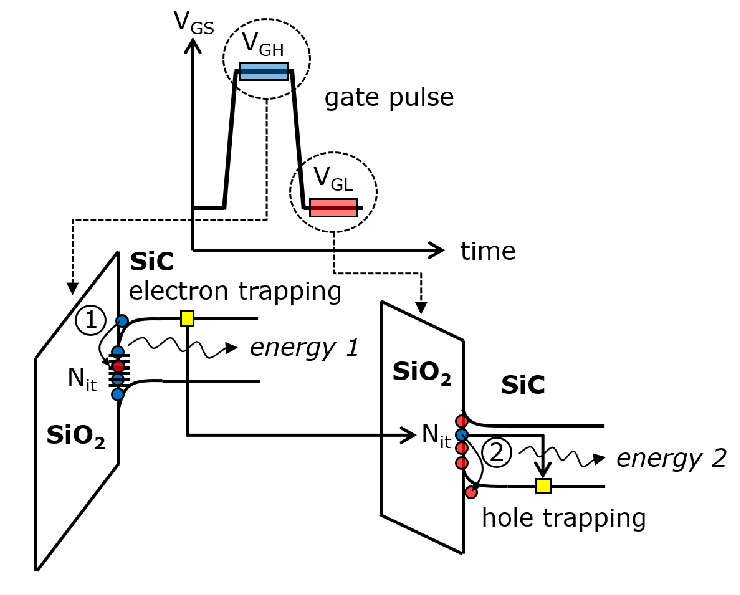

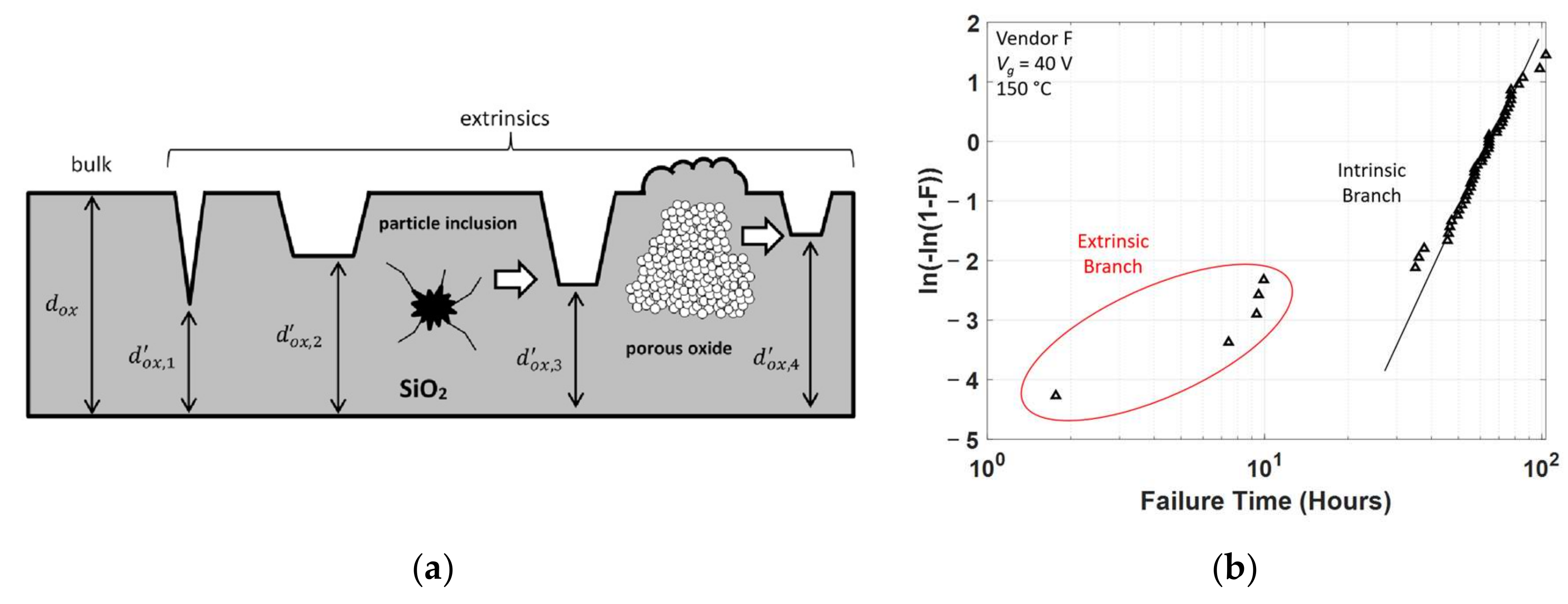

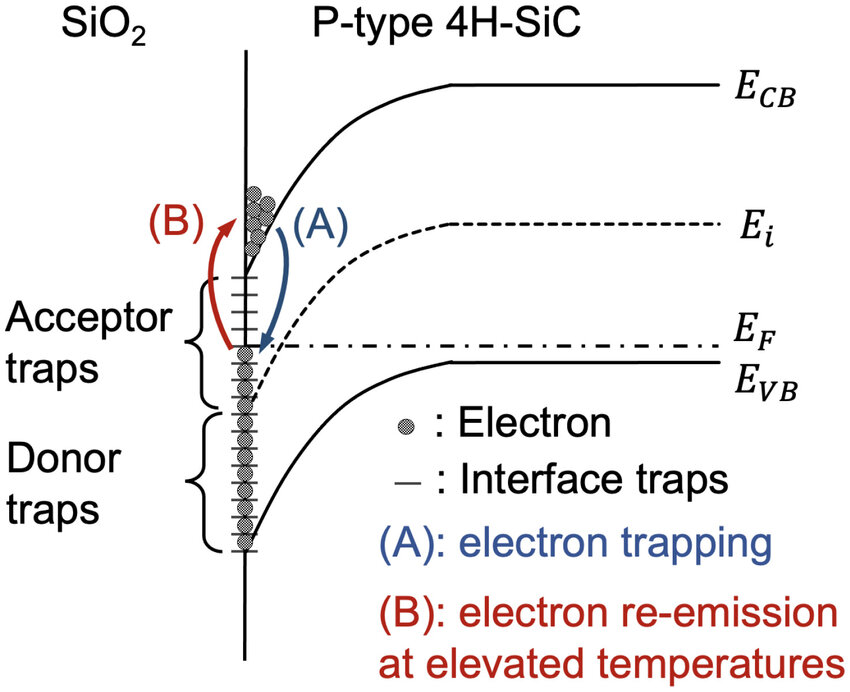

SiC與SiO2界面存在高密度的界面態(tài)和氧化層陷阱,導致電子遷移率降低和局部電場集中。英飛凌指出,SiC柵氧化層的缺陷密度顯著高于硅基器件,易引發(fā)局部擊穿(TDDB)和閾值電壓漂移(HTGB)。基本股份的實驗數(shù)據(jù)顯示,柵極氧化層電場強度超過4 MV/cm時,失效風險急劇上升,而部分競品為追求低導通電阻減薄氧化層,使工作電場遠超安全閾值。

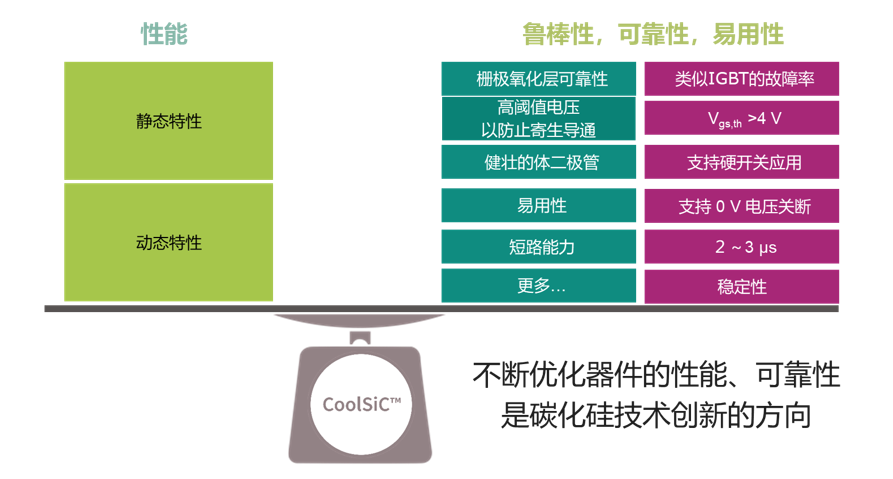

性能與可靠性的權(quán)衡困境

柵極氧化層厚度直接影響導通電阻(RDS(on))和可靠性。英飛凌研究表明,氧化層厚度每增加10 nm,可靠性呈指數(shù)級提升,而導通電阻也線性增加。然而,行業(yè)普遍存在“薄氧化層陷阱”:為降低成本和導通電阻,部分廠商將氧化層減薄至40nm甚至更低,導致器件柵極氧化層壽命大幅縮短。

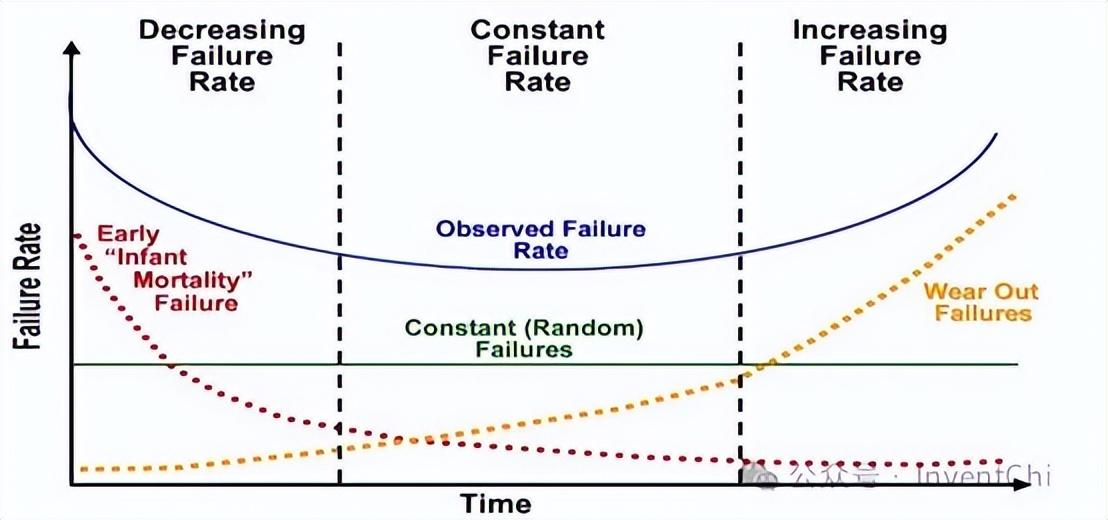

篩選與測試的復雜性

英飛凌通過高電壓篩選剔除缺陷器件,但篩選電壓的設(shè)定需精確平衡臨界電場與氧化層厚度。基本股份的HTGB和TDDB實驗表明,高溫高壓條件下的加速老化測試是驗證可靠性的關(guān)鍵,但測試標準不統(tǒng)一導致行業(yè)數(shù)據(jù)可比性不足,增加了研發(fā)和市場推廣的難度。

二、破局之路:技術(shù)創(chuàng)新與產(chǎn)業(yè)協(xié)同

工藝優(yōu)化與結(jié)構(gòu)創(chuàng)新

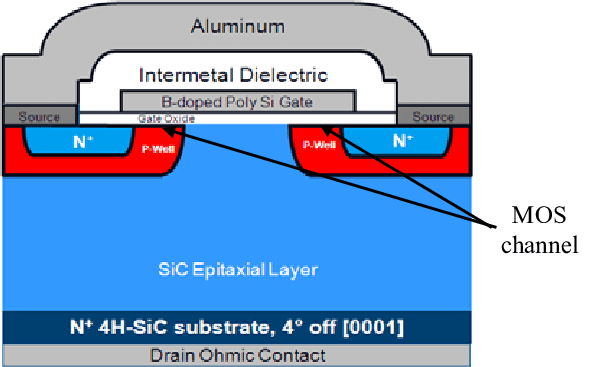

溝槽柵結(jié)構(gòu)突破界面限制:英飛凌采用垂直溝槽柵(Trench MOS)設(shè)計,利用SiC晶面的各向異性,選擇缺陷密度更低的晶面形成柵極界面,顯著降低溝道電阻。即使采用較厚氧化層(與硅基IGBT相當),仍能實現(xiàn)低導通電阻和高可靠性的平衡。

高質(zhì)量氧化層生長技術(shù):基本股份通過嚴格的工藝控制減少界面態(tài)密度,并采用高壓TDDB測試篩選缺陷,確保氧化層均勻性。

可靠性驅(qū)動的設(shè)計理念

厚氧化層策略:英飛凌CoolSiC? MOSFET的柵極氧化層厚度為行業(yè)最厚,通過犧牲少量性能(導通電阻微增)換取可靠性數(shù)量級提升。

全生命周期測試體系:基本股份構(gòu)建了涵蓋HTGB、TDDB、溫度循環(huán)等七大類加速老化實驗的可靠性驗證體系,結(jié)合E模型和1/E模型預測器件壽命,確保實際工況下的可靠性。

標準化與產(chǎn)業(yè)鏈協(xié)同

統(tǒng)一測試標準:推動JEDEC和MIL-STD等標準細化SiC器件可靠性測試方法,明確柵極電場安全閾值(如4 MV/cm)和篩選電壓比例。

上下游技術(shù)協(xié)同:材料供應商需優(yōu)化SiC襯底質(zhì)量,設(shè)備廠商開發(fā)高精度氧化層沉積設(shè)備,共同攻克界面缺陷難題。

三、未來展望:從技術(shù)單點到生態(tài)構(gòu)建

柵極氧化層可靠性問題的解決不僅依賴單一技術(shù)創(chuàng)新,更需要構(gòu)建涵蓋材料、工藝、設(shè)計和測試的完整生態(tài)。英飛凌與基本股份的實踐表明,通過結(jié)構(gòu)優(yōu)化、嚴格測試和長期可靠性驗證,SiC MOSFET的可靠性短板不再是瓶頸。未來,隨著新工藝等新技術(shù)的引入,SiC MOSFET或?qū)⒃诟呖煽啃耘c高性能之間找到更優(yōu)解,推動新能源與電動交通領(lǐng)域的全面升級。

結(jié)語

在SiC MOSFET產(chǎn)業(yè)中,柵極氧化層可靠性既是技術(shù)難點,也是競爭壁壘。唯有堅持長期主義,平衡性能與可靠性,并通過產(chǎn)業(yè)鏈協(xié)同創(chuàng)新,方能突破瓶頸,實現(xiàn)碳化硅技術(shù)的真正普及。

審核編輯 黃宇

-

柵極

+關(guān)注

關(guān)注

1文章

184瀏覽量

21310 -

SiC MOSFET

+關(guān)注

關(guān)注

1文章

84瀏覽量

6468

發(fā)布評論請先 登錄

柵極氧化層在SiC MOSFET設(shè)計中的重要作用

為何必須通過TDDB(時間相關(guān)介質(zhì)擊穿)方法檢驗國產(chǎn)SiC MOSFET的柵氧可靠性水平

提供半導體工藝可靠性測試-WLR晶圓可靠性測試

SiC碳化硅MOSFET驅(qū)動電壓的限制源于柵氧可靠性與器件性能之間的權(quán)衡

麥科信光隔離探頭在碳化硅(SiC)MOSFET動態(tài)測試中的應用

國產(chǎn)SiC碳化硅MOSFET廠商絕口不提柵氧可靠性的根本原因是什么

碳化硅(SiC)MOSFET的柵氧可靠性成為電力電子客戶應用中的核心關(guān)切點

如何測試SiC MOSFET柵氧可靠性

什么是MOSFET柵極氧化層?如何測試SiC碳化硅MOSFET的柵氧可靠性?

瞻芯電子參與編制SiC MOSFET可靠性和動態(tài)開關(guān)測試標準

重磅 9項 SiC MOSFET測試與可靠性標準發(fā)布

瞻芯電子交付碳化硅(SiC)MOSFET逾千萬顆 產(chǎn)品長期可靠性得到驗證

SiC MOSFET產(chǎn)業(yè)柵極氧化層可靠性挑戰(zhàn)與破局之路

SiC MOSFET產(chǎn)業(yè)柵極氧化層可靠性挑戰(zhàn)與破局之路

評論