實現將SC130GS采集的黑白圖像數據緩存進DDR3,并以1024*600@60的視頻時序輸出到LVDS

屏幕顯示。其中,DDR3工作頻率為600MHz,SC130GS輸入的圖像數據大小為1280*1024,幀率為

60幀,數據格式為RAW10。

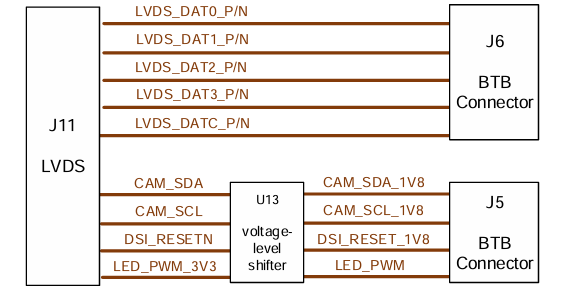

底板提供了一個LVDS顯示接口,采用40P 0.5mm間距的FPC連接 器,包含5對差分信號和6個控制信號,分別為4Data+1Clk和I2C、復 位、中斷、PWM、使能信號。其中I2C、復位和PWM信號由核心板上 FPGA的4個1.8V電平信號通過底板上的雙向電平轉換芯片轉換為3.3V 電平信號后引出到接口上。LVDS接口連接示意圖:

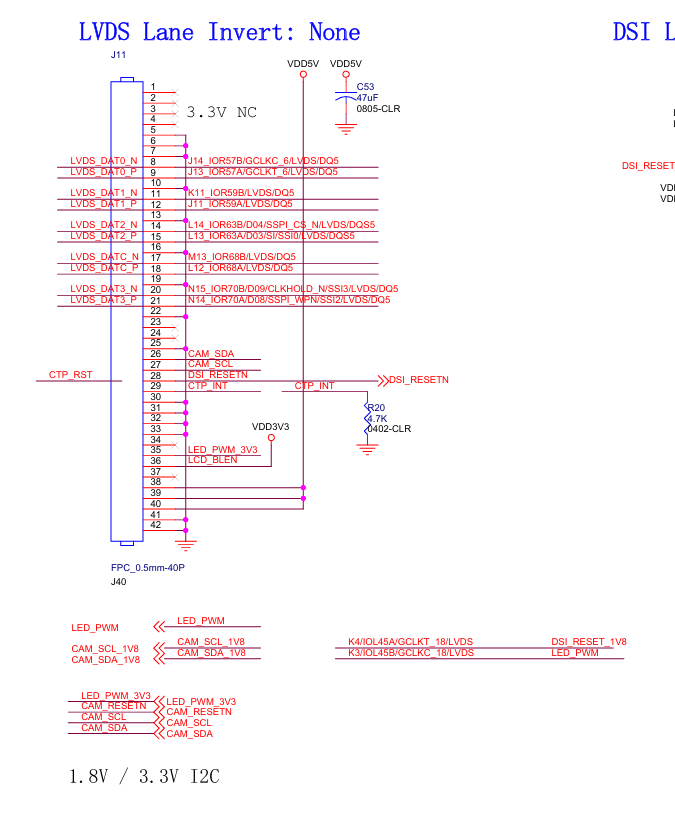

電路原理圖如下:

代碼分析:

//

//Written by GowinSynthesis

//Tool Version "V1.9.10.02"

//Sat Oct 12 14:33:36 2024

//Source file index table:

//file0 "C:/Gowin/Gowin_V1.9.10.02_x64/IDE/ipcore/DDR/data/ddr_138k.v"

`timescale 100 ps/100 ps

module ddio_lvds (

din,

fclk,

pclk,

reset,

q

)

;

input [6:0] din;

input fclk;

input pclk;

input reset;

output [0:0] q;

wire VCC;

wire GND;

OVIDEO ovideo_gen[0].ovideo_inst (

.Q(q[0]),

.D6(din[6]),

.D5(din[5]),

.D4(din[4]),

.D3(din[3]),

.D2(din[2]),

.D1(din[1]),

.D0(din[0]),

.PCLK(pclk),

.FCLK(fclk),

.RESET(reset)

);

VCC VCC_cZ (

.V(VCC)

);

GND GND_cZ (

.G(GND)

);

GSR GSR (

.GSRI(VCC)

);

endmodule /* ddio_lvds */

1. 模塊聲明與端口定義

module ddio_lvds (

din, // 7位輸入數據(寬度6:0,含D0-D6共7位)

fclk, // 高頻時鐘(可能為系統時鐘或DDR時鐘)

pclk, // 并行時鐘(可能用于數據鎖存或同步)

reset, // 復位信號(高電平有效?需結合IP核特性)

q // 1位LVDS輸出(可能為差分信號的正極)

);

-

核心功能:將 7 位并行輸入數據

din轉換為單路 LVDS 格式輸出q,適用于高速串行數據傳輸場景(如視頻信號、DDR 接口等)。 -

命名規則:模塊名

ddio_lvds中,ddio可能指雙數據速率輸入輸出(Dual Data Rate I/O),lvds為低壓差分信號,暗示涉及高速串行通信。

關鍵元件與 IP 核分析

OVIDEO ovideo_gen[0].ovideo_inst (

.Q(q[0]), // 輸出LVDS信號(單端,實際可能需配合差分對)

.D6(din[6]), .D5(din[5]), ..., .D0(din[0]), // 7位輸入數據

.PCLK(pclk), // 并行時鐘(用于鎖存輸入數據)

.FCLK(fclk), // 高頻時鐘(可能用于生成串行時鐘或數據采樣)

.RESET(reset) // 復位信號(控制IP核內部狀態機)

);

-

OVIDEO IP 核功能:

- 通常用于視頻數據的串化(Parallel to Serial)或 LVDS 驅動,可能集成并串轉換、時鐘分頻、預加重等功能。

-

7 位輸入數據

din[6:0]可能對應視頻信號的 RGB565 格式(如 D6-D0 對應 G [5:0] 或類似組合),或自定義協議的并行數據。

-

時鐘關系:

-

pclk為并行數據的同步時鐘,fclk為高頻串行時鐘(通常為pclk的倍數,如 2x、4x 等,用于實現高速串行輸出)。 -

若

fclk是pclk的 8 倍,則可能實現 8b/10b 編碼或類似的串化邏輯。

-

電源與接地元件

VCC VCC_cZ ( .V(VCC) ); // 電源實例化

GND GND_cZ ( .G(GND) ); // 接地實例化

- 顯式實例化電源和地,可能是工具自動生成的模板代碼,確保綜合時電路完整性。

全局置位 / 復位(GSR)

GSR GSR ( .GSRI(VCC) ); // 全局復位使能(高電平有效)

- 用于初始化 FPGA 內部寄存器,確保上電時所有觸發器進入已知狀態,是可綜合設計的常見結構。

信號流向與時序邏輯

din[6:0](并行輸入) → OVIDEO IP核 → 串化處理 → q[0](LVDS單端輸出)

-

IP 核內部可能包含:1、并行數據緩存寄存器(由

pclk驅動);2、串化器(Serializer)將 7 位數據轉換為串行流;3、LVDS 驅動器(如差分緩沖器)生成符合 ANSI-644 標準的信號

時鐘域處理

- fclk和pclk可能屬于不同時鐘域,IP 核內部需處理跨時鐘域(CDC)問題,例如通過 FIFO 或握手信號同步。

-

若fclk是pclk的整數倍,可能通過鎖相環(PLL)生成,確保時鐘同步。

復位邏輯

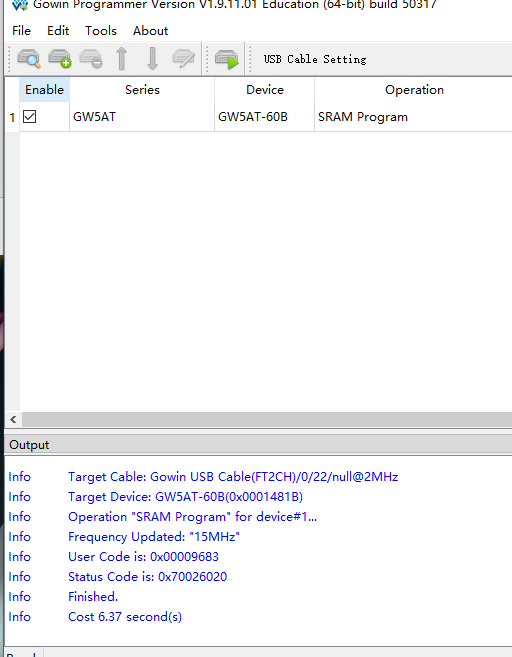

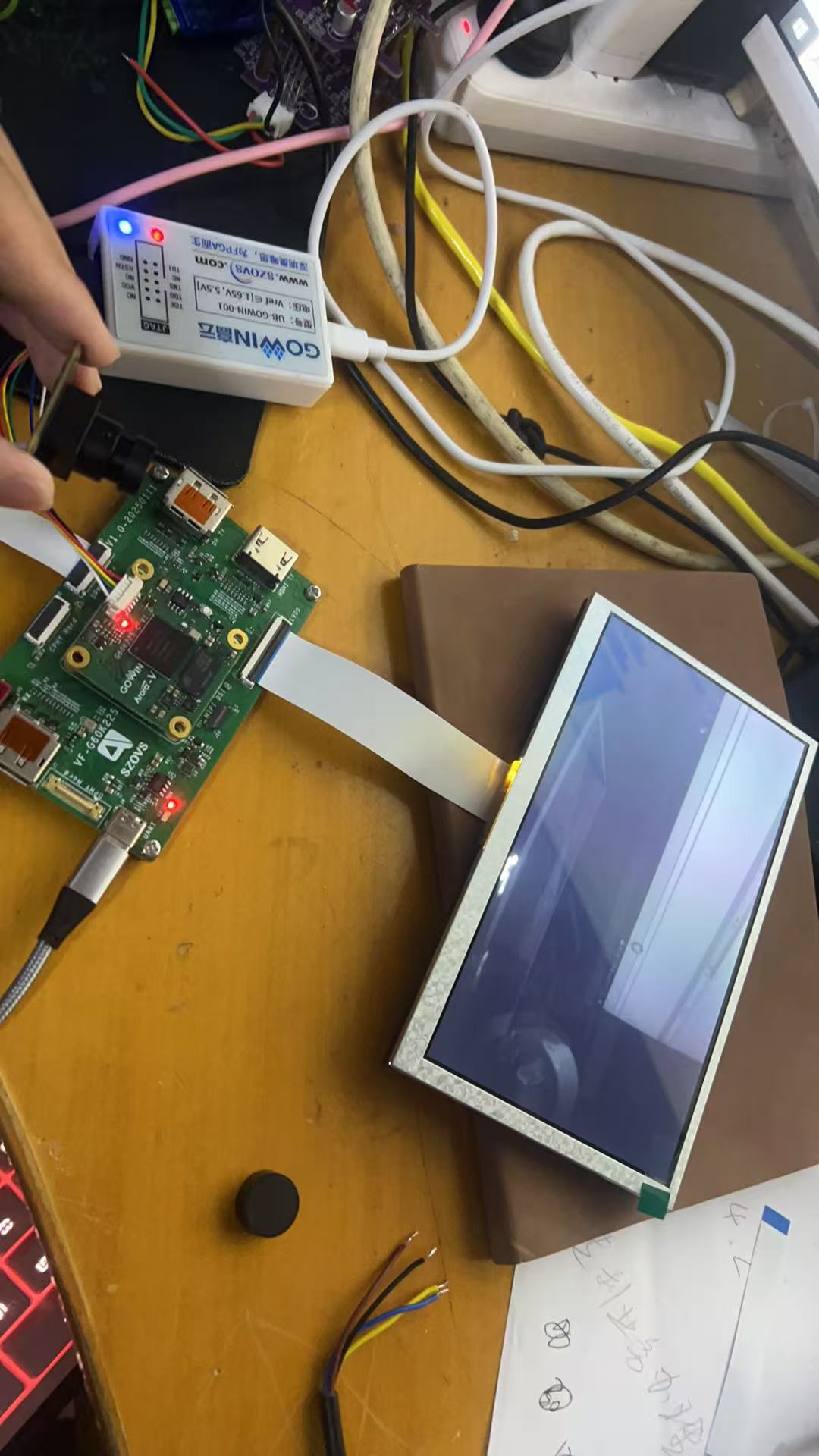

編譯下載固件如下:

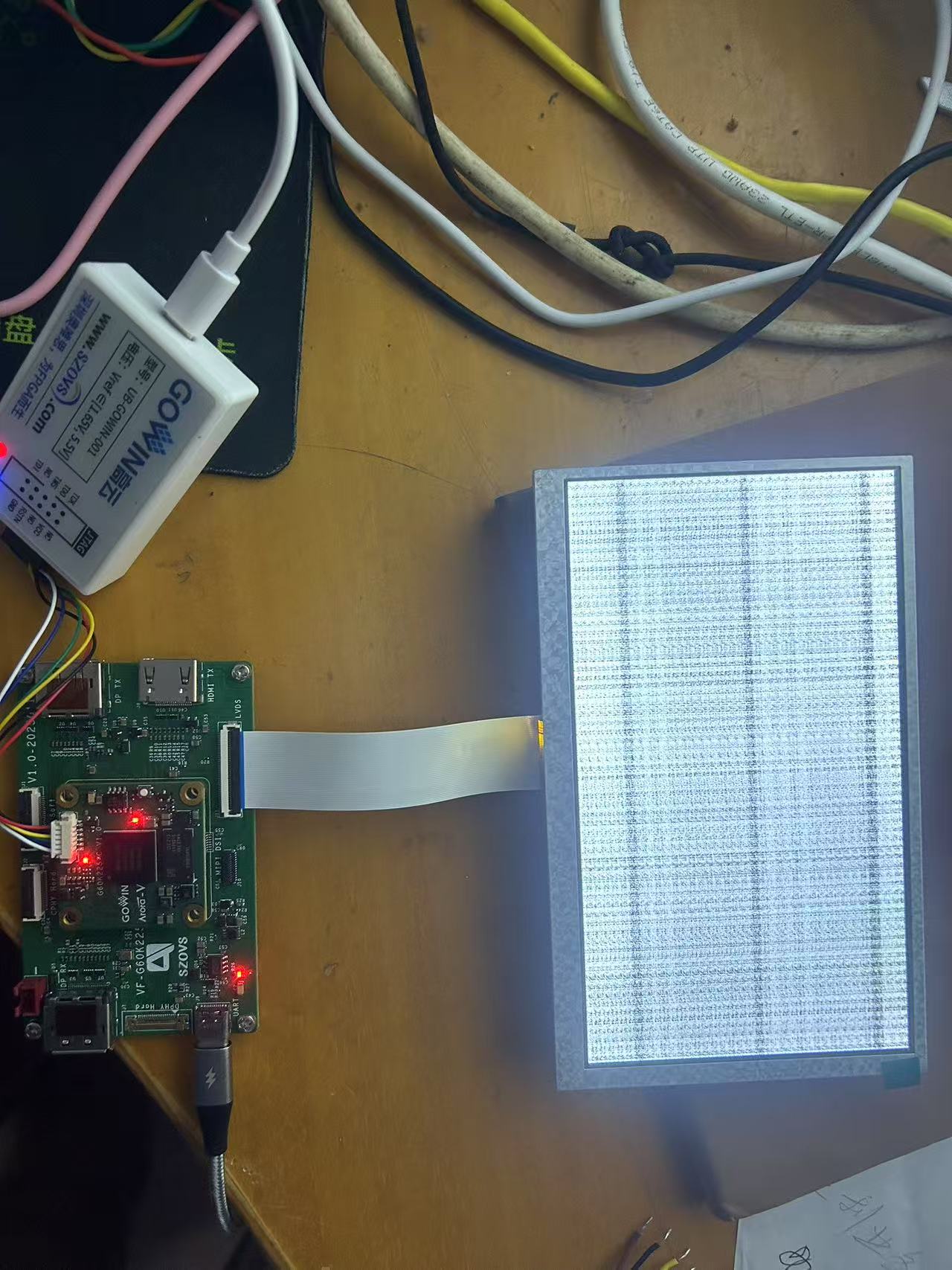

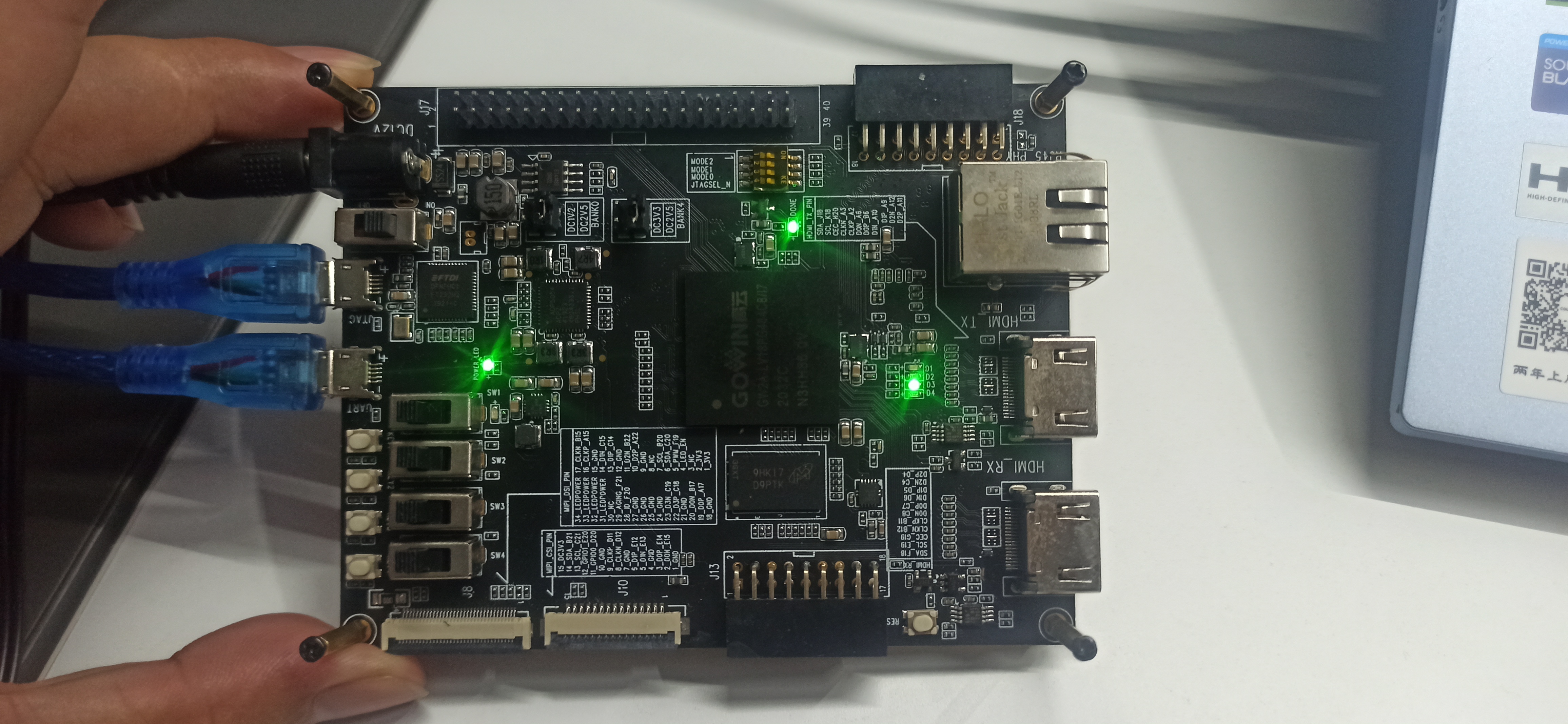

實際效果如下:

實際圖

實際圖 攝像頭數據傳輸到顯示屏

攝像頭數據傳輸到顯示屏潛在應用場景

1. 視頻傳輸系統

- 將 RGB565 格式的 7 位視頻數據(如 G [5:0] + R [0] 或類似組合)轉換為 LVDS 串行流,用于驅動顯示屏或攝像頭接口(如 MIPI D-PHY 的簡化版)。

2. DDR 接口擴展

-

結合

ddio(雙數據速率)特性,可能用于 FPGA 與 DDR 存儲器之間的接口邏輯,實現高速數據讀寫(如 DDR3/DDR4 的控制信號傳輸)。

3. 工業總線通信

設計注意事項

1. LVDS 的差分特性

-

當前代碼僅輸出單端信號

q[0],實際應用中需搭配差分對(如q_p和q_n),可能需修改模塊端口或 IP 核配置。

2. 時鐘頻率匹配

-

需確保

fclk和pclk的頻率關系滿足 IP 核要求(如fclk = 8 * pclk),否則可能導致數據采樣錯誤或串化失敗。

3. 時序約束

- 綜合后需添加時序約束(如時鐘周期、輸入輸出延遲),特別是跨時鐘域路徑,避免出現建立 / 保持時間違規。

4. 復位有效性

-

確認

reset信號的極性(當前代碼未明確,但GSR實例化中GSRI=VCC可能暗示復位信號為高電平有效),需與 IP 核文檔一致。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21985瀏覽量

615097 -

Camera

+關注

關注

0文章

81瀏覽量

21414 -

開發套件

+關注

關注

2文章

171瀏覽量

24620 -

高云半導體

+關注

關注

20文章

136瀏覽量

51022 -

LVDS屏

+關注

關注

0文章

10瀏覽量

1521

發布評論請先 登錄

相關推薦

熱點推薦

【高云GW5AT-LV60 開發套件試用體驗】開箱報告

板套件包括:

DK_VIDEO_GW5AT-LV60UG225_V1.0 核心板

DK_VIDEO_GW5AT-LV60UG225_V1.0 底板

1080*1920 MIPI 液晶屏

發表于 04-29 15:55

【高云GW5AT-LV60 開發套件試用體驗】開箱報告

今天收到高云GW5AT-LV60 FPGA圖像開發套件,拆開看看

很大一個箱子

里面是禮盒包裝,相當豪華。

附包裝清單:

① DK_VIDEO_GW5ATLV60UG225_V1.

發表于 04-30 14:39

【高云GW5AT-LV60 開發套件試用體驗】開箱測評

很榮幸收到高云GW5AT-LV60 FPGA圖像開發板,就來發個開箱帖子吧,首先引入眼簾的就是這個大箱子

采用的是順豐快遞,可以看出高云的誠意滿滿

打開箱子,發現用塑料防護膜包裹著的

發表于 05-04 11:52

【高云GW5AT-LV60 開發套件試用體驗】代碼解讀-點燈實驗

這篇文章解讀一下開發板的第一個demo,這個demo是個點燈demo,通過這個demo可以讓小白了解高云開發的基本過程,所以也是非常重要的,如果之前完全沒用過高云的產品,通過學習這篇文

發表于 05-17 20:23

【高云GW5AT-LV60 開發套件試用體驗】開箱及IDE與開發板基礎功能測評

本帖最后由 jf_88521721 于 2025-5-18 12:34 編輯

一、硬件配置與開箱體驗

高云GW5AT-LV60開發套件以“全場景圖像處理”為核心定位,包裝內包含核

發表于 05-18 12:11

【高云GW5AT-LV60 開發套件試用體驗】代碼解讀-LVDS屏幕驅動

今天我們繼續來學習高云開發板的代碼,我們拿著開發板自然是要開發的,所以看代碼是非常重要的,何況這種FPGA開發板上面沒啥外設的,基本上都是接

發表于 05-31 23:01

【高云GW5AT-LV60 開發套件試用體驗】SC130GScmos模塊與LVDS屏和HDMI輸出例程測試報告

Route Option:1

固化程序啟動速度設置:35MHz

LVDS屏顯示SC130cmos圖像效果如下:

cmos數據位mipi接口,通過lvds物理差分對將圖像數據化傳

發表于 06-08 23:35

【高云GW5AT-LV60 開發套件試用體驗】SC130GScmos模塊與LVDS屏和HDMI輸出例程測試報告圖像顯示部分細節補充

:03-2_G60_HDMI_Display_1080P60、04_G60_LVDS_Display_1024x600,重新設計輸出圖像,得到新的圖像顯示畫面:

ok,回到cmos顯示

發表于 06-09 09:46

【RISC-V專題】高云半導體Combat開發套件首發試用

Combat開發套件是以高云半導體 GW2A 系列 FPGA 產品為核心,是高云半導體晨熙?家族第一代產品, 內部資源豐富,具有高性能的DSP 資源,高速

發表于 04-15 13:55

【高云半導體Combat開發套件試用體驗】基礎測評GPIO+串口測評

本文來源電子發燒友社區,作者:mameng, 帖子地址: https://bbs.elecfans.com/jishu_2291163_1_1.html Combat開發套件是以高云半導體 GW

【新品發布】高云Arora-V 60K FPGA圖像開發板

2024年上,高云半導體發布了最新22nm先進工藝的60K高性能FPGA: Arora-V:GW5AT-LV60 高云的Arora Ⅴ系列的GW5A

發表于 02-18 17:34

?595次閱讀

高云Arora Ⅴ系列GW5AT-LV60 FPGA:晨熙?家族高性能新星

高云半導體推出的Arora Ⅴ系列GW5AT-LV60 FPGA,作為晨熙?家族的第5代杰出產品,憑借其內部資源的豐富性與創新架構,成功吸引了業界的廣泛關注。 GW5AT-LV60 F

基于高云Arora-V 60K FPGA實現的MIPI CPHY轉MIPI DPHY透傳模塊

近期,高云代理商聯詮國際聯合合作伙伴DepEye(深目微)共同推出 MIPI CPHY轉DPHY (C2D)透傳模塊:DEGC2DV60,功能基于高云GW5AT-LV60 FPGA實現

發表于 04-22 17:51

?244次閱讀

【高云GW5AT-LV60 開發套件試用體驗】 LVDS屏顯示和camera

【高云GW5AT-LV60 開發套件試用體驗】 LVDS屏顯示和camera

評論