在高頻電路設(shè)計(jì)中,理想元件的假設(shè)往往成為制約性能的「隱形枷鎖」。當(dāng)信號(hào)頻率突破MHz級(jí)門檻時(shí),電阻與電容的寄生參數(shù)(如引線電感、分布電容)開始主導(dǎo)電路行為,導(dǎo)致阻抗特性偏離理論模型。本文將深度解析這些「非理想特性」的物理機(jī)制、量化影響及應(yīng)對(duì)策略。

一、寄生參數(shù)的物理根源:從「理想模型」到「現(xiàn)實(shí)枷鎖」

電阻的寄生雙生:引線電感與分布電容

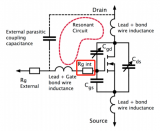

電阻的物理結(jié)構(gòu)中,引線長(zhǎng)度與導(dǎo)體截面積直接決定寄生參數(shù)的強(qiáng)度。以0603封裝貼片電阻為例,其引線電感典型值為0.5nH,當(dāng)頻率超過(guò)100MHz時(shí),該電感與電阻本體(1kΩ)形成的并聯(lián)諧振點(diǎn)將導(dǎo)致阻抗驟降。更隱蔽的分布電容源于電阻體與引線間的電場(chǎng)耦合,典型值為0.1~0.5pF,在GHz頻段會(huì)形成額外的容性通路。

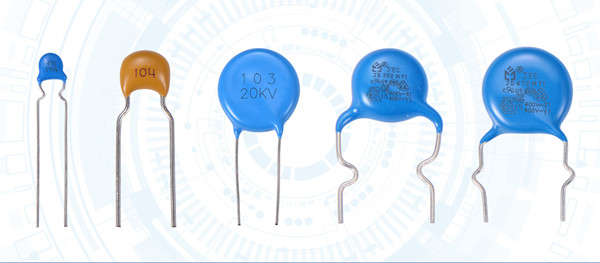

電容的寄生三重奏:ESR、ESL與介質(zhì)損耗

電容的高頻等效電路包含三個(gè)關(guān)鍵寄生參數(shù):

等效串聯(lián)電阻(ESR):由電極材料(如銀漿)的電阻率與引線電阻共同決定,典型值為幾毫歐至幾十毫歐。在開關(guān)電源的輸出濾波電容中,ESR會(huì)引發(fā)電壓紋波,需選用低ESR的聚合物電容(如POSCAP)。

等效串聯(lián)電感(ESL):由引線長(zhǎng)度與封裝結(jié)構(gòu)決定,0402封裝陶瓷電容的ESL約為0.5nH。當(dāng)信號(hào)頻率超過(guò)自諧振頻率(SRF)時(shí),電容將呈現(xiàn)感性,導(dǎo)致濾波失效。

介質(zhì)損耗:由電介質(zhì)材料的介電損耗角正切(tanδ)表征,X7R陶瓷電容的tanδ在1MHz時(shí)約為0.02,在GHz頻段會(huì)顯著增加,引發(fā)發(fā)熱與信號(hào)衰減。

二、寄生參數(shù)的量化影響:從「微小擾動(dòng)」到「性能崩塌」

電阻的頻響畸變:阻抗曲線中的「死亡谷」

在100MHz~1GHz頻段,電阻的阻抗曲線呈現(xiàn)典型的「雙峰」特征:

第一諧振點(diǎn):由引線電感與分布電容的并聯(lián)諧振引發(fā),導(dǎo)致阻抗急劇上升。例如,1kΩ電阻在500MHz時(shí)可能呈現(xiàn)10kΩ的諧振峰值。

第二諧振點(diǎn):由電阻體本身的電感與電容諧振引發(fā),導(dǎo)致阻抗再次下降。這種非單調(diào)特性使得電阻在高頻時(shí)無(wú)法作為穩(wěn)定的負(fù)載或分壓元件。

電容的SRF陷阱:從「濾波神器」到「噪聲放大器」

電容的自諧振頻率(SRF)是其高頻性能的分水嶺。以10μF鉭電解電容為例,其SRF約為100kHz,在MHz級(jí)頻段已完全失效。而0.1μF陶瓷電容的SRF可達(dá)100MHz,但在GHz頻段仍會(huì)因ESL效應(yīng)呈現(xiàn)感性。更致命的是,電容的寄生參數(shù)會(huì)引發(fā)「反諧振」現(xiàn)象:當(dāng)多個(gè)電容并聯(lián)時(shí),其阻抗曲線可能在特定頻段形成尖峰,導(dǎo)致EMI超標(biāo)。

三、寄生參數(shù)的應(yīng)對(duì)策略:從「被動(dòng)妥協(xié)」到「主動(dòng)駕馭」

電阻的「瘦身術(shù)」:結(jié)構(gòu)優(yōu)化與材料革新

薄膜電阻:采用濺射工藝制備的鎳鉻合金薄膜,可將寄生電容降低至0.05pF以下,適用于GHz級(jí)電路。

無(wú)感繞線電阻:通過(guò)雙線并繞技術(shù)消除電感,但僅適用于50kHz以下頻段。

金屬箔電阻:利用康銅箔的趨膚效應(yīng)優(yōu)化高頻特性,寄生電容可控制在0.02pF以內(nèi)。

電容的「頻率馴化」:拓?fù)鋬?yōu)化與材料升級(jí)

反向電容布局:將高頻去耦電容靠近芯片電源引腳,縮短電流回路,降低ESL。例如,在CPU供電電路中,0.1μF電容需與電源平面通過(guò)多個(gè)過(guò)孔連接。

三維集成電容:采用硅通孔(TSV)技術(shù)實(shí)現(xiàn)的嵌入式電容,可將ESL降低至0.1nH以下,適用于10GHz以上頻段。

寬頻帶匹配:通過(guò)串聯(lián)小電容(如1pF)與并聯(lián)大電容(如10μF)的組合,擴(kuò)展濾波帶寬。例如,在射頻電路中,常采用「π型濾波器」實(shí)現(xiàn)DC~6GHz的寬頻帶抑制。

四、寄生參數(shù)的測(cè)試與建模:從「黑箱摸索」到「精準(zhǔn)預(yù)測(cè)」

測(cè)試技術(shù):從LCR表到矢網(wǎng)分析

時(shí)域反射法(TDR):通過(guò)測(cè)量反射系數(shù)計(jì)算寄生參數(shù),適用于PCB走線的寄生電感提取。

阻抗分析儀:在1MHz~3GHz頻段內(nèi)掃描電容的阻抗曲線,直接獲取SRF與ESR。

去嵌入技術(shù):利用S參數(shù)測(cè)量與仿真模型迭代,消除測(cè)試夾具的影響。

建模方法:從集總參數(shù)到分布參數(shù)

RLC梯形網(wǎng)絡(luò):將電阻或電容的寄生參數(shù)等效為串聯(lián)/并聯(lián)的RLC網(wǎng)絡(luò),適用于100MHz以下頻段。

傳輸線模型:當(dāng)元件尺寸超過(guò)信號(hào)波長(zhǎng)的1/10時(shí),需采用分布式參數(shù)模型。例如,在毫米波電路中,電容的引線需建模為微帶線。

電磁仿真:通過(guò)HFSS或CST軟件進(jìn)行全波仿真,考慮導(dǎo)體趨膚效應(yīng)與介質(zhì)損耗。

結(jié)語(yǔ):在非理想中尋找理想

高頻電路的寄生參數(shù)陷阱,本質(zhì)上是物理定律與工程實(shí)踐的永恒博弈。電阻的寄生電感與電容的ESL,如同「達(dá)摩克利斯之劍」,時(shí)刻威脅著信號(hào)完整性。但通過(guò)結(jié)構(gòu)優(yōu)化(如薄膜電阻)、材料革新(如低ESR電容)與建模技術(shù)(如傳輸線模型),工程師可將非理想特性的影響控制在可接受范圍內(nèi)。正如量子力學(xué)揭示的「測(cè)不準(zhǔn)原理」,電子工程師需學(xué)會(huì)在不確定中構(gòu)建確定性——這或許正是高頻設(shè)計(jì)的終極魅力。

審核編輯 黃宇

-

觸摸屏

+關(guān)注

關(guān)注

42文章

2380瀏覽量

118251 -

電容電阻

+關(guān)注

關(guān)注

0文章

18瀏覽量

6832

發(fā)布評(píng)論請(qǐng)先 登錄

村田貼片電容的高頻特性與阻抗匹配

【干貨分享】電源功率器件篇:變壓器寄生電容對(duì)高壓充電機(jī)輸出功率影響

工業(yè)機(jī)器人協(xié)作場(chǎng)景中的聚徽電容觸控交互方案:安全急停與精準(zhǔn)操控的雙重保障

LCR測(cè)試儀中LP(Parallel)與LS(Series)模式的區(qū)別

村田電容高頻特性解析:技術(shù)優(yōu)勢(shì)與應(yīng)用突破

如何選擇適合高頻電路的貼片電容?

一文詳解寄生參數(shù)對(duì)柵極震蕩的影響

寄生參數(shù)陷阱:聚徽解碼高頻電路中電容電阻的「非理想特性」

寄生參數(shù)陷阱:聚徽解碼高頻電路中電容電阻的「非理想特性」

評(píng)論