隨著數據中心高密度計算需求的增長,服務器電源向高功率密度、高效率方向發展,而磁性元器件產品作為電源的核心部件,其設計直接影響系統性能與可靠性。

南京博蘭得電子科技有限公司研發高級經理劉建在近日的中國磁性元器件產業鏈峰會上,以《15kW 服務器電源磁性元器件優化》為主題,分享了團隊在磁性元器件設計中如何平衡多重約束的實戰經驗。

博蘭得研發高級經理劉建

一、背景:解碼15kW服務器電源的規格挑戰

電源規格:輸入覆蓋 342-528Vac 寬電壓范圍,采用液冷散熱方案,輸出需達到 48V/313A(15kW),15 毫秒掉電保持時間,過流保護(OCP)點為額定電流的 130%~140%。

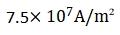

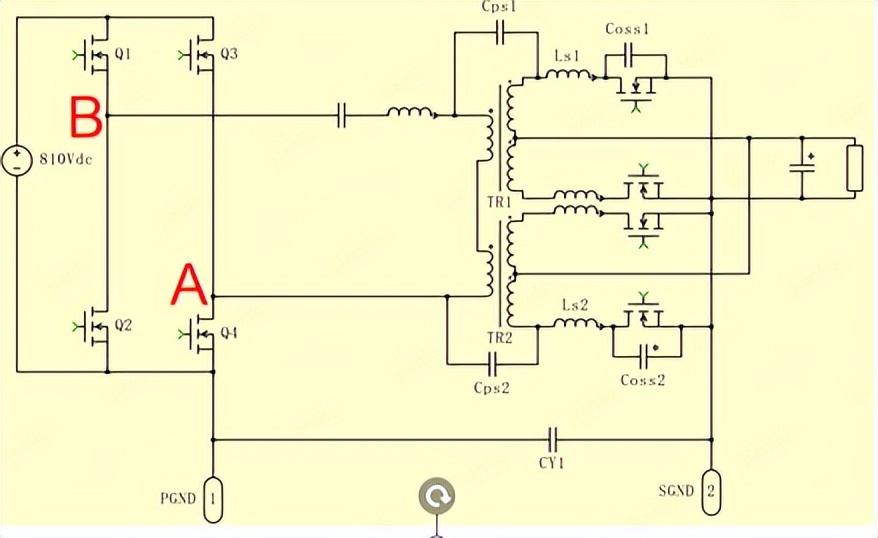

從服務器電源的系統框圖來看,前級采用 Vienna 結構,后級為三路全橋 LLC 并聯的電路拓撲組合,原副邊均由 DSP 控制。每路LLC的磁性元器件產品通過原邊串聯、副邊并聯實現 15kW 總功率,這種磁性元器件設計對集成度、散熱效率和電磁兼容性(EMC)提出了更高的要求。

二、LLC 磁性元器件設計優化:從磁芯到繞組的全流程分析

1.磁性元器件設計之匝比優化

磁性元器件匝比確定主要基于三點原則:一是原邊采用 1200V SiC MOSFET,盡量提高母線(BUS)電壓以降低原邊電流;二是在滿足電壓降額的前提下提高 BUS 電壓,減少 BUS 電容數量以滿足保持時間要求;三是原邊串聯、副邊并聯,等效原邊總匝數需為偶數。

最終選擇總匝比 34:2(單磁性元器件產品匝比 17:2),選擇BUS 電壓為810V,增益計算為 17×48/810=1.0074,額定工況下 LLC 工作點接近 100kHz 諧振頻率。

2.磁芯結構優化

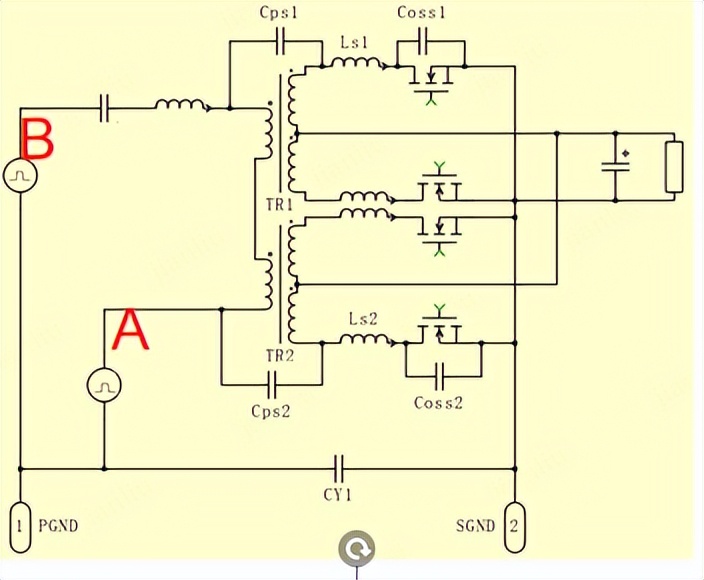

15kW 電源的 DCDC 部分由三路 5kW 全橋 LLC 組成,原設計每路 LLC 采用兩個 EI 磁性元器件(原邊串聯、副邊并聯),但 6 個磁性元器件體積過大,無法滿足空間要求。

團隊提出 “磁通抵消” 設計,將兩個磁性元器件磁芯整合:第一個磁性元器件繞組電流逆時針,磁通向外;第二個磁性元器件繞組電流順時針,磁通向內,邊柱合并后磁通相互抵消,兩個磁性元器件磁芯可以集成為一個磁芯,磁芯體積減少 30% 以上。

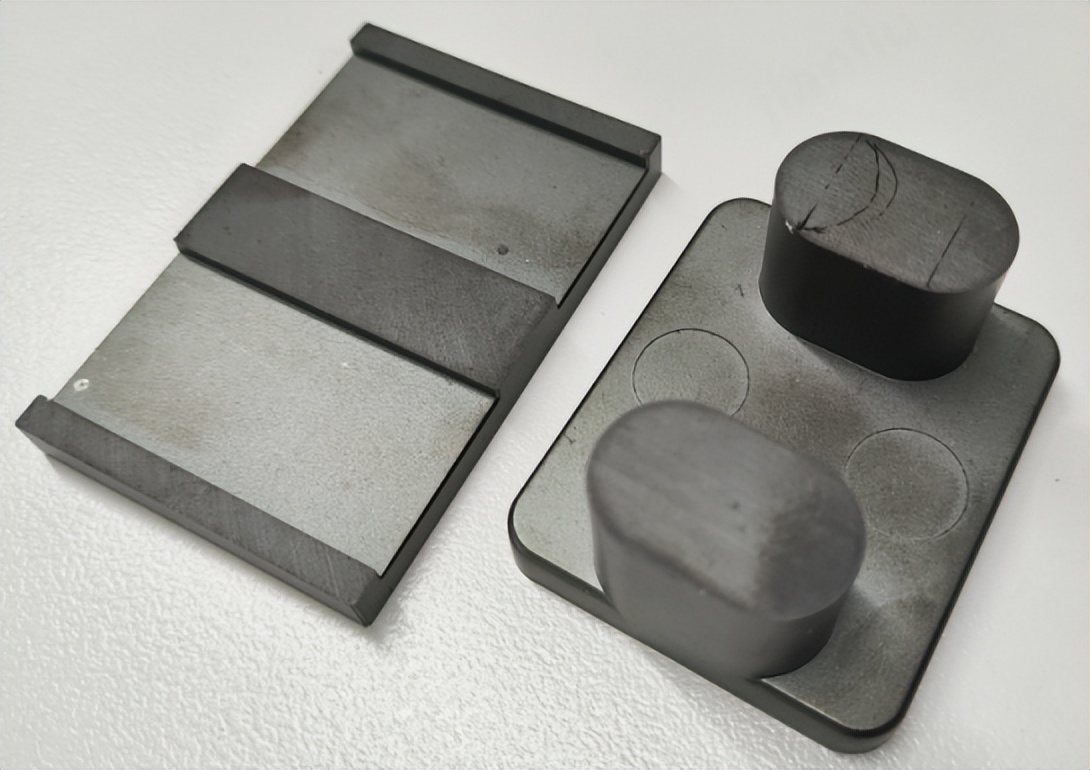

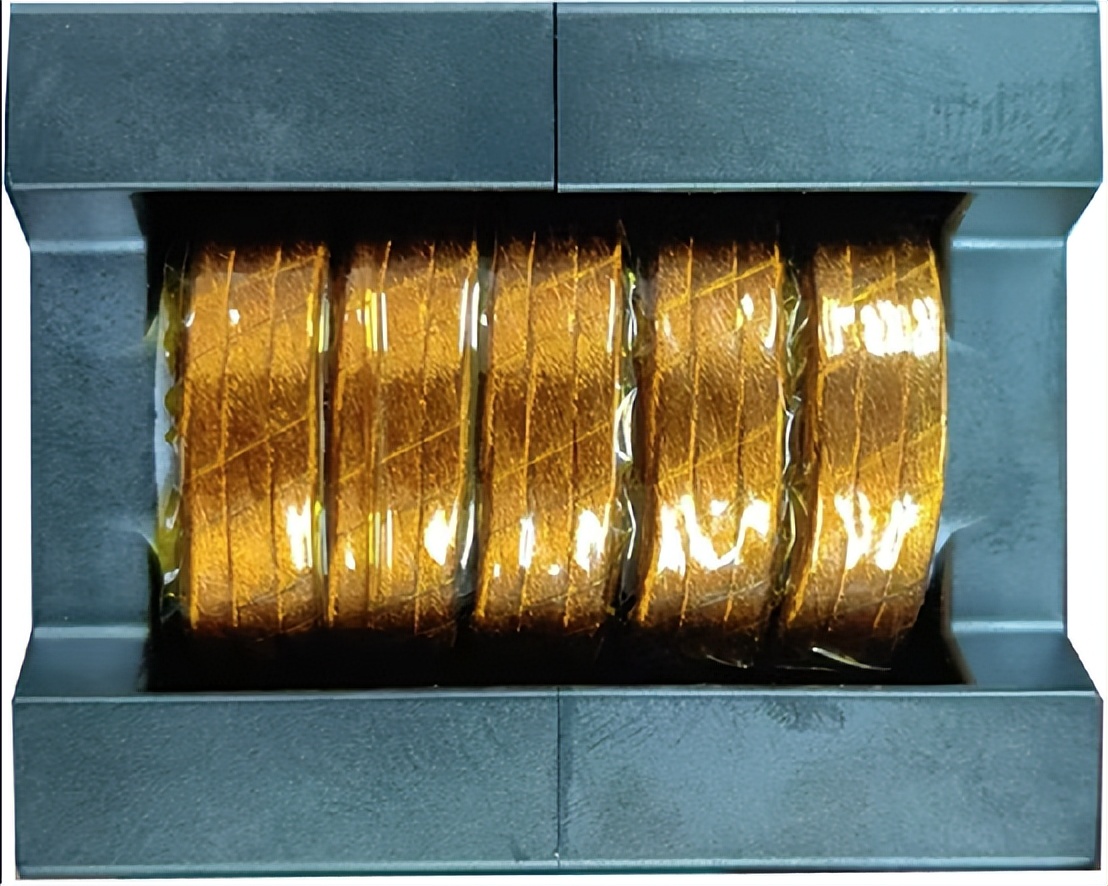

優化后的磁芯

3.磁性元器件繞組損耗優化

磁性元器件損耗主要分為銅損和鐵損,由于諧振頻率,匝數以及layout已經確定,鐵損基本上只能靠材料來進行優化,所以主要考慮鐵損的優化。

疊層結構對比:

磁性元器件產品采用無骨架(Bobbinless)繞法,原邊每柱 17 匝(100 股直徑 0.1mm 三層絕緣線),分為 9 匝和 8 匝兩個線圈;副邊 S1、S2 為 2 匝寬 8.5mm 扁平線。

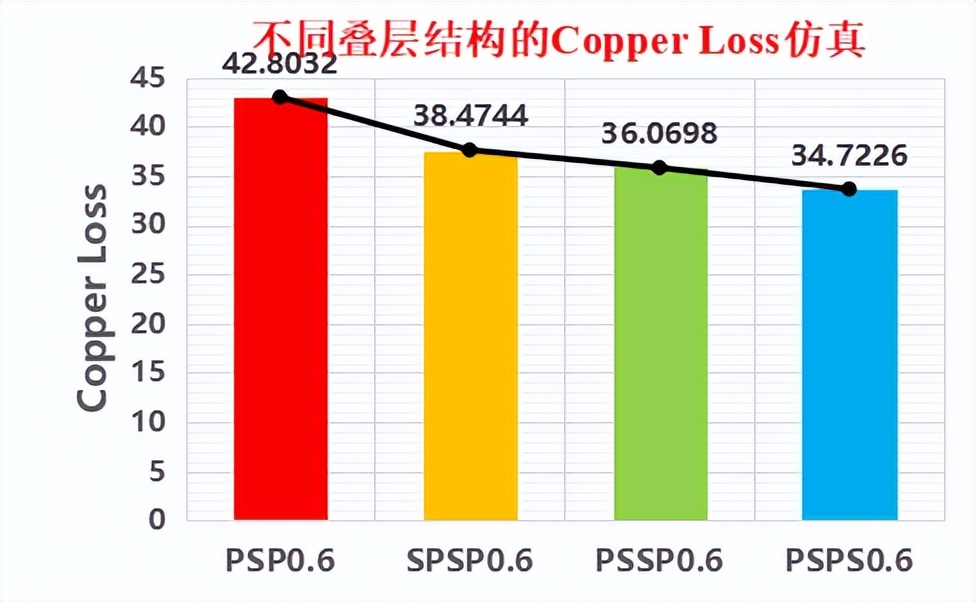

針對四種疊層結構(PSP、SPSP、PSSP、PSPS),團隊放棄了傳統的 “試錯法”,利用 Maxwell 2D 仿真分析磁動勢(MMF)與損耗:

從仿真結果看,PSPS的比PSP損耗減少8.1W,實測減少12.5W。SPSP 結構因副邊靠近氣隙,邊緣效應(Fringing Effect)導致額外損耗。

根據一般經驗,PSSP比較好,然而根據相關文獻,PSSP和PSPS在頻率變化時,損耗有個交叉點,低頻PSSP較好,高頻PSPS占優,在本項目中,PSPS較好。

2.厚度敏感分析

副邊波形為脈動直流,近似半正弦波,可分解為交流分量(有效值 0.386)和直流分量(有效值0.318),交流分量占主導,因此重點優化交流損耗(集膚效應與鄰近效應)。

繞組的損耗可以分解成 DC損耗和 AC 損耗,DC 損耗僅與繞組厚度相關,AC損耗則是集膚效應和鄰近效應產生的損耗之和。研究發現,副邊繞組的電流密度沿厚度方向劇烈變化,可見電流在厚度方向上嚴重分布不均是交流損耗較大的原因。

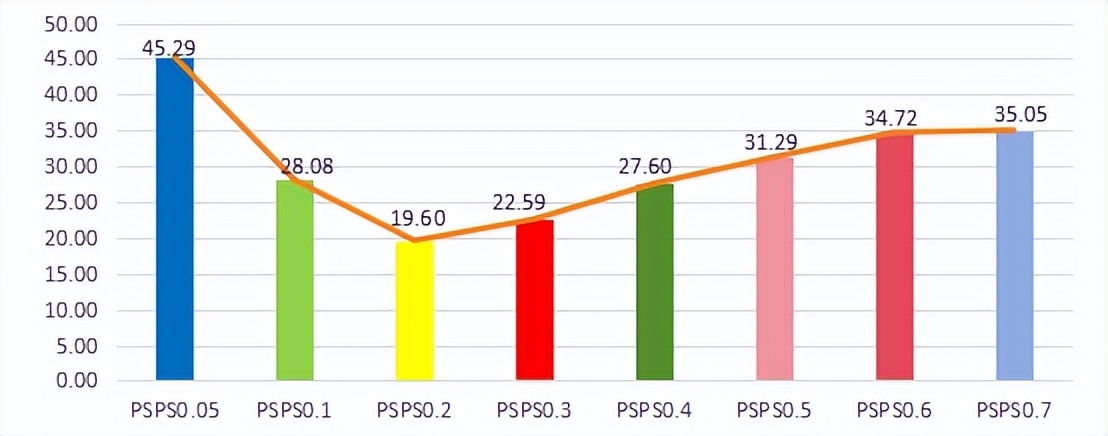

通過仿真不同厚度(0.05-0.7mm)的銅損發現,厚度 0.2mm 時總損耗為19.6W,因集膚效應損耗(隨厚度先降后升)與鄰近效應損耗(隨厚度先升后降)達到平衡。厚度增加到0.5mm后,損耗變化已經變得比較緩慢。

然而,理論優解0.2mm 厚度的難以生產,考慮到可生產性,最終選擇 0.3mm厚度的繞組,實測損耗仍比0.6mm 降低 15W。這一折中設計體現了工程思維對理論的修正。

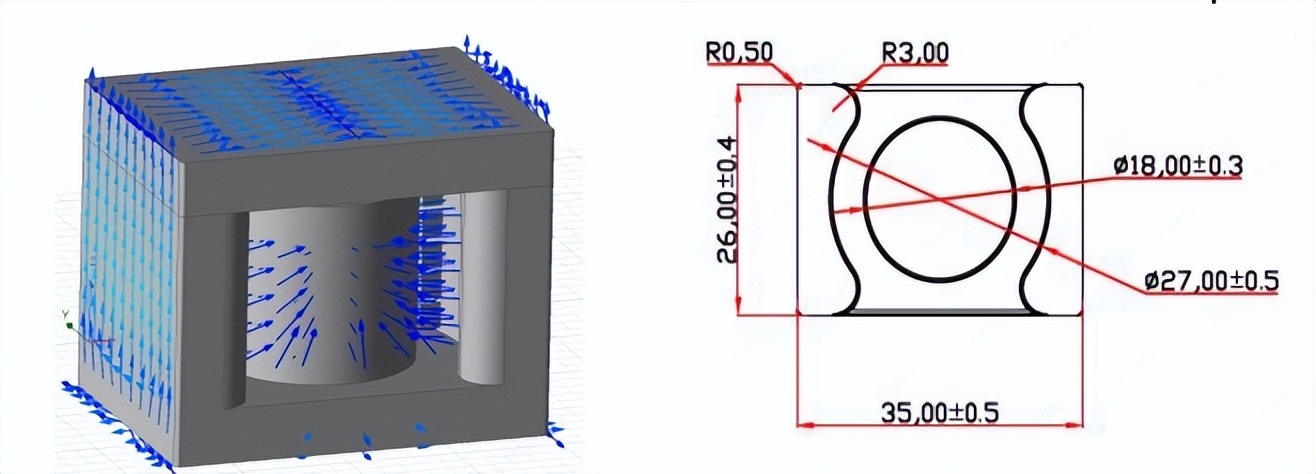

進一步通過電流密度分析,0.6mm 厚度在 90°相位時電流密度峰值達

而0.3mm僅為

驗證了厚度對交流損耗的決定性影響。

磁性元器件產品優化最終方案為PSPS疊層,副邊繞組銅厚0.3mm,實現單個磁性元器件產品損耗降低27.64W。

4.寄生電容抑制

PSPS 結構雖降低損耗,但原副邊寄生電容(實測 C1=63pF,C2=52pF)引發兩大問題:一是EMI 問題,原邊諧振電流出現高頻振蕩。二是電壓尖峰:副邊 SR MOSFET 的 DS 電壓在軟啟時出現 150V以上的尖峰(超過 150V 額定應力)。

通過等效電路分析,博蘭得研發團隊發現A 點回路因缺少電感(磁性元器件產品),成為這些問題的主因。為此,該團隊創新提出在 A 點串聯電感(與B回路的電感集成),通過增加回路阻抗抑制振蕩,無需RC吸收電路。實測顯示,滿載啟機時 DS 電壓尖峰降至 134V,諧振電流的高頻振蕩被抑制。

諧振電感優化

諧振電感采用 EQI35 磁芯(中柱氣隙 1.8mm),初始設計為 0.15×75 利茲線 10 匝,仿真發現fringing effect不明顯,但繞組損耗較大,為4.67W。經研究發現其原因為邊柱與中柱間距 4.5mm,而電感的氣隙為1.8mm,兩者具有可比性,遠離氣隙的地方有比較大的磁通直接從邊柱到中柱,氣隙附近的磁通減少。磁通直接切割了遠離氣隙的繞組,造成了較大的AC 損耗。

為了驗證上面的分析,做了如下仿真:中柱Ae減少,氣隙不變,匝數增加到15匝,保持電感量接近,進行仿真結果為繞組損耗為3.63W,驗證了上面的分析。

隨后,團隊通過以下調整破解難題:一是采用 0.1×120 利茲線(股數增加,單股直徑減小),降低集膚效應深度(100kHz 時銅的集膚深度 0.066mm,0.1mm 線徑)。二是將繞組遠離氣隙邊緣,邊緣效應損耗降低35%。最終使總損耗從 4.60W 降至 2.37W。

三、PFC 磁性元器件優化

在 342Vac 輸入、冷卻液溫度 45°C 時,電源運行 30 分鐘后關機,博蘭得研發團隊經磁芯溫升測試與仿真分析發現:共模電感磁芯(T63×38×25,TS10 材質)溫度升至 110°C,此時 Bsat 從室溫 0.3T 降至 0.18T,而滿載時磁密峰值達 0.2T,超過高溫下的Bsat,導致磁芯瞬間飽和電感量驟降(從 5mH 降至 數uH),PFC控制異常觸發保護。

三相共模電感并繞

傳統集中繞制時,漏感較大造成共模電感在流過大電流時飽和。于是博蘭得團隊仿真了如下結構:共模電感的三個繞組,每個繞組拆分為兩部分,按 A1-B1-C1-A2-B2-C2 順序交替繞制。仿真結果顯示,磁密峰值降至 0.1T。最終選取了三線并繞的方法進行繞制。

四、總結:仿真驅動設計的價值與工程啟示

本次磁性元器件產品優化的啟示在于仿真工具的深度應用。團隊對比了 3D 仿真與 2D 簡化模型的工程價值,在對稱結構中,2D 仿真速度更快,且誤差較小。

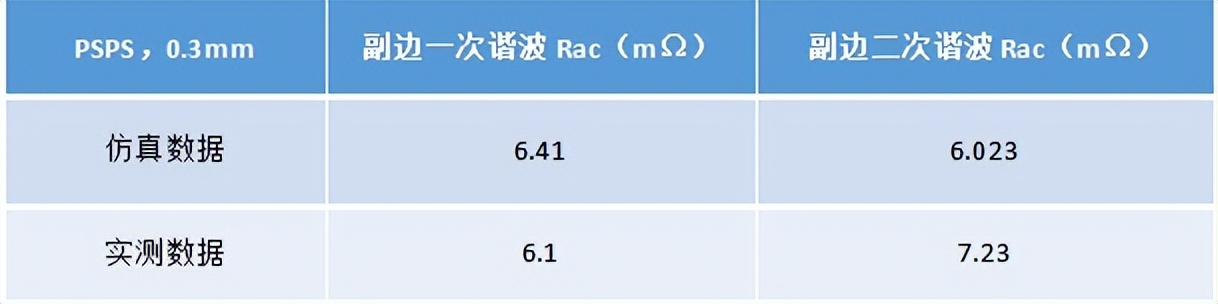

博蘭得的實踐揭示了高功率密度電源設計的三大核心法則:如副邊繞組的Rac仿真值與實際測量值的對比,結果相差不大,仿真具有參考意義,成為當下產品迭代的核心工具。在大功率及高功率密度場合,磁性元器件設計優化是難點之一。僅靠實驗來指導設計,可能會事倍功半;但借助仿真來指導設計,則會事半功倍。

系統級優化思維:磁性元器件設計需從單一器件視角轉向電源系統視角,例如匝比選擇需聯動 MOSFET 選型與BUS電容設計;

仿真驅動研發:在 SiC/GaN 等寬禁帶器件普及的今天,寄生參數的影響已無法通過經驗公式覆蓋,必須依賴精確建模;

工藝協同創新:從 Bobbinless 繞法到三線并列結構,磁性元器件設計創新必須與工藝能力深度綁定,避免理論方案的工程不可行。

五、結語

博蘭得團隊通過電磁理論創新、仿真工具突破與工藝細節打磨的三重協同,不僅實現了單個電源模塊的性能躍升,更勾勒出高功率密度電源研發的新范式 —— 以仿真為驅動力,將磁性元器件設計轉化為 "可計算、可預測、可迭代" 的工程科學。這在為數據中心電源的下一代技術突破(如 20kW 級產品)奠定基礎,推動磁性元器件與電源行業向更高效率、更緊湊體積、更低成本的目標邁進。

本文為嗶哥嗶特資訊原創文章,未經允許和授權,不得轉載

審核編輯 黃宇

-

服務器電源

+關注

關注

1文章

32瀏覽量

9757 -

磁性元器件

+關注

關注

0文章

134瀏覽量

14506

發布評論請先 登錄

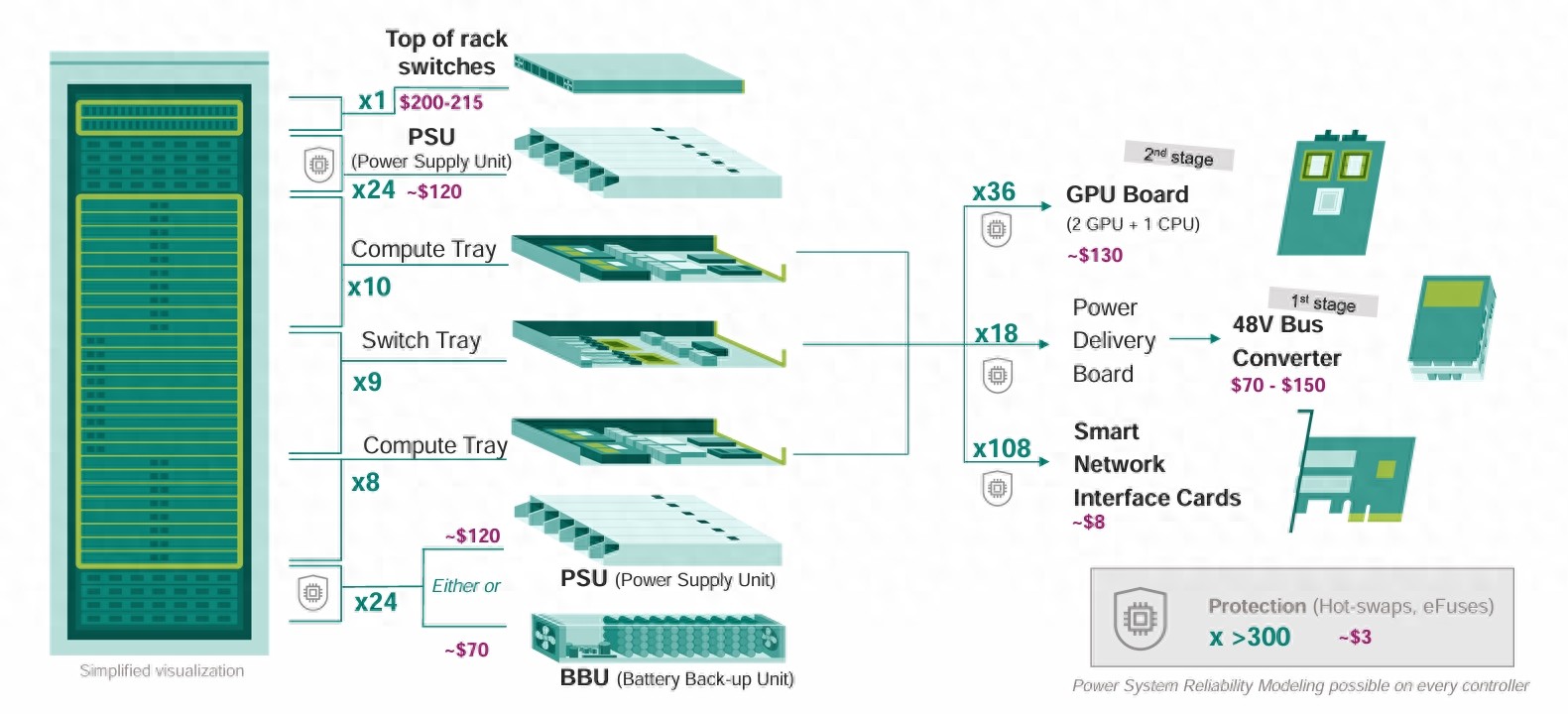

一臺AI服務器電源系統如何吃掉$15,000的半導體器件?

AI服務器電源技術研討會部分演講嘉賓確認

AI 服務器電源如何迭代升級?

峰值效率98%,納微12kW AI數據中心服務器電源,支持英偉達Backwell GPU

RakSmart服務器成本優化策略

薩瑞微電子SiC 和 GaN賦能AI服務器電源系統

15kW服務器電源 如何優化磁性元器件?

15kW服務器電源 如何優化磁性元器件?

評論