FPGA即現(xiàn)場(chǎng)可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點(diǎn)。本文主要介紹的是FPGA開(kāi)發(fā)流程及VHDL基本語(yǔ)法,具體的跟隨小編來(lái)了解一下。

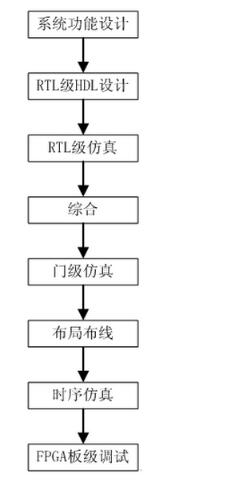

FPGA開(kāi)發(fā)流程詳解

1) 系統(tǒng)功能設(shè)計(jì)

在系統(tǒng)設(shè)計(jì)之前,首先要進(jìn)行的是方案論證、系統(tǒng)設(shè)計(jì)和FPGA芯片選擇等準(zhǔn)備工作。

一般都采用自頂向下的設(shè)計(jì)方法,把系統(tǒng)分成若干個(gè)基本單元,然后再把每個(gè)基本單元?jiǎng)澐譃橄乱粚哟蔚幕締卧?/p>

2) RTL級(jí)HDL設(shè)計(jì)

RTL級(jí)(Register Transfer Level,寄存器傳輸級(jí))指不關(guān)注寄存器和組合邏輯的細(xì)節(jié)(如使用了多少個(gè)邏輯門、邏輯門的連接拓?fù)浣Y(jié)構(gòu)等),通過(guò)描述數(shù)據(jù)在寄存器之間的流動(dòng)和如何處理、控制這些數(shù)據(jù)流動(dòng)的模型的HDL設(shè)計(jì)方法。

RTL級(jí)比門級(jí)更抽象,同時(shí)也更簡(jiǎn)單和高效。RTL級(jí)的最大特點(diǎn)是可以直接用綜合工具將其綜合成為門級(jí)網(wǎng)表,其中RTL級(jí)設(shè)計(jì)直接決定著系統(tǒng)的功能和效率。

3) RTL級(jí)仿真

也稱為功能(行為)仿真,或是綜合前仿真,是在編譯之前對(duì)用戶所設(shè)計(jì)的電路進(jìn)行邏輯功能驗(yàn)證,此時(shí)的仿真沒(méi)有延遲信息,僅對(duì)初步的功能進(jìn)行檢測(cè)。

仿真前,要先利用波形編輯器和HDL等建立波形文件和測(cè)試向量(即將所關(guān)心的輸入信號(hào)組合成序列),仿真結(jié)果將會(huì)生成報(bào)告文件和輸出信號(hào)波形,從中觀察各個(gè)節(jié)點(diǎn)信號(hào)的變化。雖然仿真是非必需步驟,但卻是系統(tǒng)設(shè)計(jì)中最關(guān)鍵的一步。為了提高功能仿真的效率,需要建立測(cè)試平臺(tái)testbench,其測(cè)試激勵(lì)一般使用行為級(jí)HDL語(yǔ)言描述。

4) 綜合

所謂綜合就是將較高級(jí)抽象層次的描述轉(zhuǎn)化成較低層次的描述。綜合優(yōu)化根據(jù)目標(biāo)與要求優(yōu)化所生成的邏輯連接,使層次設(shè)計(jì)平面化,供FPGA布局布線軟件進(jìn)行實(shí)現(xiàn)。

就目前的層次來(lái)看,綜合優(yōu)化(Synthesis)是指將設(shè)計(jì)輸入編譯成由與門、或門、非門、RAM、觸發(fā)器等基本邏輯單元組成的邏輯連接網(wǎng)表,而并非真實(shí)的門級(jí)電路。

真實(shí)具體的門級(jí)電路需要利用FPGA制造商的布局布線功能,根據(jù)綜合后生成的標(biāo)準(zhǔn)門級(jí)結(jié)構(gòu)網(wǎng)表來(lái)產(chǎn)生。

5) 門級(jí)仿真

也稱為綜合后仿真,綜合后仿真檢查綜合結(jié)果是否和原設(shè)計(jì)一致。

在仿真時(shí),把綜合生成的標(biāo)準(zhǔn)延時(shí)文件反標(biāo)注到綜合仿真模型中去,可估計(jì)門延時(shí)帶來(lái)的影響。但這一步驟不能估計(jì)線延時(shí),因此和布線后的實(shí)際情況還有一定的差距,并不十分準(zhǔn)確。目前的綜合工具較為成熟,對(duì)于一般的設(shè)計(jì)可以省略這一步,但如果在布局布線后發(fā)現(xiàn)電路結(jié)構(gòu)和設(shè)計(jì)意圖不符,則需要回溯到綜合后仿真來(lái)確認(rèn)問(wèn)題之所在。

6) 布局布線

實(shí)現(xiàn)是將綜合生成的邏輯網(wǎng)表配置到具體的FPGA芯片上,將工程的邏輯和時(shí)序與器件的可用資源匹配。布局布線是其中最重要的過(guò)程,布局將邏輯網(wǎng)表中的硬件原語(yǔ)和底層單元合理地配置到芯片內(nèi)部的固有硬件結(jié)構(gòu)上,并且往往需要在速度最優(yōu)和面積最優(yōu)之間作出選擇。布線根據(jù)布局的拓?fù)浣Y(jié)構(gòu),利用芯片內(nèi)部的各種連線資源,合理正確地連接各個(gè)元件。也可以簡(jiǎn)單地將布局布線理解為對(duì)FPGA內(nèi)部查找表和寄存器資源的合理配置,布局可以被理解挑選可實(shí)現(xiàn)設(shè)計(jì)網(wǎng)表的最優(yōu)的資源組合,而布線就是將這些查找表和寄存器資源以最優(yōu)方式連接起來(lái)。

目前,F(xiàn)PGA的結(jié)構(gòu)非常復(fù)雜,特別是在有時(shí)序約束條件時(shí),需要利用時(shí)序驅(qū)動(dòng)的引擎進(jìn)行布局布線。布線結(jié)束后,軟件工具會(huì)自動(dòng)生成報(bào)告,提供有關(guān)設(shè)計(jì)中各部分資源的使用情況。由于只有FPGA芯片生產(chǎn)商對(duì)芯片結(jié)構(gòu)最為了解,所以布局布線必須選擇芯片開(kāi)發(fā)商提供的工具。

7) 時(shí)序仿真

是指將布局布線的延時(shí)信息反標(biāo)注到設(shè)計(jì)網(wǎng)表中來(lái)檢測(cè)有無(wú)時(shí)序違規(guī)(即不滿足時(shí)序約束條件或器件固有的時(shí)序規(guī)則,如建立時(shí)間、保持時(shí)間等)現(xiàn)象。時(shí)序仿真包含的延遲信息最全,也最精確,能較好地反映芯片的實(shí)際工作情況。由于不同芯片的內(nèi)部延時(shí)不一樣,不同的布局布線方案也給延時(shí)帶來(lái)不同的影響。因此在布局布線后,通過(guò)對(duì)系統(tǒng)和各個(gè)模塊進(jìn)行時(shí)序仿真,分析其時(shí)序關(guān)系,估計(jì)系統(tǒng)性能,以及檢查和消除競(jìng)爭(zhēng)冒險(xiǎn)是非常有必要的。

8) FPGA板級(jí)調(diào)試

通過(guò)編程器將布局布線后的配置文件下載至FPGA中,對(duì)其硬件進(jìn)行編程。配置文件一般為.pof或.sof文件格式,下載的方式包括AS(主動(dòng))、PS(被動(dòng))、JTAG(邊界掃描)等方式。

VHDL基本語(yǔ)法詳解

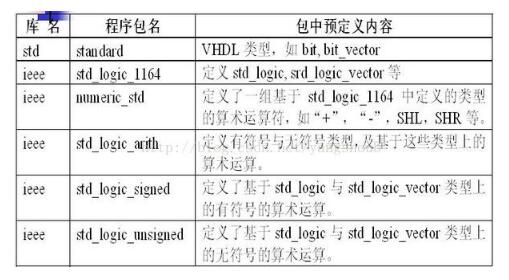

1、引用庫(kù)

library IEEE; //表示打開(kāi)IEEE庫(kù),因?yàn)镮EEE庫(kù)不屬于VHDL的標(biāo)準(zhǔn)庫(kù),所以使用庫(kù)的內(nèi)容要先聲明

use ieee.numeric_std.all; //USE和ALL是關(guān)鍵詞,表示允許使用IEEE庫(kù)中numeric_std程序包中的所有內(nèi)容,這個(gè)程序包主要是用來(lái)做數(shù)據(jù)類型轉(zhuǎn)換

use ieee.std_logic_unsigned.all;

use ieee.std_logic_misc.all;

use ieee.std_logic_1164.all;

library UNISIM; //UNISIM是xilinx的庫(kù)函數(shù),為了仿真使用。Using this declaration, the simulator references the functional models for all device primitives. In addition to this declaration, you must compile the library and map the library to the simulator.

use UNISIM.VCOMPONENTS.ALL;

程序包的使用都可以在EDIT-》language templates-》VHDL-》Common Constructs-》Convertion Functions中找到例子。

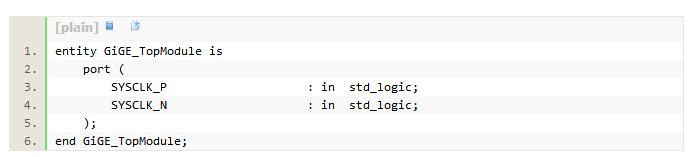

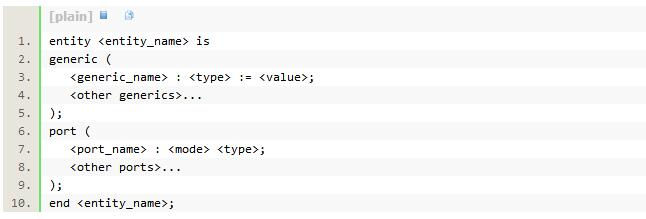

2、實(shí)體entity

實(shí)體類似于原理圖中的一個(gè)部件符號(hào),它并不描述設(shè)計(jì)的具體功能,只是定義所需的全部輸入/輸出信號(hào)。

舉例:

套用EDIT-》language templates-》VHDL-》Common Constructs-》Architecture Components & entity的舉例

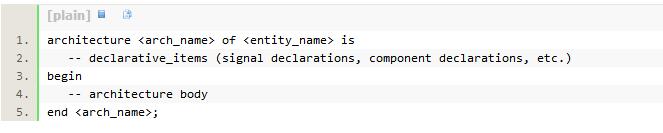

3、結(jié)構(gòu)體architecture

所有能被仿真的實(shí)體都由結(jié)構(gòu)體(ARCHITECTURE)描述,即結(jié)構(gòu)體描述實(shí)體的結(jié)構(gòu)或行為,一個(gè)實(shí)體可以有多個(gè)結(jié)構(gòu)體,每個(gè)結(jié)構(gòu)體分別代表該實(shí)體功能的不同實(shí)現(xiàn)方案。

結(jié)構(gòu)體名是對(duì)本結(jié)構(gòu)體的命名,它是該結(jié)構(gòu)體的惟一名稱,雖然可以由設(shè)計(jì)人員自由命名,但一般都將命名和對(duì)實(shí)體的描述結(jié)合起來(lái),結(jié)構(gòu)體對(duì)實(shí)體描述有三種方式(括號(hào)中為命名):

1) 行為描述(BEHAVE):反映一個(gè)設(shè)計(jì)的功能和算法,一般使用進(jìn)程PROCESS,用順序語(yǔ)句表達(dá);(下例中的情況)

2) 結(jié)構(gòu)描述(STRUCT):反映一個(gè)設(shè)計(jì)硬件方面的特征,表達(dá)了內(nèi)部元件間連接關(guān)系,使用元件例化來(lái)描述;

3) 數(shù)據(jù)流描述(DATAFLOW):反映一個(gè)設(shè)計(jì)中數(shù)據(jù)從輸入到輸出的流向,使用并行語(yǔ)句描述

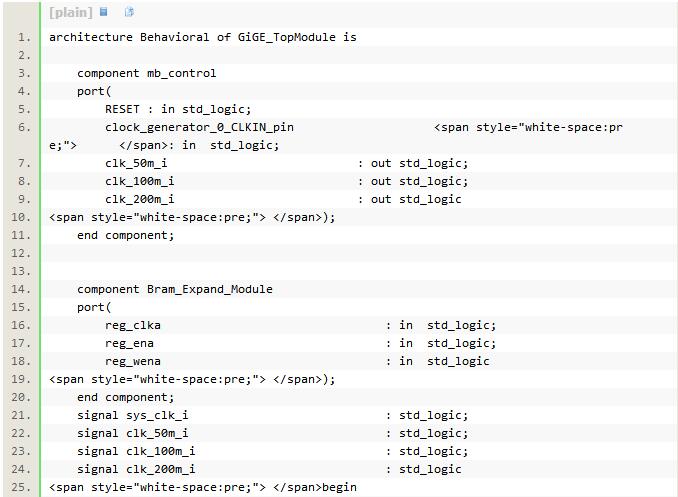

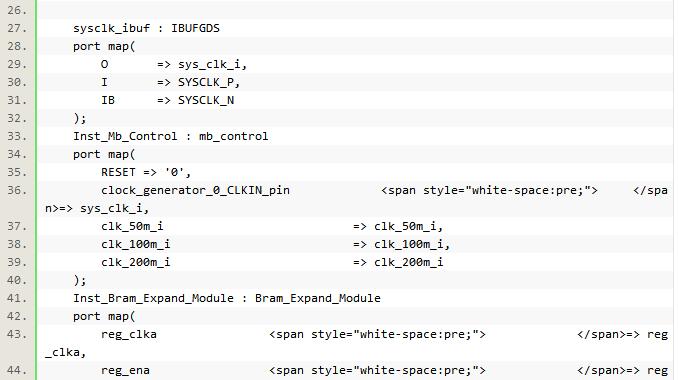

舉例:

套用EDIT-》language templates-》VHDL-》Common Constructs-》Architecture Components & entity的舉例

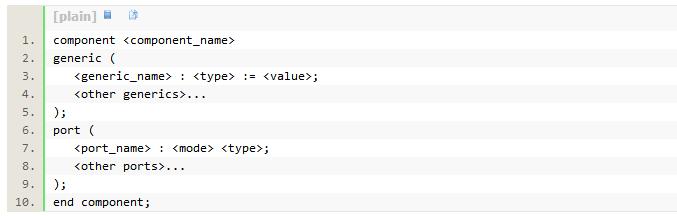

4、元件component

上面例子中有了component的例化,具體的:

-

vhdl

+關(guān)注

關(guān)注

30文章

819瀏覽量

129630 -

FPGA開(kāi)發(fā)

+關(guān)注

關(guān)注

1文章

44瀏覽量

15350

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA入門:Verilog/VHDL語(yǔ)法學(xué)習(xí)的經(jīng)驗(yàn)之談

FPGA入門:基本開(kāi)發(fā)流程概述

FPGA入門:基本開(kāi)發(fā)流程概述

勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載4:Verilog與VHDL

FPGA基本開(kāi)發(fā)流程概述

FPGA與VHDL快速工程實(shí)踐從入門到提高

VHDL語(yǔ)言在FPGA/CPLD開(kāi)發(fā)中的應(yīng)用?

用VHDL/VerilogHD語(yǔ)言開(kāi)發(fā)PLD/FPGA的完整流程

基于VHDL的FPGA和Nios_II實(shí)例精煉

關(guān)于FPGA它的開(kāi)發(fā)流程是怎樣的

FPGA入門之FPGA 開(kāi)發(fā)流程

FPGA的詳細(xì)開(kāi)發(fā)流程

FPGA入門筆記_FPGA開(kāi)發(fā)流程及VHDL基本語(yǔ)法

FPGA入門筆記_FPGA開(kāi)發(fā)流程及VHDL基本語(yǔ)法

評(píng)論