文章來源:學(xué)習(xí)那些事

原文作者:小陳婆婆

本文主要介紹基于TSV的三維集成電路的相關(guān)知識(shí)。

三維集成電路工藝技術(shù)因特征尺寸縮小與系統(tǒng)復(fù)雜度提升而發(fā)展,其核心目標(biāo)在于通過垂直堆疊芯片突破二維物理極限,同時(shí)滿足高密度、高性能、高可靠性及低成本的綜合需求。

為實(shí)現(xiàn)這一目標(biāo),工藝需聚焦硅通孔(TSV)技術(shù)的優(yōu)化,包括采用微小直徑TSV陣列以最小化芯片面積占用并提升數(shù)據(jù)傳輸帶寬,同時(shí)縮短TSV高度、降低寄生電容以適配高速低功耗器件需求;此外,需通過熱管理設(shè)計(jì)增強(qiáng)散熱能力以確保熱力學(xué)與電學(xué)穩(wěn)定性,并確保三維集成流程對(duì)前后端工藝(FEOL/BEOL)的兼容性,減少工藝擾動(dòng)。

典型銅(Cu)TSV制造流程涵蓋通孔刻蝕、絕緣層沉積、黏附層與擴(kuò)散阻擋層沉積、種子層制備及電鍍填充銅材料,后續(xù)需結(jié)合硅片減薄、高精度對(duì)準(zhǔn)與鍵合技術(shù)完成多層芯片互聯(lián),盡管實(shí)際工藝順序可能調(diào)整,但整體以TSV制備、減薄、鍵合為主線。最終,通過晶圓級(jí)鍵合、已知合格芯片(KGD)篩選及異構(gòu)芯片堆疊策略,工藝需在性能、良率與成本間取得平衡,推動(dòng)三維集成技術(shù)向規(guī)模化應(yīng)用演進(jìn)。

本文主要介紹基于TSV的三維集成電路的相關(guān)知識(shí),分述如下:

TSV制造順序分類與工藝特點(diǎn)

三維集成電路堆疊方式

三維集成電路鍵合方式

TSV制造順序分類與工藝特點(diǎn)

根據(jù)TSV(硅通孔)在集成電路工藝流程中的位置,可將其制造順序分為先通孔(Via First)、中通孔(Via Middle)和后通孔(Via Last)三類。

以下為三類工藝的核心差異與關(guān)鍵技術(shù)要點(diǎn):

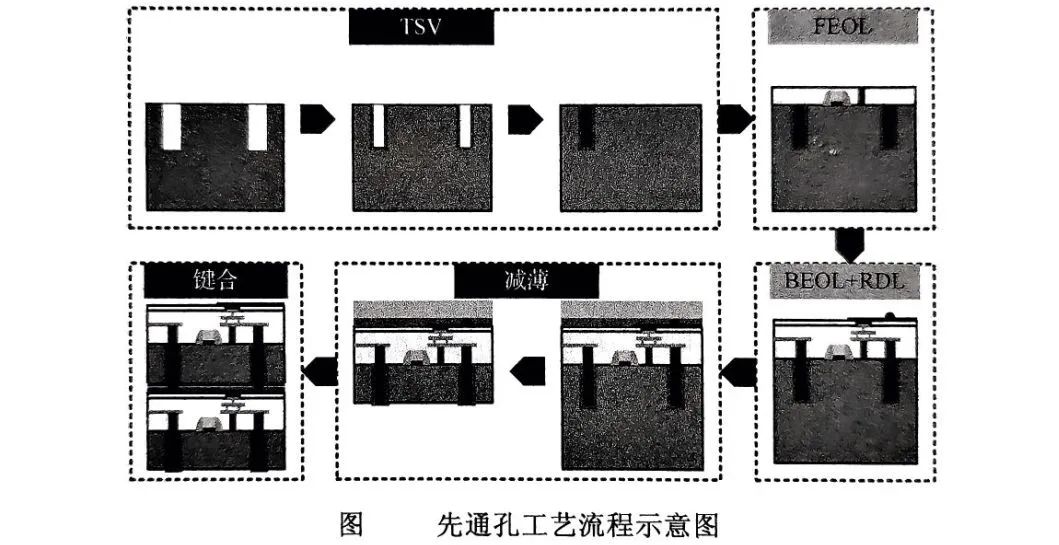

1. 先通孔工藝(Via First)

工藝順序:在CMOS前道工藝(FEOL)前制造TSV,即空白硅片上完成TSV刻蝕、絕緣層沉積、導(dǎo)電材料填充(如多晶硅或鎢)后,再進(jìn)行晶體管及互連層制造。

核心特點(diǎn):

材料選擇:需耐受1000℃以上高溫(如多晶硅、鎢),避免后續(xù)CMOS工藝損壞TSV結(jié)構(gòu)。

連接方式:TSV通過鎢塞與第一層金屬(M1)互連,無法直接鍵合相鄰層TSV,需借助平面互連層過渡。

優(yōu)勢:工藝簡化(無需擴(kuò)散阻擋層/種子層)、熱匹配性好(多晶硅CTE與硅接近)、支持高深寬比TSV(20:1以上)。

局限:電阻率高(多晶硅/鎢電阻遠(yuǎn)高于銅),TSV直徑較大(1~5μm),靈活性受限。

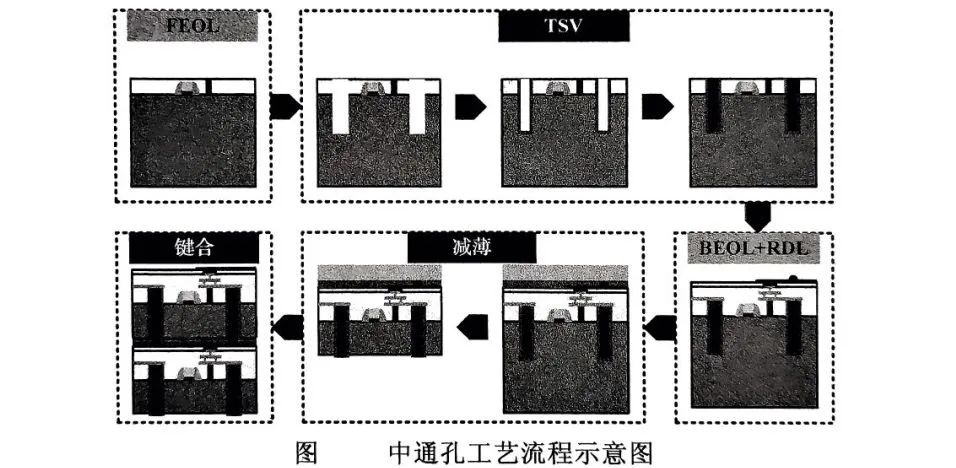

2. 中通孔工藝(Via Middle)

工藝順序:在CMOS前道工藝(FEOL)完成后、后道工藝(BEOL)前制造TSV,即晶體管制造后、多層互連前插入TSV流程。

核心特點(diǎn):

材料選擇:優(yōu)先使用銅(Cu)填充,電學(xué)性能優(yōu)異(低電阻、低寄生電容),但需復(fù)雜擴(kuò)散阻擋層防止銅污染。

連接方式:TSV與M1層直接互連,設(shè)計(jì)靈活性高,但需優(yōu)化CMP工藝(需高選擇比去除銅而不損傷鎢塞)。

優(yōu)勢:兼容標(biāo)準(zhǔn)CMOS工藝,TSV深寬比均勻,支持高層金屬連接(如Mn),適合高性能需求。

局限:銅熱膨脹系數(shù)(CTE)與硅差異大,易引發(fā)熱應(yīng)力問題;TSV刻蝕需避開金屬層,設(shè)計(jì)約束較多。

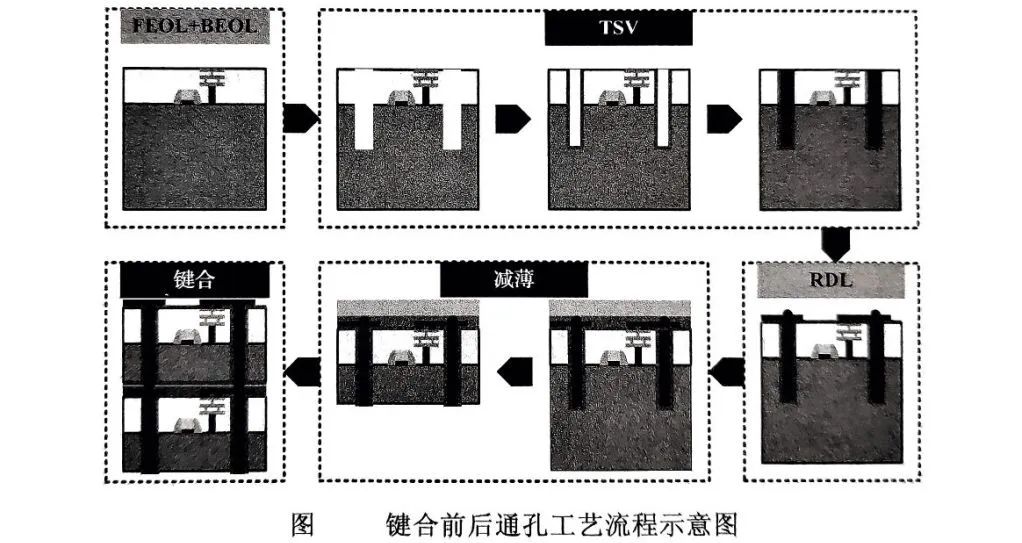

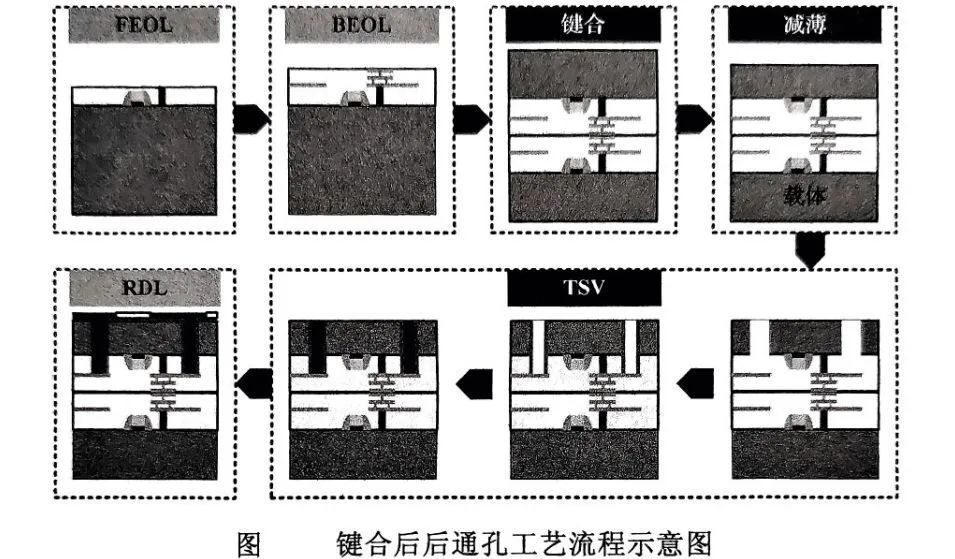

3. 后通孔工藝(Via Last)

工藝順序:在CMOS后道工藝(BEOL)完成后制造TSV,分鍵合前和鍵合后兩種子類:

鍵合前后通孔:BEOL完成后制造TSV,再鍵合芯片并減薄。

鍵合后后通孔:先鍵合減薄硅片,再制造TSV并通過電鍍或熱壓鍵合實(shí)現(xiàn)層間連接。

核心特點(diǎn):

材料選擇:銅為主流填充材料,支持TSV直接鍵合(如Cu-Cu熱壓鍵合),連接強(qiáng)度高。

連接方式:TSV可跨層直接連接(如Mn到Mn),但需解決介質(zhì)層刻蝕難題(如低k材料橫向展寬)。

優(yōu)勢:TSV位置靈活,支持異構(gòu)芯片堆疊,適合高密度集成。

局限:刻蝕工藝復(fù)雜(需穿透多層介質(zhì)/硅),CMP需兼容最終金屬層,成本較高。

4. 工藝對(duì)比與選型依據(jù)

性能優(yōu)先:中通孔(銅TSV)適用于高速低功耗場景;先通孔(多晶硅/鎢)適合高溫工藝兼容需求。

成本敏感:先通孔工藝可由硅片廠商預(yù)制,降低封裝成本;后通孔需復(fù)雜刻蝕,成本較高。

設(shè)計(jì)靈活性:中通孔支持高層金屬連接,后通孔實(shí)現(xiàn)跨層直接鍵合,先通孔受限于固定位置。

可靠性:先通孔熱應(yīng)力低,中通孔需解決銅擴(kuò)散問題,后通孔需優(yōu)化介質(zhì)層刻蝕損傷。

三類工藝各有優(yōu)劣,需根據(jù)產(chǎn)品需求綜合選型。

三維集成電路堆疊方式

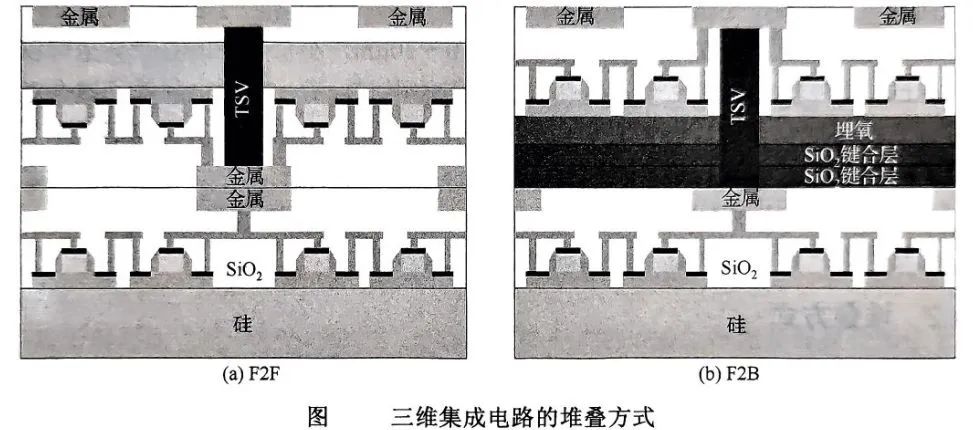

在三維集成電路中,芯片間鍵合的堆疊方式直接影響互連密度、散熱性能及工藝復(fù)雜度,主要分為正面對(duì)正面(F2F)和正面對(duì)背面(F2B)兩種模式。

1. 正面對(duì)正面(F2F)堆疊

結(jié)構(gòu)特點(diǎn):上層芯片翻轉(zhuǎn)后正面朝下,與下層芯片正面直接鍵合,器件層相對(duì)放置。

核心優(yōu)勢:

高密度互連:除TSV外,上下層芯片可通過金屬凸點(diǎn)直接鍵合,互連數(shù)量可超越TSV限制,簡化工藝并提升可靠性。

工藝靈活性:上層芯片可在減薄前完成鍵合,無需輔助圓片支撐。

主要局限:

散熱挑戰(zhàn):器件層間距小,集成后發(fā)熱密度高,需強(qiáng)化散熱設(shè)計(jì)。

多層擴(kuò)展受限:若堆疊超過兩層,上層芯片需轉(zhuǎn)為F2B模式,無法持續(xù)利用金屬凸點(diǎn)互連。

2. 正面對(duì)背面(F2B)堆疊

結(jié)構(gòu)特點(diǎn):上層芯片保持正面朝上,通過背面與下層芯片鍵合,器件層順序排列。

核心優(yōu)勢:

散熱優(yōu)化:硅襯底位于兩層器件層之間,增強(qiáng)散熱能力。

多層兼容性:工藝流程可重復(fù)擴(kuò)展,天然適配三層及以上芯片堆疊。

主要局限:

工藝復(fù)雜度:需預(yù)先減薄上層芯片,且需輔助圓片防止彎曲變形。

互連依賴TSV:層間互連完全由TSV數(shù)量決定,難以實(shí)現(xiàn)F2F的凸點(diǎn)級(jí)互連密度。

3. 堆疊方式選型依據(jù)

兩層堆疊優(yōu)先F2F:最大化利用金屬凸點(diǎn)互連,降低成本并簡化流程。

三層及以上必選F2B:確保工藝可擴(kuò)展性,但可結(jié)合混合模式(如首尾層用F2F,中間層用F2B)。

功能需求主導(dǎo):特定應(yīng)用(如傳感器、光電集成)可能要求固定朝向,需按功能設(shè)計(jì)選擇堆疊方式。

F2F以互連密度和工藝簡化見長,適合兩層堆疊;F2B通過散熱優(yōu)化和多層兼容性主導(dǎo)復(fù)雜集成,二者可靈活組合以平衡性能與成本。

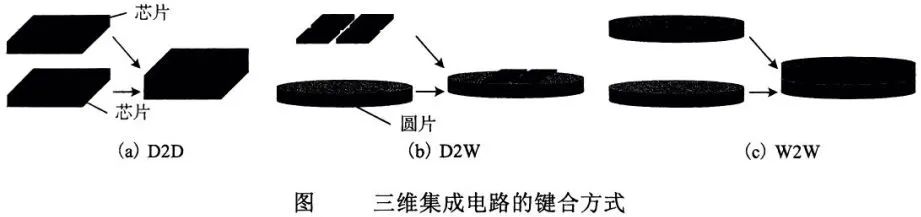

三維集成電路鍵合方式

在三維集成電路制造中,鍵合方式的選擇直接影響成品率、成本及工藝效率,主要分為芯片到芯片(D2D)、芯片到圓片(D2W)和圓片到圓片(W2W)三種模式。

1. 芯片到芯片(D2D)鍵合

核心特點(diǎn):單個(gè)芯片與單個(gè)芯片直接鍵合。

優(yōu)勢:

成品率優(yōu)化:鍵合前可剔除失效芯片,避免低良率芯片影響整體成品率。

靈活性高:適配不同尺寸芯片堆疊,減少小尺寸芯片浪費(fèi)。

局限:

效率低:逐芯片鍵合耗時(shí),對(duì)準(zhǔn)精度有限(通常5~10μm)。

成本敏感:適用于小批量或高價(jià)值芯片,大規(guī)模生產(chǎn)效率不足。

2. 芯片到圓片(D2W)鍵合

核心特點(diǎn):單個(gè)芯片與完整圓片鍵合。

優(yōu)勢:

效率提升:圓片固定后重復(fù)鍵合芯片,減少裝載時(shí)間。

良率控制:圓片及芯片均可預(yù)測試,跳過失效區(qū)域以降低成本。

局限:

熱應(yīng)力風(fēng)險(xiǎn):圓片及已鍵合芯片需多次經(jīng)歷高溫工藝,可靠性受挑戰(zhàn)。

工藝復(fù)雜:需精確控制芯片與圓片間熱膨脹系數(shù)(CTE)匹配。

3. 圓片到圓片(W2W)鍵合

核心特點(diǎn):完整圓片與完整圓片一次性鍵合。

優(yōu)勢:

效率最高:單次對(duì)準(zhǔn)完成全圓片鍵合,適合大規(guī)模生產(chǎn)。

熱過程少:僅需一次高溫工藝,熱應(yīng)力風(fēng)險(xiǎn)低。

局限:

成品率風(fēng)險(xiǎn):無法預(yù)剔除失效芯片,單層良率低將導(dǎo)致整體成本激增。

尺寸限制:要求上下層圓片尺寸嚴(yán)格匹配,否則造成面積浪費(fèi)。

4. 鍵合方式選型策略

D2D適用場景:堆疊芯片良率波動(dòng)大、尺寸差異顯著,或需定制化小批量生產(chǎn)。

D2W平衡選擇:兼顧效率與良率控制,適用于中等規(guī)模生產(chǎn)及對(duì)熱管理要求嚴(yán)格的場景。

W2W效率優(yōu)先:僅當(dāng)圓片尺寸匹配、良率極高(如≥99%)時(shí)采用,常見于同質(zhì)芯片堆疊(如存儲(chǔ)器立方體)。

鍵合方式的選擇需綜合考量成本、良率、熱穩(wěn)定性及尺寸兼容性。小尺寸芯片或高良率場景下,W2W可顯著降低成本;而復(fù)雜異構(gòu)集成或良率敏感場景中,D2D或D2W的靈活性更為關(guān)鍵。

-

芯片

+關(guān)注

關(guān)注

459文章

52443瀏覽量

439797 -

集成電路

+關(guān)注

關(guān)注

5422文章

12030瀏覽量

368161 -

鍵合

+關(guān)注

關(guān)注

0文章

80瀏覽量

8093 -

TSV

+關(guān)注

關(guān)注

4文章

123瀏覽量

81917

原文標(biāo)題:基于TSV的三維集成電路

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

高通和英特爾介紹用在移動(dòng)SOC的TSV三維封裝技術(shù)

集成電路制造技術(shù)的應(yīng)用

世界級(jí)專家為你解讀:晶圓級(jí)三維系統(tǒng)集成技術(shù)

有償,用matlab仿真三維電路互連線尺寸調(diào)整對(duì)延時(shí)功耗帶寬影響

三維設(shè)計(jì)應(yīng)用案例

基于TSVArray的三維集成電路優(yōu)化設(shè)計(jì)研究

三維集成電路系統(tǒng)的電網(wǎng)分析

集成電路由二維向三維發(fā)展是必行趨勢

三維集成電路(IC)設(shè)計(jì)中的溫度控制

基于高溫共燒陶瓷基板的三維互連技術(shù)

10.9.6 三維集成電路測試∈《集成電路產(chǎn)業(yè)全書》

10.5.2 基于TSV的三維集成電路∈《集成電路產(chǎn)業(yè)全書》

一文解鎖TSV制程工藝及技術(shù)

基于TSV的三維集成電路制造技術(shù)

基于TSV的三維集成電路制造技術(shù)

評(píng)論