大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來聊一聊FPGA中不可綜合語句 相關(guān)知識(shí)。

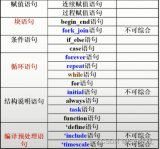

(1)所有綜合工具都支持的結(jié)構(gòu):always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not, bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。

(2)所有綜合工具都不支持的結(jié)構(gòu):time,defparam,$finish,fork,join,initial,delays,UDP,wait。

(3)有些工具支持有些工具不支持的結(jié)構(gòu):casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。

建立可綜合模型的原則

要保證Verilog HDL賦值語句的可綜合性,在建模時(shí)應(yīng)注意以下要點(diǎn):

(1)不使用initial。

(2)不使用#10。

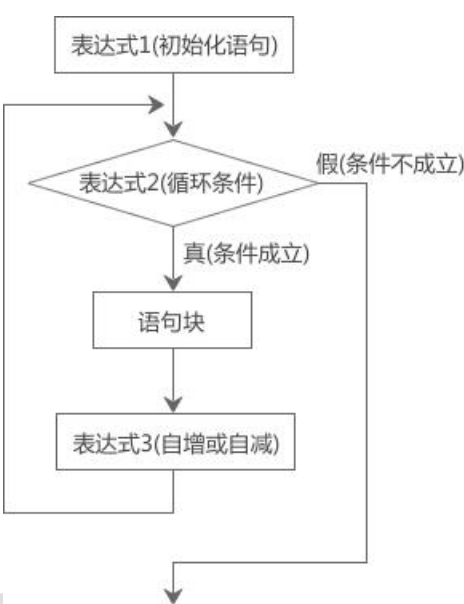

(3)不使用循環(huán)次數(shù)不確定的循環(huán)語句,如forever、while等。

(4)不使用用戶自定義原語(UDP元件)。

(5)盡量使用同步方式設(shè)計(jì)電路。

(6)除非是關(guān)鍵路徑的設(shè)計(jì),一般不采用調(diào)用門級(jí)元件來描述設(shè)計(jì)的方法,建議采用行為語句來完成設(shè)計(jì)。

(7)用always過程塊描述組合邏輯,應(yīng)在敏感信號(hào)列表中列出所有的輸入信號(hào)。

(8)所有的內(nèi)部寄存器都應(yīng)該能夠被復(fù)位,在使用FPGA實(shí)現(xiàn)設(shè)計(jì)時(shí),應(yīng)盡量使用器件的全局復(fù)位端作為系統(tǒng)總的復(fù)位。

(9)對(duì)時(shí)序邏輯描述和建模,應(yīng)盡量使用非阻塞賦值方式。對(duì)組合邏輯描述和建模,既可以用阻塞賦值,也可以用非阻塞賦值。但在同一個(gè)過程塊中,最好不要同時(shí)用阻塞賦值和非阻塞賦值。

(10)不能在一個(gè)以上的always過程塊中對(duì)同一個(gè)變量賦值。而對(duì)同一個(gè)賦值對(duì)象不能既使用阻塞式賦值,又使用非阻塞式賦值。

(11)如果不打算把變量推導(dǎo)成鎖存器,那么必須在if語句或case語句的所有條件分支中都對(duì)變量明確地賦值。

(12)避免混合使用上升沿和下降沿觸發(fā)的觸發(fā)器。

(13)同一個(gè)變量的賦值不能受多個(gè)時(shí)鐘控制,也不能受兩種不同的時(shí)鐘條件(或者不同的時(shí)鐘沿)控制。

(14)避免在case語句的分支項(xiàng)中使用x值或z值。

1、initial

只能在test bench中使用,不能綜合。(我用ISE9.1綜合時(shí),有的簡(jiǎn)單的initial也可以綜合,不知道為什么)

2、events

event在同步test bench時(shí)更有用,不能綜合。

3、real

不支持real數(shù)據(jù)類型的綜合。

4、time

不支持time數(shù)據(jù)類型的綜合。

5、force 和release

不支持force和release的綜合。

6、assign 和deassign

不支持對(duì)reg 數(shù)據(jù)類型的assign或deassign進(jìn)行綜合,支持對(duì)wire數(shù)據(jù)類型的assign或deassign進(jìn)行綜合。

7、fork join

不可綜合,可以使用非塊語句達(dá)到同樣的效果。

8、primitives

支持門級(jí)原語的綜合,不支持非門級(jí)原語的綜合。

9、table

不支持UDP 和table的綜合。

10、敏感列表里同時(shí)帶有posedge和negedge

如:always @(posedge clk or negedge clk) begin...end

這個(gè)always塊不可綜合。

11、同一個(gè)reg變量被多個(gè)always塊驅(qū)動(dòng)

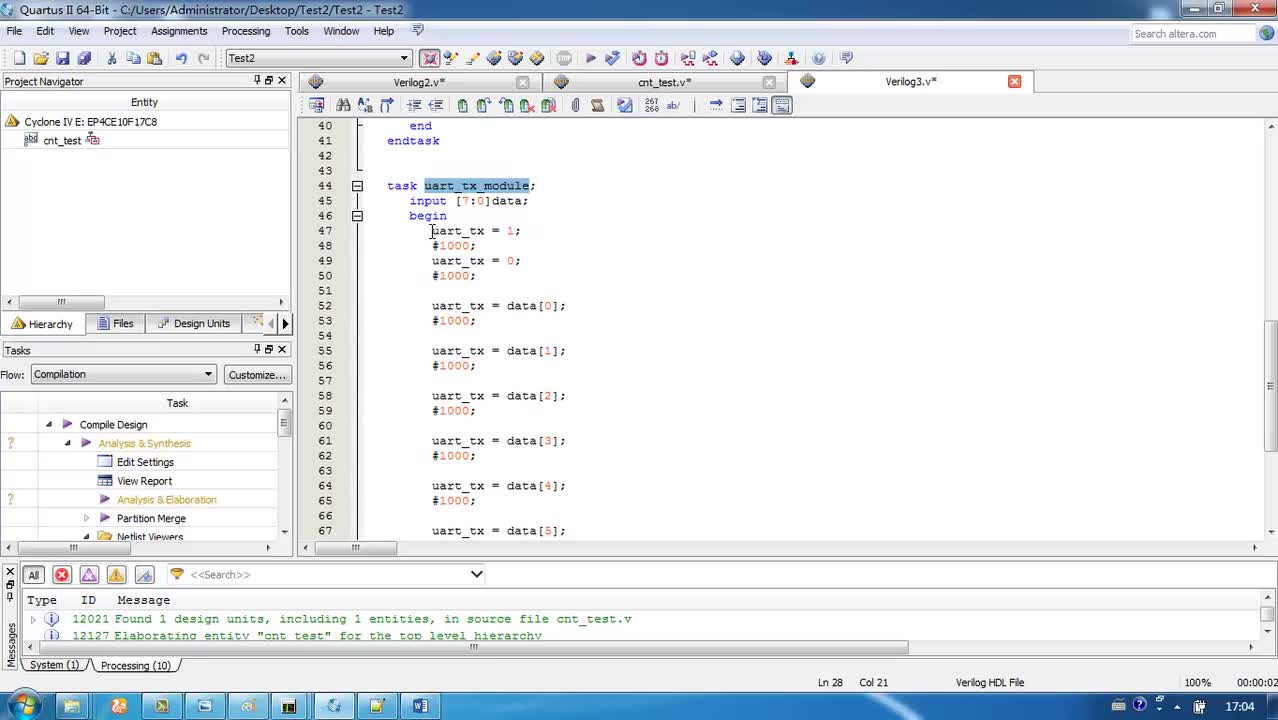

12、延時(shí)

以#開頭的延時(shí)不可綜合成硬件電路延時(shí),綜合工具會(huì)忽略所有延時(shí)代碼,但不會(huì)報(bào)錯(cuò)。

如:a=#10 b;

這里的#10是用于仿真時(shí)的延時(shí),在綜合的時(shí)候綜合工具會(huì)忽略它。也就是說,在綜合的時(shí)候上式等同于a=b;

13、與X、Z的比較

可能會(huì)有人喜歡在條件表達(dá)式中把數(shù)據(jù)和X(或Z)進(jìn)行比較,殊不知這是不可綜合的,綜合工具同樣會(huì)忽略。所以要確保信號(hào)只有兩個(gè)狀態(tài):0或1。

如:

1 module synthesis_compare_xz (a,b);

2 output a;

3 input b;

4 reg a;

5

6 always @ (b)

7 begin

8 if ((b == 1'bz) || (b == 1'bx)) begin

9 a = 1;

10 end else begin

11 a = 0;

12 end

13 end

14

15 endmodule

今天就聊到這里這里,后續(xù)還會(huì)更新,加油,各位!

-

FPGA

+關(guān)注

關(guān)注

1646文章

22054瀏覽量

618813

發(fā)布評(píng)論請(qǐng)先 登錄

verilog不可綜合語句總結(jié)

Verilog 中generate if語句如何用systemc實(shí)現(xiàn)?

verilog可綜合與不可綜合-學(xué)習(xí)一下

C51原理及相關(guān)基礎(chǔ)入門知識(shí)

verilog可綜合與不可綜合語句概述

verilog 不可綜合語句

FPGA學(xué)習(xí)系列:6.組合邏輯和時(shí)序邏輯

FPGA中不可綜合語句 相關(guān)知識(shí)

FPGA中不可綜合語句 相關(guān)知識(shí)

評(píng)論