循環(huán)語句允許多次執(zhí)行編程語句或begin-end語句組。SystemVerilog中的循環(huán)語句有:for、repeat、while、do..while、foreach和forever。

2022-11-03 09:10:33 1354

1354

C語言基礎知識(5)--循環(huán)語句

2023-06-15 10:18:54 1275

1275

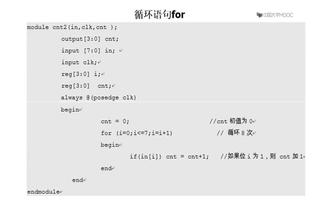

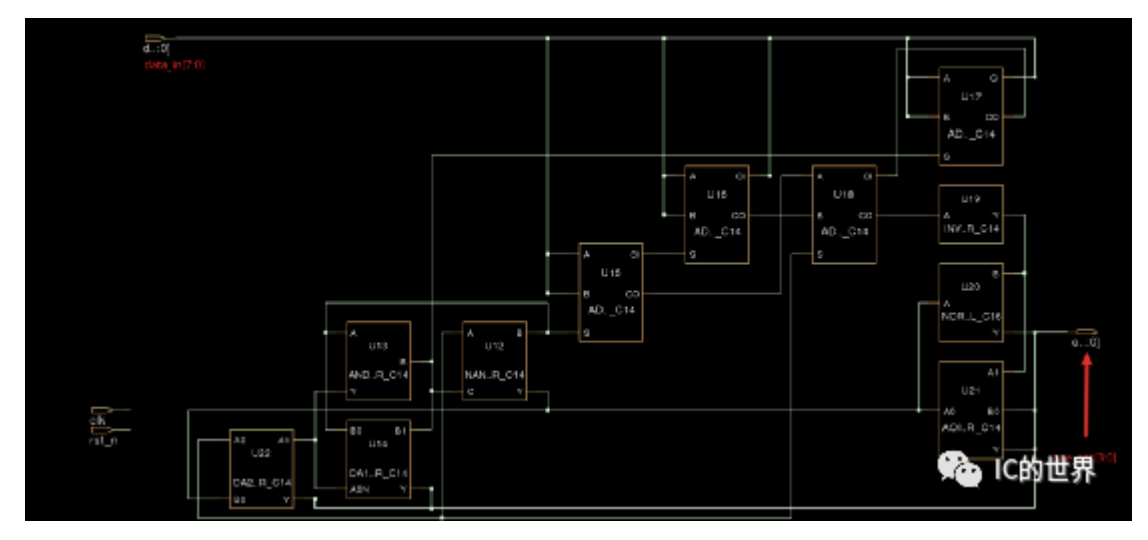

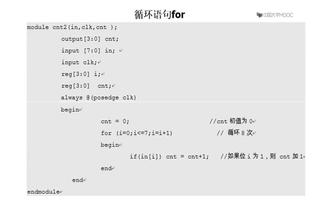

利用for循環(huán)實現(xiàn)對信號的賦值。

2023-08-03 10:22:27 1482

1482 在C語言中,break語句是一種控制流語句,它用于終止當前所在的循環(huán)結構(for、while、do-while)或者switch語句,從而跳出循環(huán)或者結束switch語句的執(zhí)行。

2023-08-17 15:35:46 917

917 FOR循環(huán)語句應用比較廣泛,在機器人編程、PLC編程、C語言編程中都有應用。能讀懂這些程序語句,可以更好地理解機電設備控制原理,為機電設備安裝維修工作帶來便利。

2023-09-25 17:14:51 2516

2516

首先,考慮x和z在verilog條件語句中的使用情況,然后我們再考慮在verilog中用x和z給其他reg/wire賦值的情況。

2023-11-02 09:40:10 478

478

,不同的模擬選項導致開始模擬時現(xiàn)象不同建議: 在0時刻通過非阻塞賦值設置reset信號;第一個半周期設置clock為0編寫Verilog代 碼的一些經驗:Verilog文件名和模塊名相同不要在可綜合代碼

2019-03-26 08:00:00

1.Verilog 中generate if語句如何用systemc實現(xiàn)?例如:generateif (SIZE < 8)assign y = a & b & c;else

2014-08-29 16:11:21

Verilog可綜合子集

2013-04-01 12:44:46

Verilog 中generate if語句如何用systemc實現(xiàn)?例如:generateif (SIZE < 8)assign y = a & b & c;else

2014-08-28 12:06:43

Verilog中的always塊內的語句執(zhí)行的速度是什么樣的,如果always塊是時鐘上升沿觸發(fā)的,會不會塊內語句還未執(zhí)行完,而下一個時鐘上升沿又來了???

2015-10-29 22:30:43

以前很少用for語句,以為是不可綜合的。在印象中好像只用循環(huán)生成(for...generate)語句綜合過多個模塊。最近在仔細研讀《輕松成為設計高手——Verilog HDL使用精解》這本書,才知道

2014-08-13 14:59:34

在書上看到,“for循環(huán)更多的表示為根據(jù)循環(huán)次數(shù)來復制一個電路”。那么我現(xiàn)在有一個問題,for循環(huán)的次數(shù)是一個input型的參數(shù)(位寬已知,具體是多少是由輸入決定的)。這樣可以被綜合嗎?

2018-08-22 13:22:20

1,在一個verilog程序里,如果循環(huán)是一個循環(huán)次數(shù)不可定的循環(huán),那么它能被綜合工具綜合嗎2,如果程序里有always @(clock)里面又嵌套了@(clock)這樣的控制事件,這個能被綜合嗎

2015-02-03 15:29:11

。 建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時應注意以下要點: (1)不使用初始化語句。 (2)不使用帶有延時的描述。 (3)不使用循環(huán)次數(shù)不確定的循環(huán)語句,如

2012-10-20 08:10:13

,若不是,則只能用于仿真),while, 建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時應注意以下要點: (1)不使用initial。 (2)不使用#10。 (3)不使

2015-01-05 19:42:44

,arrays,memories,repeat,task,while。建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時應注意以下要點: (1)不使用initial。 (2)不使

2012-02-27 15:01:27

,使用生成語句能大大簡化程序的編寫過程。Verilog-2001添加了generate循環(huán),允許產生module和primitive的多個實例化,generate語句的最主要功能就是對module、reg

2020-12-23 16:59:15

各位大神,我在學習verilog的過程中遇到一個問題,如圖中代碼,后面3個@(...)是什么意思?有什么作用?為什么我用Xilinx的綜合工具不能綜合?請大神們指教!(真誠臉

2017-08-14 12:06:47

考慮清楚了。可以看著圖直接寫code。 要知道,最初Verilog是為了實現(xiàn)仿真而發(fā)明的.不可綜合的Verilog語句也是很重要的.因為在實際設計電路時,除了要實現(xiàn)一個可綜合的module外,你還要

2017-04-05 20:34:43

verilog的仿真和綜合有什么區(qū)別,請具體一點?

2018-06-06 22:41:18

verilog設計練習進。我們可以先理解樣板模塊中每一條語句的作用,然后對樣板模塊進行綜合前和綜合后仿真,再獨立完成每一階段規(guī)定的練習。當十個階段的練習做完后,便可以開始設計一些簡單的邏輯電路和系統(tǒng)

2012-08-15 16:29:30

可綜合的Verilog語法和語義(劍橋大學,影印)

2012-08-06 13:03:57

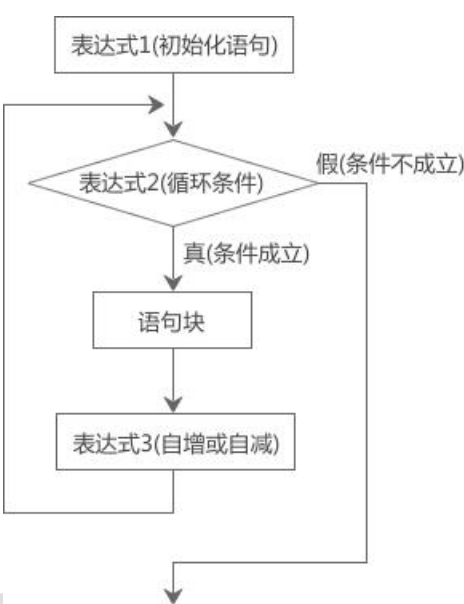

For循環(huán)是任何HDL語言中最讓人容易誤解的代碼之一。For循環(huán)可以以可綜合與不可綜合兩種版本實現(xiàn)。不過C語言中的For循環(huán)與HDL眾的For循環(huán)不太一樣,要想熟練運用的話就得先理解它。將軟件編程

2019-08-07 05:00:00

可綜合的語法子集3本文節(jié)選自特權同學的圖書《FPGA設計實戰(zhàn)演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt(1) 多語句定義:begin…end

2015-06-17 11:53:27

類似C的環(huán)路結構如for-loop可能對學過C語言的人存在陷阱。其原因是在硬件語言中并沒有隱含的寄存器這個條件,所以一般這些環(huán)路不可以在可綜合代碼中用來做算法迭代。在Verilog中,for循環(huán)一般

2018-08-08 11:02:25

一:基本Verilog中的變量有線網(wǎng)類型和寄存器類型。線網(wǎng)型變量綜合成wire,而寄存器可能綜合成WIRE,鎖存器和觸發(fā)器。二:verilog語句結構到門級的映射1、連續(xù)性賦值:assign連續(xù)性

2012-02-24 10:37:21

,都有Xilinx公司自己寫好的可綜合的模塊,想請教一下為什么要分成這樣兩項?它們里面的模塊有區(qū)別嗎?2、上述談到的可綜合模塊和ISE 自帶的IP core又有什么區(qū)別呢?

2013-09-28 18:17:54

chisel 中可以用Verilog 語句嗎 ?

2022-03-11 14:23:16

Verilog HDL 在執(zhí)行語句時分為順序和并行兩種方式。在順序語句塊中,語句按給定次序順序執(zhí)行;在并行語句塊中,語句并行執(zhí)行。順序語句塊的語法和實例如下:begin[:block_id

2018-09-25 09:22:19

流程控制語句包括:? if 語句;? case 語句;? 循環(huán)語句。if 語句的語法如下:if(condition_1)procedural_statement_1{else

2018-09-26 09:21:53

本帖最后由 630183258 于 2016-11-4 13:41 編輯

關于阻塞:計算RHS并更新LHS,此時不能允許有來自任何其他Verilog語句的干擾。 所謂阻塞的概念是指在同一個

2016-11-03 20:26:38

HDL操作數(shù)和操作符4.Verilog HDL和VHDL語言的對比5.Verilog HDL循環(huán)語句6.Verilog HDL程序的基本結構7.Verilog HDL語言的數(shù)據(jù)類型和運算符

2018-09-19 11:34:03

do{..........} while(1) 和for(;;)[..............]這兩個語句都代表死循環(huán)吧都是一樣的意思吧!

2018-09-26 17:37:01

大多是可綜合的。Verilog中絕大多數(shù)運算操作符都是可綜合的,其列表如下:+// 加-// 減!// 邏輯非~// 取反&// 與~&// 與非|// 或~|// 或非

2017-12-19 21:36:24

1、不使用初始化語句;2、不使用延時語句;3、不使用循環(huán)次數(shù)不確定的語句,如:forever,while等;4、盡量采用同步方式設計電路;5、盡量采用行為語句完成設計;6、always過程塊描述組合

2021-07-29 06:10:04

我在verilog中嘗試了for循環(huán)中的模塊實例化...我需要在特定條件到達時停止執(zhí)行循環(huán)。任何人請告訴我如何阻止它。

2019-10-25 09:38:11

verilog 中的 generate for 語句好理解,但是 generate if 和 generate case 語句怎么理解??

2014-12-21 12:44:21

在循環(huán)中嵌入定時語句,比如"always @ posedge clk" 能不能被綜合呢,為什么書上的說可以,但是在quatus里面卻提示不能,是不是不同的綜合工具對這種綜合的支持還不一樣

2015-02-02 19:39:40

采用列表框選擇 1 2 3 然后 條件語句相應會有反應。問題: 打算點擊每個while的stop然后退出此while,然后選擇列表框另一選項,相應的另一while循環(huán)動作。

2016-02-16 12:30:01

在本篇里,我們討論 Verilog 語言的綜合問題,Verilog HDL (Hardware Description Language) 中文名為硬件描述語言,而不是硬件設計語言。這個名稱提醒我們

2021-07-29 07:42:25

Verilog HDL 綜合實用教程第1章 基礎知識第2章 從Verilog結構到邏輯門第3章 建模示例第4章 模型的優(yōu)化第5章 驗證附錄A 可綜合的語言結構附錄B 通用庫

2009-07-20 11:21:13 86

86 switch/case開關語句是一種多分支選擇語句,是用來實現(xiàn)多方向條件分支的語句。雖然從理論上講采用條件語句也可以實現(xiàn)多方向條件分支,但是當分支較多時會使條件語句的嵌套層

2010-07-15 14:26:00 18

18 單片機c語言教程第十三課 C51循環(huán)語句

循環(huán)語句是幾乎每個程序都會用到的,它的作用就是用來實現(xiàn)需要反復進行多次的操 作。如一個 12M 的 51 芯片應用電路中要求

2009-04-15 09:42:25 1629

1629 if語句和while循環(huán)

C語言中,if語句和while循環(huán)都會用到布爾表達式。下面是一個使用if語句的簡單例子:

#include

2009-07-29 10:48:32 8304

8304 電子發(fā)燒友網(wǎng)站提供《Verilog HDL數(shù)字設計與綜合(第二版).txt》資料免費下載

2012-04-04 15:57:24 0

0 可綜合的Verilog語法和語義(劍橋大學,影印):第七版

2012-05-21 14:50:14 27

27 電子發(fā)燒友網(wǎng)站提供《Verilog HDL_數(shù)字設計與綜合第二版.txt》資料免費下載

2012-08-07 15:17:15 0

0 電子發(fā)燒友網(wǎng)站提供《Verilog_HDL數(shù)字設計與綜合_夏宇聞譯(第二版).txt》資料免費下載

2013-01-23 12:45:01 0

0 電子發(fā)燒友網(wǎng)站提供《夏宇聞譯(第二版)-Verilog HDL數(shù)字設計與綜合.txt》資料免費下載

2014-09-17 00:08:46 0

0 電子發(fā)燒友網(wǎng)站提供《詳解Verilog HDL數(shù)字設計與綜合 夏宇聞譯(第二版).txt》資料免費下載

2014-09-25 22:19:09 0

0 電子發(fā)燒友網(wǎng)站提供《Verilog HDL數(shù)字設計與綜合_夏宇聞譯(第二版).txt》資料免費下載

2015-09-08 17:43:22 0

0 介紹Verilog HDL數(shù)字設計與綜合的課件

2015-12-23 10:58:54 0

0 C++語言基礎講解視頻do while循環(huán)語句

2016-01-14 15:32:08 5

5 C++語言基礎講解視頻while循環(huán)語句,喜歡的朋友可以下載來學習。

2016-01-14 15:31:45 3

3 通過本章十個階段的練習,一定能逐步掌握Verilog HDL 設計的要點。我們可以先理解樣板模塊中每一條語句的作用,然后對樣板模塊進行綜合前和綜合后仿真,再獨立完成每一階段規(guī)定的練習。

2016-06-08 14:10:53 11

11 Verilog HDL數(shù)字設計與綜合 夏宇聞譯(第二版),感興趣的小伙伴們可以瞧一瞧。

2016-11-11 11:20:11 0

0 在很多地方都能看到,verilog中if與case語句必須完整,即if要加上else,case后要加上default語句,以防止鎖存器的發(fā)生,下載內容中就談到了其中原因。

2017-09-16 09:29:03 24

24 循環(huán)語句是幾乎每個程序都會用到的,它的作用就是用來實現(xiàn)需要反復進行多次的操 作。如一個 12M 的 51 芯片應用電路中要求實現(xiàn) 1 毫秒的延時,那么就要執(zhí)行 1000 次空語句 才能達到延時的目的

2017-11-22 12:43:01 866

866 本文檔的主要內容詳細介紹的是Java的循環(huán)語句的詳細資料說明包括了:1、while循環(huán)語句,2、do…while循環(huán)語句,3、for循環(huán)語句

2019-03-22 08:00:00 0

0 在接觸Verilog 語法參考手冊的時候,我們發(fā)現(xiàn)其提供了一組非常豐富的功能來描述硬件。所以大家往往會疑惑那些Verilog語句是可綜合的,那些是只能用于寫Testbench的,其實,參考手冊中只有

2019-04-20 10:59:39 4022

4022 本文檔的主要內容詳細介紹的是FPGA視頻教程之Verilog中兩種不同的賦值語句的資料說明免費下載。

2019-03-27 10:55:59 6

6 1、在許多實際問題中,需要程序進行有規(guī)律的重復執(zhí)行,這時可以用循環(huán)語句來實現(xiàn)。在c語言中。用來實現(xiàn)循環(huán)的語句有for語句,while語句,do-while語句,goto語句等。

2019-08-20 17:31:00 1

1 關于Verilog HDL綜合的討論早在1988年就已經展開。但時至今日,此領域的優(yōu)秀教材尚未囊括其基本概念。這本關于Verilog HDL綜合實用教程全面地介紹了這一新技術。它通過提供便于理解

2019-05-13 08:00:00 74

74 本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-03 07:08:00 2366

2366

可綜合設計的特點:1、不使用初始化語句。2、不使用帶有延時的描述。3、不使用循環(huán)次數(shù)不確定的循環(huán)語句,如: forever 、while 等。4、盡量采用同步方式設計電路。5、除非是關鍵路徑的設計,一般不調用門級元件來描述設計的方法,建議采用行為語句來完成設計。

2019-08-01 16:55:54 11

11 本文檔的主要內容詳細介紹的是Verilog教程之Verilog HDL程序設計語句和描述方式。

2020-12-09 11:24:23 46

46 1、如何使用Verilog HDL描述可綜合電路 Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL語言僅是對已知硬件電路的文本描述。所以編寫前: 對所需實現(xiàn)的硬件

2021-04-04 11:19:00 3838

3838

條件語句的可綜合性 HDL語言的條件語句與算法語言的條件語句,最大的差異在于: 1.不管條件:當前輸入條件沒有對應的描述,則該條件為不管條件(Don’t?Care)。對應不管條件的信號稱為不管信號

2021-05-12 09:12:22 1558

1558

(含循環(huán)體)組成的代碼塊,EDA稱為循環(huán)框架(Loop Frame)。 在這里,HDL循環(huán)語句與算法語言的循環(huán)語句的差異: 1.HDL的循環(huán)變量i是以常量進入循環(huán)體。算法語言則是以變量進入循環(huán)體。 2.HDL的循環(huán)體并不被循環(huán)執(zhí)行,而是被重復描述(多次重復綜合),從而實現(xiàn)建

2021-05-12 09:27:48 1830

1830

解釋verilog HDL中的initial語句的用法。

2021-05-31 09:11:33 0

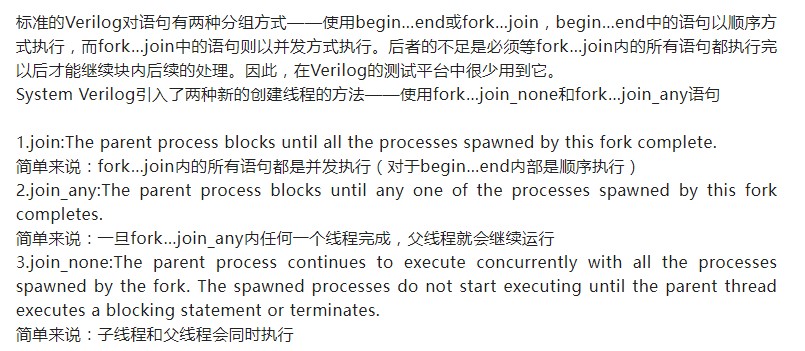

0 1. 塊語句有兩種,一種是 begin-end 語句, 通常用來標志()執(zhí)行的語句;一種是 fork-join 語句,通常用來標志()執(zhí)行的語句。 答案:順序,并行 解析: (1)begin_end

2021-06-18 15:16:49 2741

2741 ? 在Verilog中有兩種類型的賦值語句:阻塞賦值語句(“=”)和非阻塞賦值語句(“=”)。正確地使用這兩種賦值語句對于Verilog的設計和仿真非常重要。 Verilog語言中講的阻塞賦值

2021-12-02 18:24:36 5005

5005

“ 本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括循環(huán)語句(forever、repeat、while和for)、運算符。”

2022-03-15 11:41:58 4027

4027 begin_end順序塊,用于將多條語句組成順序塊,語句按順序一條一條執(zhí)行(除了帶有內嵌延遲控制的非阻塞賦值語句),每條語句的延遲時間是相對于由上一條語句的仿真時間而言;

2022-05-18 10:29:25 1085

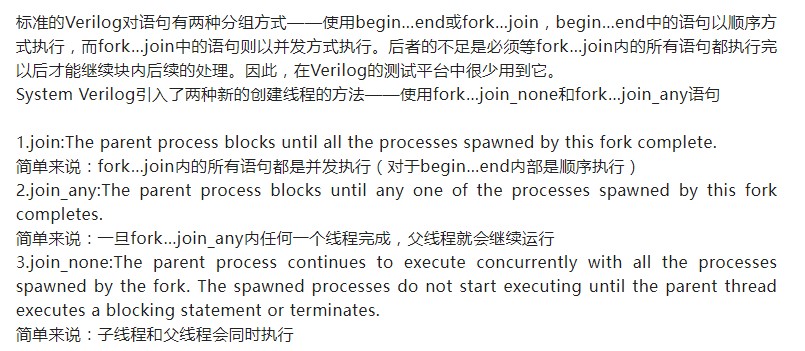

1085 標準的Verilog對語句有兩種分組方式——使用begin…end或fork…join,begin…end中的語句以順序方式執(zhí)行,而fork…join中的語句則以并發(fā)方式執(zhí)行。

2022-09-14 11:02:03 627

627

迭代語句主要用于重復執(zhí)行的程序,在 CoDeSys 中,常見的迭代語句有 FOR,REPEAT 及WHILE 語句。

2023-01-30 17:45:29 1695

1695 在循環(huán)的過程中如果要退出循環(huán),我們可以用break語句和continue語句。

2023-02-23 11:17:43 1853

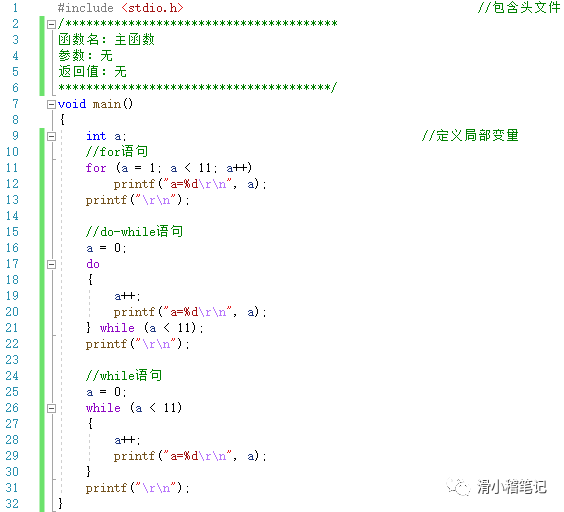

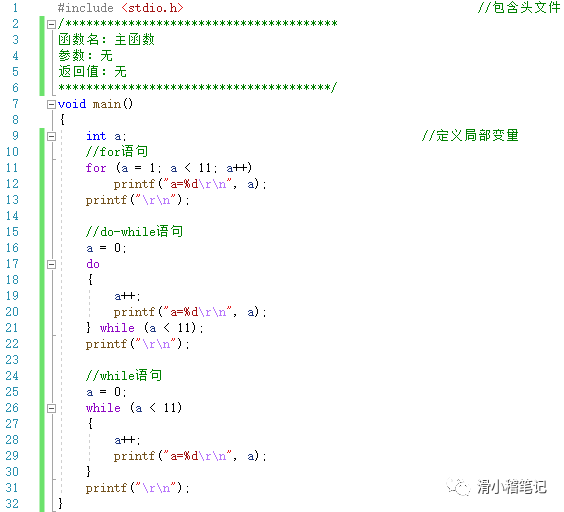

1853 循環(huán)結構是C語言中最后一種結構,常規(guī)中能夠實現(xiàn)循環(huán)效果的語句有while,do-while和for三種,下面采用舉例的方式來說明三種循環(huán)語句

2023-03-02 10:07:51 485

485

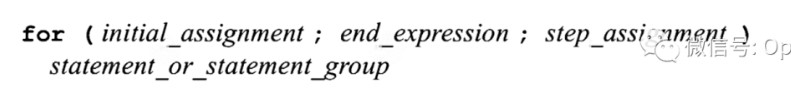

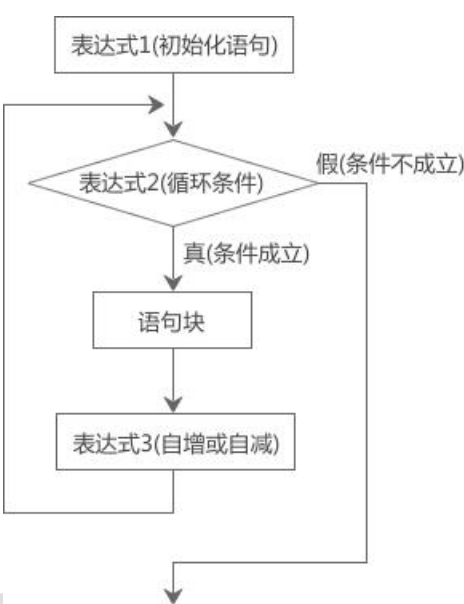

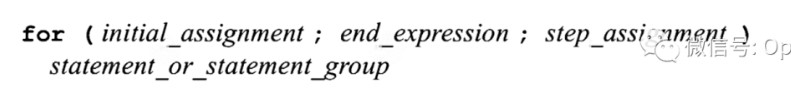

除了可以用while語句和do...while語句實現(xiàn)循環(huán)外,C語言還提供for語句實現(xiàn)循環(huán),而且for語句更為靈活,不僅可以用于循環(huán)次數(shù)已經確定的情況,還可以用于循環(huán)次數(shù)不確定而只給出循環(huán)結束條件的情況,它完成可以代替while語句。

2023-03-09 11:14:19 750

750 一個循環(huán)體內又包含另一個完整的循環(huán)結構,稱為循環(huán)的嵌套。內嵌的循環(huán)體中還可以嵌套循環(huán),這就是多層循環(huán)。

3種常用循環(huán)語句:while語句、do...while語句和for語句可以相互嵌套。

2023-03-09 11:16:15 475

475 在這篇文章中,我們討論了可以在verilog中使用的不同類型的循環(huán) - for循環(huán),while循環(huán),forever循環(huán)和repeat循環(huán)。

2023-04-15 09:19:38 1789

1789 我們在上一篇文章中已經看到了如何使用程序塊(例如 always 塊來編寫按順序執(zhí)行的 verilog 代碼。

2023-04-18 09:45:45 2421

2421 我們在上一篇文章中已經看到了如何使用程序塊(例如 always 塊來編寫按順序執(zhí)行的 verilog 代碼。

我們還可以在程序塊中使用許多語句來控制在我們的verilog設計中信號賦值的方式

2023-05-11 15:37:36 2835

2835

哈嘍大家好,我是知道。今天帶大家了解下Python的循環(huán)語句 定義循環(huán)語句允許我們執(zhí)行一個語句或語句組多次 類型Python提供了兩種不同類型的循環(huán) for循環(huán):重復執(zhí)行語句 #打印1-10for

2023-05-11 17:39:33 595

595 本文主要介紹verilog常用的循環(huán)語句,循環(huán)語句的用途,主要是可以多次執(zhí)行相同的代碼或邏輯。

2023-05-12 18:26:43 1140

1140 綜合就是將HDL語言轉化成與,非,或門等等基本邏輯單元組成的門級連接。因此,可綜合語句就是能夠通過EDA工具自動轉化成硬件邏輯的語句。

2023-06-28 10:39:46 784

784 MATLAB提供了多種條件語句和循環(huán)結構。

2023-07-05 09:41:27 2108

2108 條件語句和循環(huán)語句是計算機編程中常用的兩種控制結構

2023-07-21 16:48:09 5583

5583

條件判斷 語句塊 什么是語句塊呢? 語句塊是在條件為真(條件語句)時執(zhí)行或者執(zhí)行多次(循環(huán)語句)的一組語句。在代碼前放置空格來縮進語句即可創(chuàng)建語句塊。 關于縮進: 使用tab鍵也可以縮進語句

2023-09-12 16:41:56 548

548 循環(huán)控制循環(huán)控制語句可以改變循環(huán)正常的執(zhí)行順序 循環(huán)控制語句 break語句:跳出本次循環(huán)(嵌套循環(huán)中只跳出一層循環(huán)) continue語句:跳過當前一輪循環(huán)體的剩余語句,重新測試循環(huán)狀態(tài),進入下一

2023-09-12 16:59:58 514

514

采用for循環(huán)語句,逐個bit位判斷是否為1,為1則累加,否則保持不變,最終輸出輸入信號中1的數(shù)量。

2023-10-09 16:31:00 1247

1247

單片機中的for語句是一種常見的循環(huán)控制結構,用于重復執(zhí)行一段代碼塊,可以簡化程序的編寫和減少代碼量。本文將詳細介紹單片機中for語句的運用。 一、for語句的基本結構和功能 for語句是一種迭代

2024-01-05 14:02:03 351

351 中的for循環(huán)也是并行執(zhí)行的。 Verilog中的for循環(huán)可以用來實現(xiàn)重復的操作,例如在一個時鐘周期中對多個電路進行操作。在循環(huán)內部,多個語句可以同時執(zhí)行,而不受循環(huán)次數(shù)的限制。這種并行執(zhí)行的機制使得Verilog在硬件設計中非常高效和靈活。 在Verilog中,for循環(huán)有兩

2024-02-22 16:06:23 307

307

電子發(fā)燒友App

電子發(fā)燒友App

評論