聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Xilinx

+關注

關注

73文章

2183瀏覽量

124486 -

Vivado

+關注

關注

19文章

831瀏覽量

68326

發布評論請先 登錄

相關推薦

熱點推薦

如何使用One Spin檢查AMD Vivado Design Suite Synth的結果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synth 的結果(以 Vivado 2024.2 為例)。

Vivado Design Suite用戶指南: 設計分析與收斂技巧

電子發燒友網站提供《Vivado Design Suite用戶指南: 設計分析與收斂技巧.pdf》資料免費下載

發表于 01-15 15:28

?0次下載

Vivado Design Suite用戶指南:邏輯仿真

電子發燒友網站提供《Vivado Design Suite用戶指南:邏輯仿真.pdf》資料免費下載

發表于 01-15 15:25

?0次下載

使用HLS流程設計和驗證圖像信號處理設備

STMicroelectronics成像部門負責向消費者、工業、安全和汽車市場提供創新的成像技術和產品。該團隊精心制定了一套通過模板實現的High-Level Synthesis(HLS)高層次綜合流程,使得上述產品能夠迅速上市。對于汽車市場,該流程符合ISO 26262

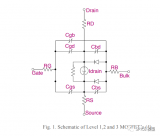

從Level1 Model到Level3 Modle來感受器件模型是如何開發的

? ? ? ?本文從Level1 model到Level3 model的Ids電流公式的發展來感受Compact器件模型是如何開發的。 MOS技術擴展到納米尺寸,帶來了電路模擬器中器件模型的發展

求助,ISO7721用于485隔離遇到的疑問求解

我想選用ISO7721用于485隔離,遇到帶你問題,請幫忙看看。

①看到PDF上描述IIH(High-level input current)最大到10uA,但是MCU SCI TX引腳輸出一般

發表于 12-18 06:30

Xilinx_Vivado_SDK的安裝教程

I Agree,然后點擊 Next: 選擇 Vivado HL System Edition(一般選擇這個設計套件比較完整,它比 Vivado HL Design Edition 多了一個 System Generator for DSP with Mat

每次Vivado編譯的結果都一樣嗎

很多FPGA工程師都有這種困惑,Vivado每次編譯的結果都一樣嗎? 在AMD官網上,有這樣一個帖子: Are Vivado results repeatable for identical

使用Vivado通過AXI Quad SPI實現XIP功能

本博客提供了基于2023.2 Vivado的參考工程,展示如何使用Microblaze 地執行(XIP)程序,并提供一個簡單的bootloader。

Vivado使用小技巧

有時我們對時序約束進行了一些調整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調整

Vivado編輯器亂碼問題

,但是在Vivado里面打開用sublime寫的代碼之后,經常出現中文亂碼,讓人很不舒服。究其原因就是一般來說第三方的編輯器是采用utf8的編碼方式,而vivado的text editor不是這種方式。

如何讓使用JCOM寫入的Overcurrent Trip Level是有效的?

我們使用IMC300的JCOM修改MCE的CompRef暫存器數值, 該暫存器為Overcurrent Trip Level,但是實驗后并未得到預期的效果.

經量測馬達運轉電流約為2A。為了測試

發表于 08-01 08:12

Getting Started with Vivado High-Level Synthesis

Getting Started with Vivado High-Level Synthesis

評論