DDR=Double Data Rate雙倍速率同步動態隨機存儲器。嚴格的說DDR應該叫DDR SDRAM,人們習慣稱為DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的縮寫,即同步動態隨機存取存儲器。本文首先介紹了DDR工作原理及結構圖,其次闡述了DDR DQS信號的處理,具體的跟隨小編一起來了解一下。

DDR工作原理及結構圖

DDR的基本原理

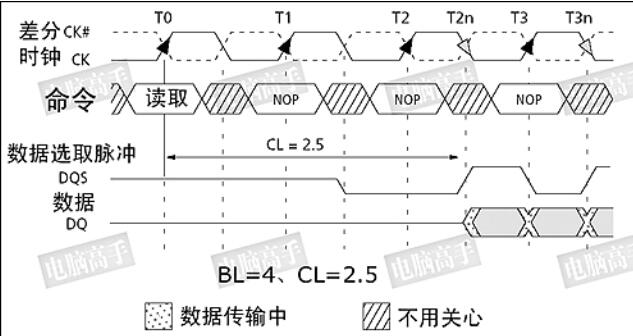

有很多文章都在探討DDR的原理,但似乎也不得要領,甚至還帶出一些錯誤的觀點。首先我們看看一張DDR正規的時序圖。

從中可以發現它多了兩個信號: CLK#與DQS,CLK#與正常CLK時鐘相位相反,形成差分時鐘信號。而數據的傳輸在CLK與CLK#的交叉點進行,可見在CLK的上升與下降沿(此時正好是CLK#的上升沿)都有數據被觸發,從而實現DDR。在此,我們可以說通過差分信號達到了DDR的目的,甚至講CLK#幫助了第二個數據的觸發,但這只是對表面現象的簡單描述,從嚴格的定義上講并不能這么說。之所以能實現DDR,還要從其內部的改進說起。

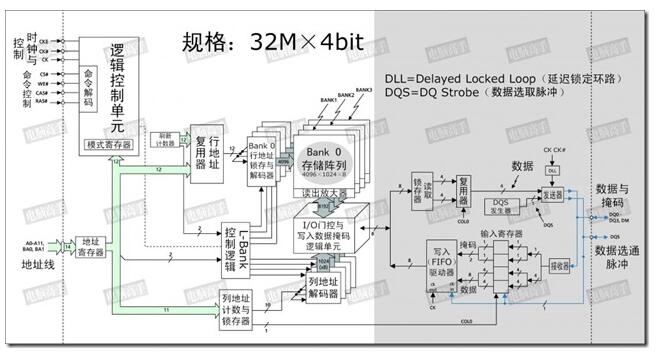

DDR內存芯片的內部結構圖

這是一顆128Mbit的內存芯片,從圖中可以看出來,白色區域內與SDRAM的結構基本相同,但請注意灰色區域,這是與SDRAM的不同之處。首先就是內部的L-Bank規格。SDRAM中L-Bank 存儲單元的容量與芯片位寬相同,但在DDR SDRAM中并不是這樣,存儲單元的容量是芯片位寬的一倍,所以在此不能再套用講解SDRAM時 “芯片位寬=存儲單元容量” 的公式了。也因此,真正的行、列地址數量也與同規格SDRAM不一樣了。

以本芯片為例,在讀取時,L-Bank在內部時鐘信號的觸發下一次傳送8bit的數據給讀取鎖存器,再分成兩路4bit數據傳給復用器,由后者將它們合并為一路4bit數據流,然后由發送器在DQS的控制下在外部時鐘上升與下降沿分兩次傳輸4bit的數據給北橋。這樣,如果時鐘頻率為100MHz,那么在I/O端口處,由于是上下沿觸發,那么就是傳輸頻率就是200MHz。

現在大家基本明白DDR SDRAM的工作原理了吧,這種內部存儲單元容量(也可以稱為芯片內部總線位寬)=2×芯片位寬(也可稱為芯片I/O總線位寬)的設計,就是所謂的兩位預取(2-bit Prefetch),有的公司則貼切的稱之為2-n Prefetch(n代表芯片位寬)。

DDR DQS信號的處理

一、DDR 1&2&3總線概覽

DDR全名為Double Data Rate SDRAM ,簡稱為DDR。現在DDR技術已經發展到了DDR 3,理論上速度可以支持到1600MT/s。DDR總線走線數量多,速度快,操作復雜,探測困難,給測試和分析帶來了巨大的挑戰。

DDR本質上不需要提高時鐘頻率就能加倍提高SDRAM的速度,它允許在時鐘的上升沿和下降沿讀出數據,因而其速度是標準SDRAM的兩倍。至于地址與控制信號則與傳統SDRAM相同,仍在時鐘上升沿進行數據判斷。

目前,許多計算機使用時鐘頻率為533MHz的DDR2內存,更先進的DDR2內存正在日益普及,它的時鐘頻率在400 MHz-800 MHz之間,新的DDR3內存的時鐘頻率則可以工作在800MHz-16OOMHz之間。DDR3內存芯片還有另外一個長處:更低的能耗,它的運行電壓是1.5伏,低于DDR2內存芯片的1.8伏和DDR1內存芯片的2.5伏。在使用電池的設備中能夠延長電池續航時間,因為能耗低,產生的熱量也就少,從而對冷卻的要求也就低一些。

DDR 2&3幾個新增特性的含義是:ODT( On Die Termination),DDR1 匹配放在主板上,DDR2&3把匹配直接設計到DRAM芯片內部,用來改善信號品質。OCD(Off Chip Driver)是加強上下拉驅動的控制功能,通過減小DQS與/DQS(DQS是數據Strobe,源同步時鐘,數據的1和0由DQS作為時鐘來判斷) Skew(時滯)來增加信號的時序容限(Timing Margin)。Posted CAS是提高總線利用率的一種方法。AL(Additive Latency)技術是相對于外部CAS,內部CAS執行一定的延時。

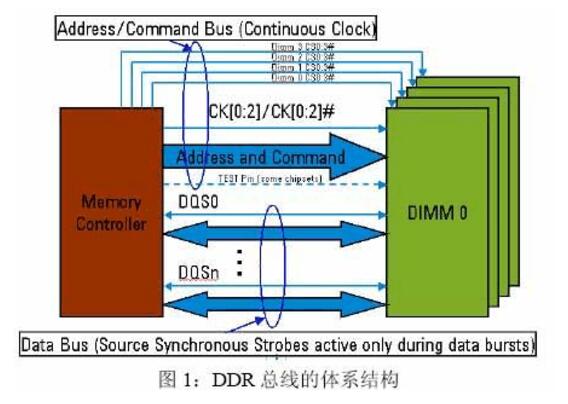

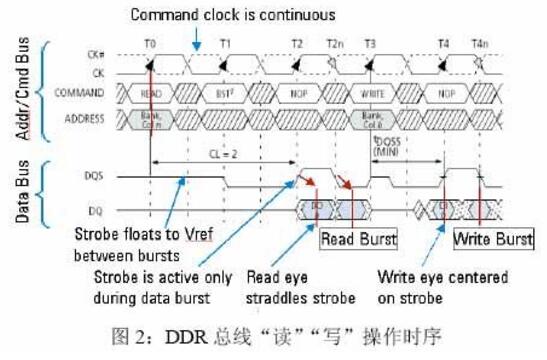

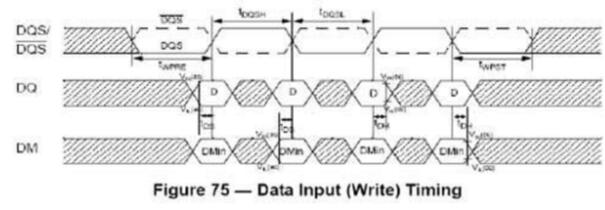

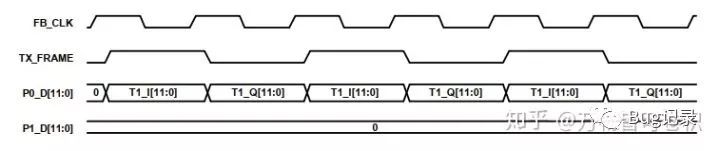

圖1是DDR總線的體系結構。其中DQS是源同步時鐘,在接收端使用DQS來讀出相應的數據DQ,上升沿和下降沿都有效。DDR1總線,DQS是單端信號,而DDR2&3, DQS則是差分信號。DQS和DQ都是三態信號,在PCB走線上雙向傳輸,讀操作時,DQS信號的邊沿在時序上與DQ的信號邊沿處對齊,而寫操作時,DQS信號的邊沿在時序上與DQ信號的中心處對齊,參考圖2,這就給測試驗證帶來了巨大的挑戰:把“讀”信號與“寫”信號分開是非常困難的!

圖2中,Addr/Cmd Bus意思是地址/命令總線,都是時鐘的上升沿有效,其中命令由:/CS(片選),/RAS, /CAS,/WE(寫使能)決定,比如:“讀”命令為:LHLH,“寫”命令為:LHLL等。操作命令很多,主要是NOP(空超作),Active(激活),Write,Read,Precharge (Bank關閉),Auto Refresh或Self Refresh(自動刷新或自刷新)等(細節請參考:Jedec規范JESD79)。Data Bus是數據總線,由DQS的上升沿和下降沿判斷數據DQ的0與1。

二、DDR 1&2&3總線的信號完整性測試

DDR總線PCB走線多,速度快,操作時序復雜,很容易出現失效問題,為此我們經常用示波器進行DDR總線的信號完整性測試和分析,通常的測試內容包括:

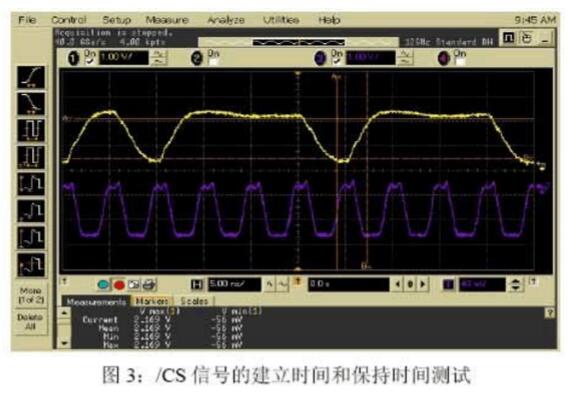

1,命令信號的波形和時序參數:需要測試/RAS,/CAS,/WE,/CS的信號品質,如Vmax(最大電壓值),Vmin(最小電壓值),Slew Rate(斜率),Ringback(回溝)等;還需要測試相對于時鐘邊沿的Setup Time(建立時間)和Hold Time(保持時間)。測試相對于時鐘邊沿的建立時間和保持時間時,需要注意參考電平的位置和最差情況波形的捕獲。如圖3的/CS建立時間和保持時間的測試就沒有測試出最差的建立時間和保持時間值,為此,我們需要用眼圖累積的方式設法找到最差情況下的建立時間和保持時間。

2,地址信號的波形和時序參數:測試內容和測試方質和相對于時鐘邊沿的建立時間和保持時間的測試。

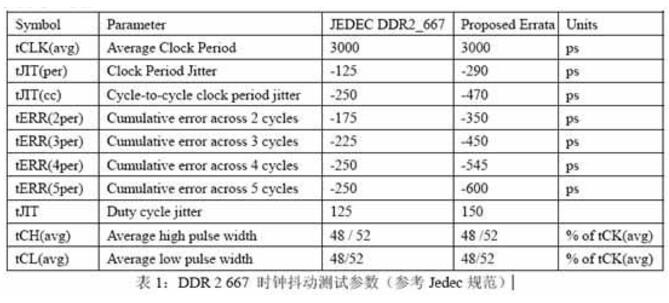

3,時鐘信號的波形和抖動參數:測試建議用差分探頭。波形參數包括overshoot(過沖),undershoot(下沖),Slew Rate(斜率)或Rise Time(上升時間)和Fall Time(下降時間),高低時間和Duty Cycle(占空比失真)等。時鐘抖動一般只是測試Cycle-Cycle Jitter(周期到周期抖動),但是當速率超過533MT/s的DDR2&3時,則測試內容相當多,不可忽略,下表1是DDR2 667的規范參數。這些抖動參數的測試需要用專用軟件實現。

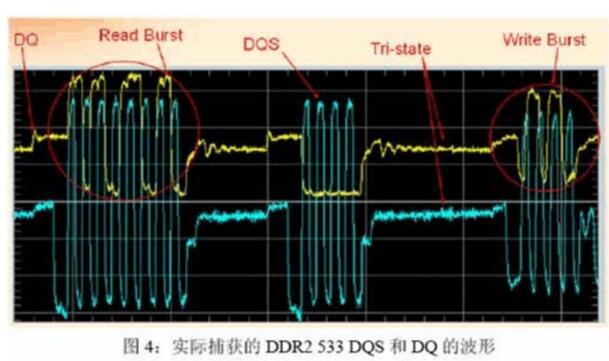

4,速據信號的波形和時序參數:DQS(源同步時鐘)和DQ(數據)波形參數與命令地址測試類似,測試起來比較簡單,但是探測卻比較復雜和困難。DDR1,DQS是單端信號,可以用單端探頭測試,DDR2&3 DQS則是差分信號,建議用差分探頭測試,減小探測難度。DQS和DQ的時序關系,即相對的在不同操作條件下的建立時間和保持時間關系則非常復雜,分析比較困難,圖4是實際捕獲的DDR2 533 DQS和DQ的波形。從圖中可以看出DQS和DQ的三態(Tri-state)特征,讀數據(Read Burst)和寫數據(Write Burst)的DQS和DQ的相對時序特征。在我們測試時,只是捕獲了這樣的波形,然后測試出在“讀”“寫”操作時的建立時間和保持時間參數是不夠的,因為數據碼型是變化的,猝發長度也是變化的,只測了幾個時序參數很難覆蓋各種情況,更難測出最差情況。很多工程師花了一周去測試DDR,仍然測不出問題的關鍵點就在此處。因此我們應該用眼圖的方式去測試DDR的讀寫時序,確保反映整體時序情況和捕獲最差情況下的波形,最好能夠套用串行數據的分析方法,調用模板幫助判斷。

三、DR 1&2&3 “讀”“寫”眼圖測試

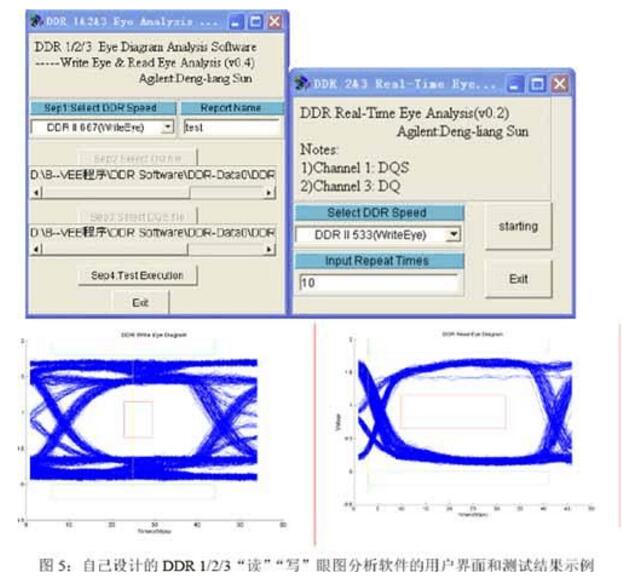

基于DDR“讀”“寫”信號相位不同的特征,本人設計了一個軟件進行“讀”“寫”眼圖的測試分析,軟件使用VEE Pro 7.5設計界面,使用VEE Pro內嵌的Matlab腳本分析數據,基于規范的AC參數設計模板,幫助工程師進行DDR信號完整性測試分析的最復雜部分即“讀” “寫”數據眼圖的測試分析。

圖5是軟件界面和分析結果的一個示例,上面兩福圖形是用戶界面。左邊的是離線分析軟件,用示波器同時采集DQS和DQ信號,并且存為*.CSV文件。采集時,采樣率設置為20GSa/s,存儲深度設置為200k以上,確保捕獲足夠的數據,同時被測系統運行大型的軟件或MemoryTest.exe工具(此內存測試軟件能夠進行內存總線的加壓測試,一般做系統設計的或內存設計的都有),以讓總線上有足夠多的數據,來增加捕獲各種碼型和最差情況的可能性。離線軟件調用采集的波形,自動去掉三態數據,把“讀”數據放在一起,把“寫”數據放在一起,基于DQS的有效邊沿(去掉預調整和后調整后的上升邊沿和下降邊沿),累積在一起形成眼圖,調用模板判斷信號的優劣和是否滿足規范要求。

圖5右上圖是基于Agilent的DSO80000和54850系列示波器的在線實時分析軟件界面。需要把軟件安裝在示波器內部,或安裝在外部電腦上用LAN或GPIB到USB適配器(82357A)連接到示波器。示波器的通道1探測DQS,通道3探測DQ,被測系統上運行大型的軟件或MemoryTest.exe工具。在在線軟件上輸入想重復捕獲波形的次數,然后按“starting”進行實時數據的捕獲和實時眼圖的分析,軟件會控制示波器捕獲波形,然后分析數據,形成眼圖,調用模板判斷信號是否滿足規范要求,然后重復下一次捕獲和分析,同時把新捕獲的波形累積到前面捕獲的波形上面。在線軟件執行的算法與離線軟件類似,只是可以自動控制示波器,進行波形的多次捕獲和分析,并同時把實時捕獲的波形的分析結果連同以前的結果一同顯示出來。

圖5下面的兩個波形是實際的分析結果示例,分析的是DDR2 667,測試點是在DIMM內存條上。對我們比較有意義的是左邊的“寫”眼圖,它反映的是信號從北橋發出,通過主板較長距離傳輸到達DRAM接收芯片的波形,這是我們做系統設計和測試時需要得到的眼圖。右圖則是直接從DRAM芯片發出的信號的波形,因為測試點是在DIMM上,所以對我們只有參考價值:當在北橋測試出時序問題時,通過此波形的觀察確定是主板設計的問題,還是DIMM或DRAM芯片本身的問題。如果測試點在北橋,則我們需要關注“讀”眼圖,而此時“寫”眼圖一般只有參考價值。

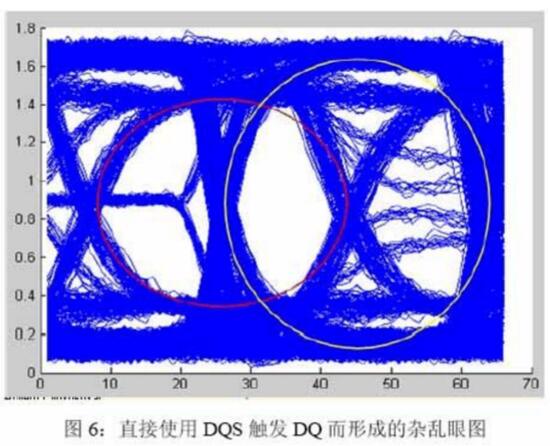

這個DDR“讀”“寫”眼圖分析軟件的算法是什么呢?其實很簡單,如圖6所示,如果直接用DQS觸發DQ,則會形成比較亂的眼圖,但是中間又包括需要的信息,如圖中的紅色圓圈周圍的是“寫”眼圖信息,途中的黃色圓圈周圍則是“讀”眼圖信息。而眼圖之所以亂,是因為同時包括“三態”信號和“讀”“寫”信號,而“讀” 和“寫”信號的時序是矛盾的。使用 軟件進行分離的處理比較容易:首先,扔掉三態信號,保留有用信息,軟件設計時,檢測DQS有效邊沿,離DQS有效邊沿較遠的信號就是三態信號,扔掉它;然后,根據建立時間和保持時間的關系把“讀”信號和“寫”信號分成兩個數據庫;最后,把“讀”信號數據庫按DQS有效邊沿放在一起形成眼圖,把“寫”信號數據庫按DQS有效邊沿放在一起形成眼圖,分別調用模板產生測試結果。

四、DDR 1&2&3 模板定義

DDR規范沒有定義模板,這給用眼圖方式分析信號時判斷信號是否滿足規范要求帶來挑戰。為了更容易判斷是否滿足規范的要求,像分析一般串行信號一樣分析“讀”“寫”眼圖,本人根據Jedec規范設計了“讀”“寫”模板。下面以定義“寫”眼圖模板為例,介紹一下模板的設計方法。

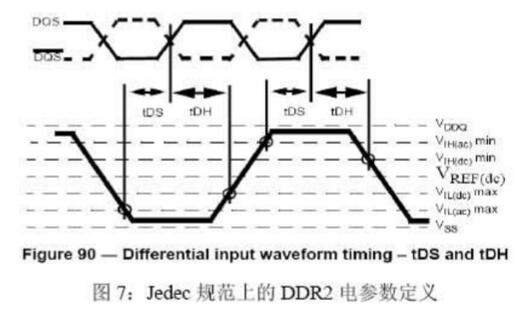

圖7是Jedec規范上的時序和波形參數,tDS是相對于DQS有效邊沿的建立時間,tDH是相對于DQS有效邊沿的保持時間,tDS相對于DQ的AC參數,tDH則相對于DQ的DC參數,不過為了測試方面的方便性,我們都可以用AC參數來定義tDS和tDH。tDS和tDH參數的測試是DDR的核心測試參數。

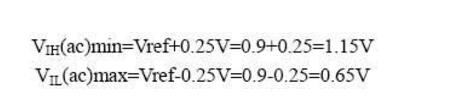

在Jedec規范上,我們可以查到各種速率的tDS和tDH 的規范值,比如DDR2 533,tDS 是100ps,tDH 是225ps。我們也可以查到各種速率的AC參數值,比如DDR2 533:其中,VIH(ac)min是VIH(ac)規范的最小值,VIL(ac)max是VIL(ac)規范的最大值,Vref是參考電壓,對DDR1來說是1.25V,DDR2來說是0.9V,DDR3來說是0.75V。

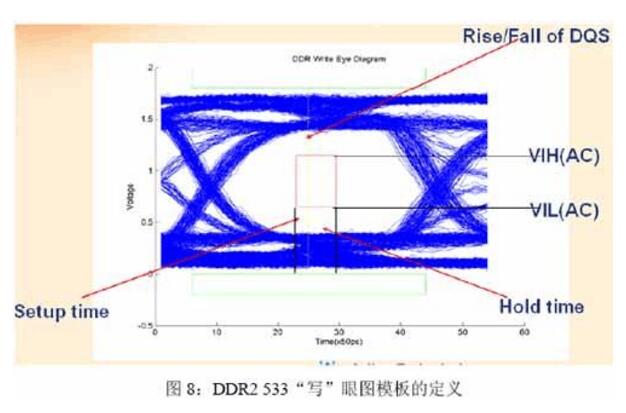

基于tDS和tDH 和VIH(ac)min和VIL(ac)max參數,我們可以得出DDR2 533“寫”眼圖的模板如圖8示。中間的紅色區域就是模板,Setup time是tDS建立時間,Hold time是tDH 保持時間,VIH(AC)是VIH(ac)min值,VIL(AC)是VIL(ac)max值。中間的黃色線是DQS的有效邊沿即有效的上升沿或下降沿。

嚴格按規范的話,中間的模板應該定義為橫著的梯形,因為保持時間是相對于DC參數,不過用長方形可以定義一個更嚴格的參數要求。

五、小結

DDR是需要進行信號完整性測試的總線中最復雜的總線,不僅走線多、探測困難,而且時 序復雜,各種操作交織在一起。本文基于多年的實踐經驗,提供了一些測試的參考方法,尤其對 “讀”“寫”眼圖的測試方法和模板的定義提出一種創新的觀點,并設計軟件實現了這種方法,希望對主板,DIMM,DRAM設計者和測試者有參考價值。

-

DDR

+關注

關注

11文章

731瀏覽量

66501 -

dqs

+關注

關注

0文章

7瀏覽量

2400

發布評論請先 登錄

可制造性案例│DDR內存芯片的PCB設計!

可制造性案例│DDR內存芯片的PCB設計

關于DDR的PCB設計

DDR總線的體系結構

映射期間出錯:DDR2

Interfacing DDR &DDR2 SDRAM wi

DDR工作原理

DDR怎么學習,從仿真開始

DDR和DDR2與DDR3的設計資料總結

DDR工作原理_DDR DQS信號的處理

DDR工作原理_DDR DQS信號的處理

評論