設計背景:

狀態(tài)機是描述各種復雜時序的時序行為,是使用HDL進行數(shù)學邏輯設計中非常重要的方法之一,狀態(tài)機分為摩爾機和米粒機,當輸出只和狀態(tài)有關(guān)系的話稱為摩爾機,當輸出不僅和狀態(tài)有關(guān)系也和輸入信號有關(guān)系的時候稱為米粒機,米粒機和摩爾機的電路原型我就不在這里給大家介紹了。

狀態(tài)機是由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預先設計的狀態(tài)進行狀態(tài)的轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號的動作,完成特定操作的控制中心。比如我們生活中遇到的問題,健康---感冒---健康,這個就是一個狀態(tài)的轉(zhuǎn)移圖,從健康狀態(tài)到感冒狀態(tài)在到健康狀態(tài)。

設計原理:

我認為對于我們初學者來說我們只要只要狀態(tài)機就是當這個狀態(tài)也就是當這個時鐘來的時候發(fā)生這件事情,當下各時鐘來的時候發(fā)生另一件事,也就是說發(fā)生這件事后,跳轉(zhuǎn)下一個時鐘發(fā)生另一件事情,兩個事情發(fā)生沒有關(guān)系。我們理解初學者理解這個就行了,不用理解高深的二段式,三段式。

我們會在下面的設計中用到簡單的狀態(tài)機讓大家明白簡單的狀態(tài)機。

我們的設計也是一個流水燈,我們的設計是在復位的時候讓4個等全熄滅,第一個上升沿點亮一個,第二個點亮下一個,依次類推。

我們的寫法可以這樣想,當?shù)谝粋€狀態(tài)也就是一個上升沿點亮第一個燈,然后跳轉(zhuǎn)下一個狀態(tài)點亮第二個燈,第三個點亮下一個。。。。

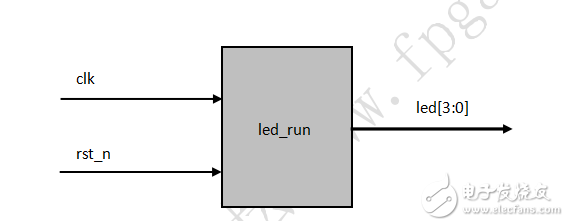

設計架構(gòu)圖:

?

?

設計代碼:

設計模塊

0moduleled_run (clk,rst_n,led);

1

2 inputclk,rst_n; //定義輸入輸出

3

4 outputreg[3:0]led;

5

6 reg[10:0]count; //定義一個時間寄存器

7 regclk_1hz; //定義一個時鐘

8 reg[1:0]state;//定義狀態(tài)

9

10 always@(posedgeclk)

11 if(!rst_n)

12 begin

13 clk_1hz <=1;

14 count <=0;

15 end

16 elseif(count <(5/1/2-1))//計數(shù)來產(chǎn)生一個時鐘

17 count <=count +1'd1;

18 else

19 begin

20 count <=26'd0;

21 clk_1hz <=~clk_1hz;

22 end

23

24 always@(posedgeclk_1hz)

25 if(!rst_n)

26 led <=4'b1111; //復位熄滅4個燈

27 else

28 case(state)

29 0 : begin //第一個狀態(tài)點亮第一個燈,然后跳轉(zhuǎn)下 一個狀態(tài)

30 state <=1;

31 led <=4'b1110;

32 end

33

34 1 : begin //第2個狀態(tài)點亮第2個燈,然后跳轉(zhuǎn)下 一個狀態(tài)

35 state <=2;

36 led <=4'b1101;

37 end

38

39 2 : begin //第3個狀態(tài)點亮第3個燈,然后跳轉(zhuǎn)下 一個狀態(tài)

40 state <=3;

41 led <=4'b1011;

42 end

43 3 : begin //第4個狀態(tài)點亮第4個燈,然后跳轉(zhuǎn)0狀態(tài)

44 state <=0;

45 led <=4'b0111;

46 end

47

48 default:state <=0;//否則跳轉(zhuǎn)0狀態(tài)

49 endcase

50

51endmodule

測試模塊

0`timescale1ns/1ps//例化時標

1

2moduletb();

3

4 regclk,rst_n;

5 wire[3:0]led;

6

7 initialbegin

8

9 clk =1;

10 rst_n =0;

11

12 #200.1rst_n =1;

13

14

-

FPGA

+關(guān)注

關(guān)注

1643文章

21971瀏覽量

614315 -

狀態(tài)機

+關(guān)注

關(guān)注

2文章

493瀏覽量

28079

發(fā)布評論請先 登錄

FPGA工程師:如何在FPGA中實現(xiàn)狀態(tài)機?

明德?lián)P視頻分享--點撥FPGA課程---第十四章 狀態(tài)機設計

FPGA---如何寫好狀態(tài)機,詳細下載pdf

一個簡單的狀態(tài)機設計

狀態(tài)機設計

高速環(huán)境下FPGA或CPLD中的狀態(tài)機設計

VHDL有限狀態(tài)機設計-ST

FPGA之狀態(tài)機設計原則

如何在FPGA中實現(xiàn)狀態(tài)機

基于FPGA的狀態(tài)機設計

FPGA學習系列:9.簡單狀態(tài)機設計

FPGA學習系列:9.簡單狀態(tài)機設計

評論