所有的Wishbone接口信號(hào)都是高電平有效,設(shè)計(jì)成高電平有效的主要原因是由于低電平有效信號(hào)的書寫問題,不同的設(shè)計(jì)者表達(dá)低電平有效信號(hào)的方式不同,拿最常見的低電平有效的復(fù)位信號(hào)來說,其表示方法就有_RST_I、N_RST_I、#RST_I和/RST_I,而高電平有效的信號(hào)其表達(dá)方式通常只有一種。

所有的Wishbone接口信號(hào)都以_I或者_(dá)O結(jié)束。_I表示輸入,_O表示輸出。()表示該信號(hào)為總線信號(hào),總線的寬度可以為1,也可以為大于1的任何值。

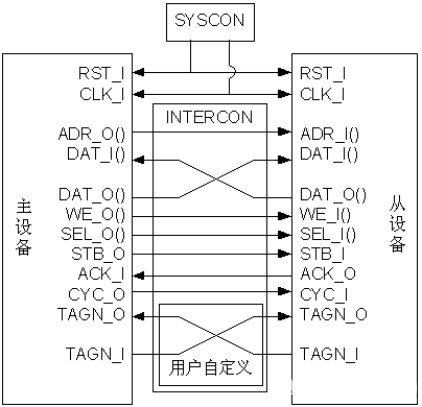

圖5Wishbone總線規(guī)范中使用的主要信號(hào)(一個(gè)點(diǎn)到點(diǎn)互聯(lián)的例子)

在圖5中,主設(shè)備具有遵守Wishbone規(guī)范的主設(shè)備接口,從設(shè)備具有遵守Wishbone規(guī)范的從設(shè)備接口,INTERCON模塊將主設(shè)備和從設(shè)備的對(duì)應(yīng)數(shù)據(jù)、地址和控制線連接起來,SYSCON模塊提供時(shí)鐘和復(fù)位信號(hào),這兩個(gè)信號(hào)被送入主設(shè)備和從設(shè)備。

圖5給出了Wishbone接口的常見信號(hào),這些信號(hào)有些是必須的,有些是可選的。這些信號(hào)的基本功能描述如下: (說明:下面各個(gè)信號(hào)默認(rèn)前面的為主機(jī)信號(hào),后面的為從機(jī)信號(hào)!)

CLK_O/CLK_I:時(shí)鐘信號(hào)。時(shí)鐘信號(hào)由SYSCON模塊產(chǎn)生,并送入各個(gè)主設(shè)備和從設(shè)備。SYSCON通常內(nèi)部存在一個(gè)鎖相環(huán),將來源于芯片外的晶體振蕩器或者時(shí)鐘輸入信號(hào)整形、分頻或者倍頻為芯片內(nèi)所需要的時(shí)鐘信號(hào)。所有Wishbone信號(hào)都同步到時(shí)鐘信號(hào)上,包括復(fù)位信號(hào)。

RST_O/RST_I:同步復(fù)位信號(hào),高電平有效。復(fù)位信號(hào)由SYSCON模塊產(chǎn)生,并送入各主設(shè)備及從設(shè)備。 復(fù)位后,Wishbone內(nèi)所有的自啟動(dòng)狀態(tài)機(jī)被強(qiáng)制進(jìn)入初始狀態(tài)。

DAT_O()/DAT_I():主設(shè)備和從設(shè)備的之間的數(shù)據(jù)信號(hào),數(shù)據(jù)可以由主設(shè)備傳送給從設(shè)備,也可以由從設(shè)備傳送給主設(shè)備。一對(duì)主設(shè)備和從設(shè)備之間最多存在兩條數(shù)據(jù)總線,一條用于主設(shè)備向從設(shè)備傳輸數(shù)據(jù),另外一條用于從設(shè)備向主設(shè)備傳輸數(shù)據(jù)。Wishbone規(guī)定數(shù)據(jù)總線的最大寬度為64位,這一規(guī)定實(shí)際上是考慮到目前商用處理器的最大位數(shù)為64,實(shí)際上數(shù)據(jù)總線的寬度可以是任意值。就發(fā)展情況來看,在64位處理器以后,處理器將向多核方向發(fā)展,總線將向高速串行方向發(fā)展。

TGD_O/TGD_I():TGD_O/TGD_I()為數(shù)據(jù)標(biāo)簽,具體講是附加于在數(shù)據(jù)總線DAT_O()/DAT_I()的標(biāo)簽,該標(biāo)簽可以用于傳送關(guān)于數(shù)據(jù)總線的額外信息如奇偶校驗(yàn)信息、錯(cuò)誤糾正和時(shí)間戳信息等。任何作者在設(shè)計(jì)兼容Wishbone總線接口的IP時(shí),都應(yīng)在其使用手冊(cè)注明數(shù)據(jù)標(biāo)簽的名稱和使用方法。

ADR_O(n..m)/ADR_I(n..m):地址信號(hào),主設(shè)備輸出地址到從設(shè)備。n取決于IP核的地址寬度,m取決于數(shù)據(jù)總線DAT_O()/DAT_I()的寬度和粒度。數(shù)據(jù)總線的粒度指的是數(shù)據(jù)總線能夠一次傳送的最小比特?cái)?shù),很多處理器如ARM的數(shù)據(jù)總線的粒度為1個(gè)字節(jié),但是也有一些處理器如CEVA TeakLite DSP的數(shù)據(jù)總線粒度為2個(gè)字節(jié)。一個(gè)位寬為32比特、粒度為1個(gè)字節(jié)的數(shù)據(jù)總線的地址信號(hào)應(yīng)定義為ADR_O(n..2)/ADR_I(n..2)。在傳送數(shù)據(jù)時(shí),具體哪些字節(jié)有效通過SEL_O()/SEL_I()信號(hào)(見下文)控制。在某些特定的場(chǎng)合(比如FIFO接口),這一信號(hào)可能不會(huì)出現(xiàn)在接口上。

CYC_O/CYC_I:總線周期信號(hào)CYC_O/CYC_I有效代表一個(gè)主設(shè)備請(qǐng)求總線使用權(quán)或者正在占有總線,但是不一定正在進(jìn)行總線操作(是否正在進(jìn)行總線操作取決于選通信號(hào)STB_O/STB_I是否有效)。只有該信號(hào)有效,Wishbone主設(shè)備和從設(shè)備接口的其它信號(hào)才有意義。CYC_O/CYC_I信號(hào)在一次總線操作過程中必須持續(xù)有效,比如一次塊讀操作可能需要多個(gè)時(shí)鐘周期,CYC_O/CYC_I信號(hào)必須保持持續(xù)有效。實(shí)際上,該信號(hào)的實(shí)際作用等同于其他總線標(biāo)準(zhǔn)中的仲裁申請(qǐng)信號(hào)。當(dāng)存在多個(gè)主設(shè)備時(shí),它們可能希望同時(shí)進(jìn)行總線操作,主設(shè)備通過仲裁申請(qǐng)信號(hào)向仲裁器申請(qǐng)總線占有權(quán),仲裁器通過一定的仲裁優(yōu)先級(jí)邏輯向其中一個(gè)選定的主設(shè)備發(fā)送總線允許信號(hào)GNT_O()/GNT_I,表示該主設(shè)備可以占用總線。

STALL_I/STALL_O:該信號(hào)用于流水線模式。流水線停止輸入表示,當(dāng)前從機(jī)不能接受來自轉(zhuǎn)換隊(duì)列中的傳輸信號(hào)。

LOCK_O/LOCK_I:在操作過程中,仲裁器可能會(huì)提前將總線占用權(quán)收回并分配給其他主設(shè)備從而打斷當(dāng)前主設(shè)備的操作,LOCK_O/LOCK_I有效代表本次總線操作是不可打斷的。仲裁器收到LOCK_I信號(hào),就不會(huì)提前收回總線使用權(quán),知道當(dāng)前主機(jī)將該信號(hào)拉低。圖5中只有一個(gè)主設(shè)備和一個(gè)從設(shè)備,因此沒畫出仲裁器模塊。

SEL_O()/SEL_I():有效數(shù)據(jù)總線選擇信號(hào),標(biāo)識(shí)當(dāng)前操作中數(shù)據(jù)總線上哪些比特是有效的,以總線粒度為單位。SEL_O()/SEL_I()的寬度為數(shù)據(jù)總線寬度除以數(shù)據(jù)總線粒度。比如,在一個(gè)8位粒度的64位端口上,信號(hào)可以被分為8個(gè)部分,即SEL_O(7..0)。每一位信號(hào)與對(duì)應(yīng)的字節(jié)相關(guān)。再比如,一個(gè)具有32位寬、粒度為1個(gè)字節(jié)的數(shù)據(jù)總線的選擇信號(hào)應(yīng)定義為SEL_O(3:0)/ SEL_I(3:0),SEL(4’b1001)代表當(dāng)前操作中數(shù)據(jù)總線的最高和最低字節(jié)有效。具體會(huì)在后面的博文中進(jìn)行詳細(xì)介紹。

STB_O/STB_I:選通信號(hào)。選通有效代表主設(shè)備發(fā)起一次總線操作。只有選通信號(hào)有效(此時(shí)CYC_O/CYC_I也必須為高),ADR_O/ADR_I()、DAT_O()/DAT_I()、SEL_O()/SEL_I()才有意義。在Wishbone總線規(guī)范中,CYC_O/CYC_I是最高層的控制信號(hào),只有該信號(hào)有效,STB_O/STB_I信號(hào)才有意義。一個(gè)信號(hào)有意義是指該信號(hào)的當(dāng)前值是需要主設(shè)備或者從設(shè)備解釋的,0為無效,1為有效,而一個(gè)信號(hào)沒有意義是指該信號(hào)的當(dāng)前值主設(shè)備和從設(shè)備不必關(guān)心,是0還是1都無效。

TGA_O()/TGA_I():TGA_O/TGA_I()為地址標(biāo)簽,具體講是附加于在地址總線ADR_O()/ADR_I()的標(biāo)簽,該標(biāo)簽可以用于傳送關(guān)于地址總線的額外信息如地址總線寬度信息(如24位、32位等 )、存儲(chǔ)器保護(hù)信息(protected or unprotected)等。Wishbone只規(guī)定了TGD_O/TGD_I和TGA_O()/TGA_I()的接口時(shí)序,用戶可以定義TGD_O/TGD_I的具體含義。 任何作者在設(shè)計(jì)兼容Wishbone總線接口的IP時(shí),都應(yīng)在其使用手冊(cè)注明地址標(biāo)簽的名稱和使用方法。

TGC_O/TGC_I():TGC_O/TGC_I()為總線周期標(biāo)簽,該標(biāo)簽可以用于傳送關(guān)于當(dāng)前總線周期所進(jìn)行操作的描述如操作類型(包括單次操作、塊操作、RMW操作)、中斷應(yīng)答類型、緩存操作類型等。類似的,Wishbone只規(guī)定了TGC_O/TGC_I()的接口時(shí)序,用戶可以定義TGD_O/TGD_I的具體含義。 任何作者在設(shè)計(jì)兼容Wishbone總線接口的IP時(shí),都應(yīng)在其使用手冊(cè)注明總線周期標(biāo)簽的名稱和使用方法。

WE_O/WE_I:寫使能信號(hào),代表當(dāng)前周期中進(jìn)行的操作是寫操作還是讀操作。1代表寫,0代表讀。

ACK_I/ACK_O、ERR_I/ERR_O、RTY_I/RTY_O:主從設(shè)備間的操作結(jié)束方式信號(hào)。ACK表示成功,ERR表示錯(cuò)誤,RTY表示重試(Retry)。操作總是在某一總線周期內(nèi)完成的,因此操作結(jié)束方式也稱為總線周期結(jié)束方式。成功是操作的正常結(jié)束方式,錯(cuò)誤表示操作失敗,造成失敗的原因可能是地址或者數(shù)據(jù)校驗(yàn)錯(cuò)誤,寫操作或者讀操作不支持等。重試表示從設(shè)備當(dāng)前忙,不能及時(shí)處理該操作,該操作可以稍后重新發(fā)起。接收到操作失敗或者重試后,主設(shè)備如何響應(yīng)取決于主設(shè)備的設(shè)計(jì)者。

-

接口

+關(guān)注

關(guān)注

33文章

8694瀏覽量

151928 -

信號(hào)

+關(guān)注

關(guān)注

11文章

2807瀏覽量

77113 -

Wishbone

+關(guān)注

關(guān)注

0文章

16瀏覽量

10444

原文標(biāo)題:【博文連載】Wishbone接口信號(hào)定義

文章出處:【微信號(hào):ChinaAET,微信公眾號(hào):電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于WISHBONE總線的FLASH閃存接口設(shè)計(jì)

PWM的輸入是高電平有效還是低電平有效的?

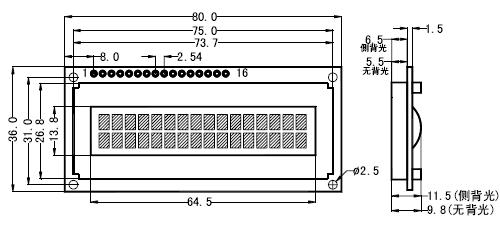

SMC1602的封裝尺寸及接口信號(hào)說明

基于WISHBONE總線的FLASH閃存接口設(shè)計(jì)

CAN總線接口信號(hào)隔離收發(fā)IC

邏輯芯片輸入的低電平有效和高電平有效

電子設(shè)計(jì)(4)高電平、低電平復(fù)位電路

HDMI模塊接口概念及接口信號(hào)定義介紹

龍迅HDMI接口信號(hào)轉(zhuǎn)換的應(yīng)用案例

Wishbone接口信號(hào)都是高電平有效

Wishbone接口信號(hào)都是高電平有效

評(píng)論