坐在上海回北京的高鐵上,漫長的旅途著實(shí)讓人感到無聊(沒買到直達(dá)的高鐵,只能慢悠悠的走一站停一站,暈,都高鐵時(shí)代了,竟然還這樣,想起了大學(xué)放假回家站十幾個(gè)小時(shí)綠皮車的時(shí)光啊,哈哈),遂有點(diǎn)“寫心萌動(dòng)”,不由感嘆——“春”天真是來了,春為啥加引號捏,我相信大家都懂的,哈哈。這樣也好,俺又可以慢悠悠的寫作抒情了,走著。。。

其實(shí)都搞了這么長時(shí)間的ARM開發(fā),關(guān)于其至關(guān)重要的中斷優(yōu)先級問題我早就想跟大家伙分享分享了,可惜一方面想真正的講清楚這個(gè)問題估計(jì)又得大費(fèi)周章和墨水,另一方面自己越來越忙進(jìn)一步導(dǎo)致寫文章倒是越來越懶了,呵呵。所以趁著坐高鐵無聊趕緊擼胳膊抹袖子整吧,不然把這么重要的內(nèi)容放在自己腦子里封存落灰實(shí)在是頗為浪費(fèi)呀,哈哈。那就不多扯淡了,再多扯火車到站了就尷尬了,咳咳。。。

對于中斷優(yōu)先級配置的需求實(shí)際上主要體現(xiàn)在系統(tǒng)存在多個(gè)可能的中斷源情況下,這時(shí)為了保證代碼的可靠執(zhí)行,我們不得不考慮很現(xiàn)實(shí)的兩個(gè)問題,一個(gè)是如果兩個(gè)以上中斷同時(shí)發(fā)生,pending請求到CPU,CPU決策該先進(jìn)哪一個(gè)相應(yīng)的中斷服務(wù)Routine,第二個(gè)問題是CPU當(dāng)前已經(jīng)在響應(yīng)某個(gè)中斷服務(wù),此時(shí)來了另一個(gè)中斷請求,是否允許其打斷當(dāng)前中斷服務(wù)轉(zhuǎn)而響應(yīng)新的中斷請求即我們常說的中斷嵌套問題,不要告訴我沒考慮過哈(如果真是這樣,我只能不客氣的說,這樣搞單片機(jī)是不負(fù)責(zé)任的,很可能給項(xiàng)目帶來潛在的風(fēng)險(xiǎn)bug),那樣的話俺也白寫了,呵呵。那正題來了,對現(xiàn)在紅紅火火的ARM Cortex-M4和M0+兩個(gè)核來說,他們是如何解決這兩個(gè)問題的呢,因?yàn)檫@兩個(gè)核在中斷優(yōu)先級管理上略有些區(qū)別(雖然都是NVIC和SCB兩個(gè)寄存器來管理),所以下面我分開來說,另外由于中斷優(yōu)先級管理屬于內(nèi)核問題,所以這方面的信息你不會在各大半導(dǎo)體廠家的官方手冊中找到,我們只能追根溯源直接到內(nèi)核的老家ARM官網(wǎng)去找,建議大家有興趣的到ARM官網(wǎng)把M4和M0+的內(nèi)核手冊下載下來簡單瞅瞅,可能會有意想不到的收獲哦,呵呵:

ARM Cortex-M0+中斷優(yōu)先級和嵌套

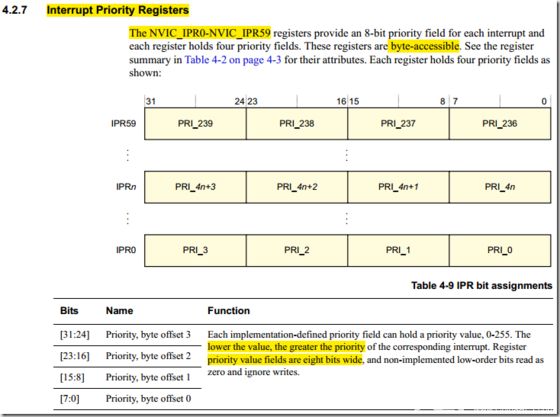

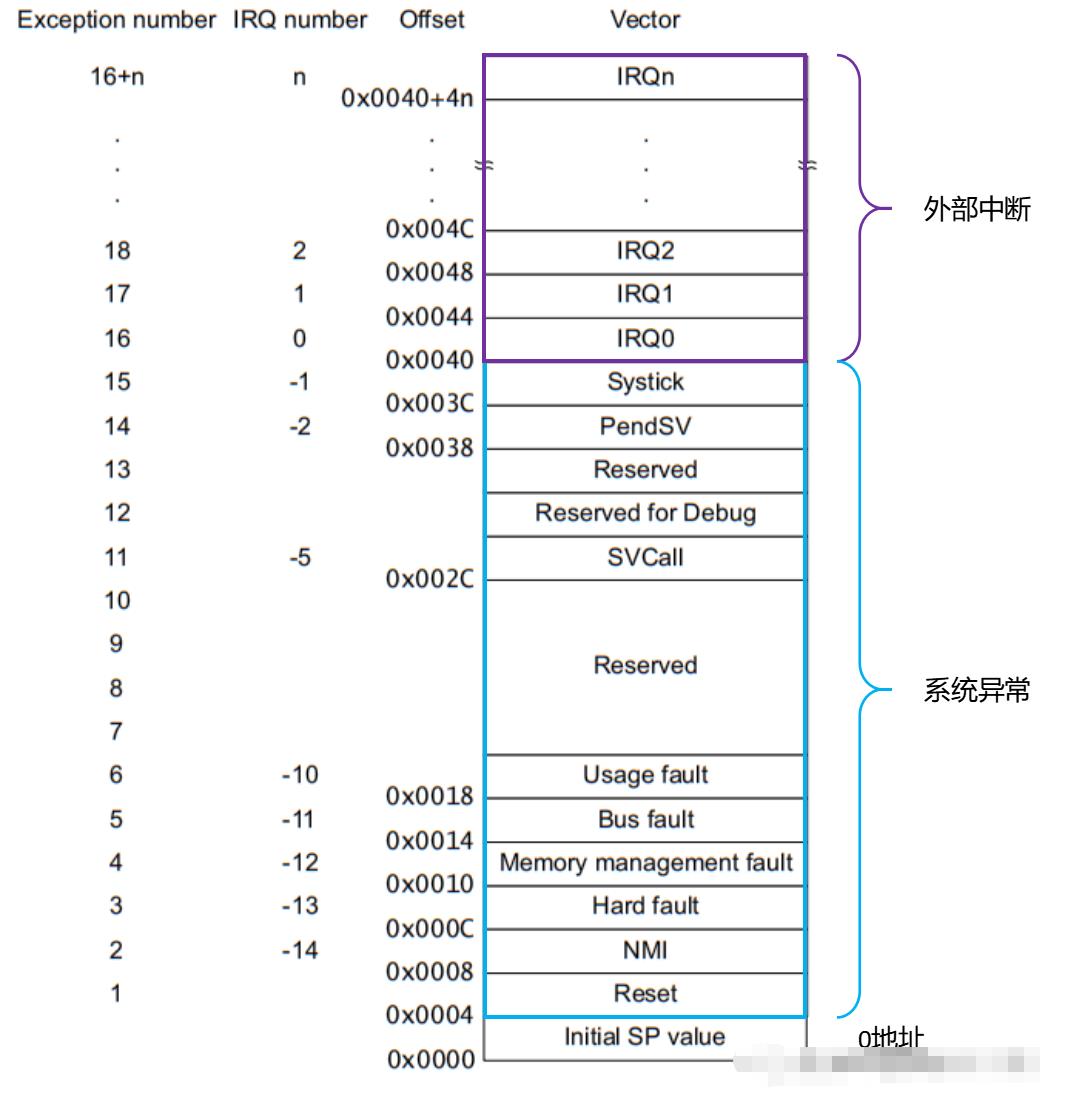

無論是M0+或者是M4內(nèi)核,實(shí)際上他們兩個(gè)的中斷優(yōu)先級都是由NVIC和SCB兩個(gè)寄存器來管理的,在這里我默認(rèn)大家都知道ARM的中斷源分為內(nèi)核中斷和IRQ中斷了哈(我怕再細(xì)講下去又沒完了,呵呵),而對IRQ的中斷管理是由NVIC來主導(dǎo)的,內(nèi)核的中斷管理則是由SCB來主導(dǎo)的,我們先講IRQ中斷的優(yōu)先級問題(關(guān)于中斷使能和禁能不在本篇討論范圍內(nèi)哈),打開M0+的內(nèi)核手冊找到NVIC_IPR寄存器(Interrupt Priority Registers)如下圖所示:

注意觀察我高亮標(biāo)注的幾塊,從這幾塊中可以抽象出核心的幾個(gè)問題,第一個(gè)是NVICIPR一共有8個(gè)寄存器,而每個(gè)寄存器管理4個(gè)IRQ中斷,乘法口訣算一下,我們就明白了為啥M0+的IRQ中斷源最多只支持32個(gè)了,再加上16個(gè)內(nèi)核中斷,加法口訣再算一下,也就是說M0+最多就是48個(gè)中斷源,所以M0+算是比較好搞的了,一會兒講M4就該頭疼了,呵呵;第二個(gè)問題是優(yōu)先級寄存器里面的配置值越低表明相應(yīng)的中斷優(yōu)先級越高;第三個(gè)問題是每個(gè)PRIxx的8位中只有最高兩位[7:6]有效,也就是說實(shí)際上M0+的優(yōu)先級只有四個(gè)即0,1,2,3,4,其中0的優(yōu)先級是最高的;第四個(gè)問題,為啥我放到最后說呢,因?yàn)檫@是比較容易忽略的問題,即word-accessible,也就是說這幾個(gè)寄存器都只能按字操作,切記不要為了顯示我們的編程技巧而使用指向字節(jié)的指針只對某個(gè)單獨(dú)中斷的優(yōu)先級進(jìn)行配置。

至于嵌套的問題,對M0+是比較簡單的,即只要相應(yīng)中斷的優(yōu)先級比較高即可隨時(shí)搶占比它優(yōu)先級低的中斷服務(wù)。至于內(nèi)核中斷,其中斷優(yōu)先級則由SCB模塊的SCB_SHPR寄存器來管理如下圖所示,實(shí)際上我們平時(shí)常用的就是systemtick中斷,其優(yōu)先級配置同NVIC,這里就不贅述了。另外,我這里提一下,即如果我們不對優(yōu)先級進(jìn)行配置的話,則默認(rèn)相應(yīng)中斷源的向量號越低其優(yōu)先級越高,不過如前面我提到的,我是強(qiáng)烈建議在多中斷的情況最好把每個(gè)用到的中斷優(yōu)先級都根據(jù)實(shí)際需求進(jìn)行相應(yīng)配置,避免潛在的風(fēng)險(xiǎn)。

ARM Cortex-M4中斷優(yōu)先級和嵌套

我前面提到一句,M4雖然指令集是向下兼容M0+的,但是在中斷優(yōu)先級管理上是有區(qū)別的,由于M4的中斷源比較多(最多允許256),所以其對中斷優(yōu)先級管理是略有些復(fù)雜的,不過一定要仔細(xì)看下去,因?yàn)槲覀兤綍r(shí)會比較常用到,但是我敢肯定不是所有人的用法是正確的,為啥?待我下面繼續(xù)分解(放心,還沒完呢,呵呵),先繼續(xù)上圖:

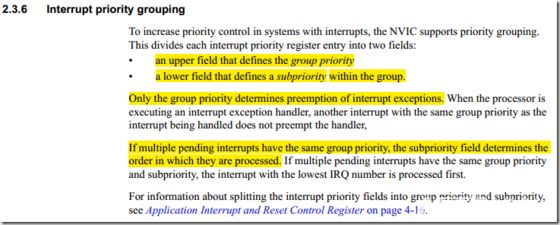

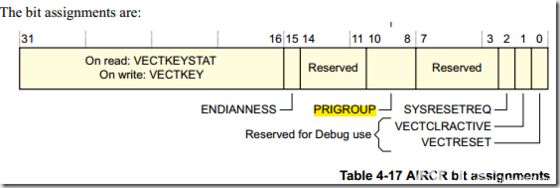

繼續(xù)找上圖亮點(diǎn),一個(gè)是M4最高支持16+4*60=256個(gè)中斷源,第二個(gè)這60個(gè)寄存器是可以按字節(jié)操作的(我們可以繼續(xù)的裝逼用指針了,哈哈),第三個(gè)跟M0+一樣即值越小優(yōu)先級越高,最后則是最大的區(qū)別,即每個(gè)寄出去你的8位數(shù)據(jù)都是可以定義其中斷優(yōu)先級了,說到這里,a question is raised,那是不是意味著M4的優(yōu)先級最高可以256個(gè)級別呢。我只能說,大家想多了,呵呵,繼續(xù)看下圖吧,可見PRIGROUP定義了這8位數(shù)據(jù)到底該怎么用了,這里出現(xiàn)了兩個(gè)新名詞,即Group Priority和Subpriority,至于這兩個(gè)優(yōu)先級是什么意思那大家繼續(xù)看圖2,大家先仔細(xì)理解理解,我喝口水先。。。Ok,繼續(xù)回來,從下面兩張圖可以看到在M4內(nèi)核中,其對中斷優(yōu)先級管理是分了兩個(gè)部分,一個(gè)是組優(yōu)先級一個(gè)是子優(yōu)先級,即組優(yōu)先級是管理搶占優(yōu)先級的(即是否能嵌套),即高的組優(yōu)先級中斷(數(shù)值低)可以搶占低的組優(yōu)先級(數(shù)值高)中斷的,而如果組優(yōu)先級是一樣的,即使子優(yōu)先級比正在執(zhí)行的中斷的子優(yōu)先級高也是不能搶占的,那又有同志們要問問題了,那子優(yōu)先級有啥用?呵呵,正如圖2所說,在組優(yōu)先級一致的情況下,多個(gè)中斷請求同時(shí)發(fā)生,這樣的情況下子優(yōu)先級高的可以先執(zhí)行的,而子優(yōu)先級低的則只能暫時(shí)pending等著了,呵呵。而回到PRIGROUP的作用是用來配置NVIC的8位數(shù)據(jù)域是如何分配給搶占優(yōu)先級和子優(yōu)先級的,而一般情況下,最好是各留4位給這二位大爺和小爺了,即每位爺最多可配16個(gè)優(yōu)先級,而PRIGROUP是從哪來的呢,呵呵,實(shí)際上它是SCB_AIRCR寄存器的其中3位如圖3所示。

呼。。。終于搞完了,總算把這個(gè)問題給寫出來了,我腦袋里可以騰出點(diǎn)地方給其他問題了,哈哈。另外實(shí)際上我上面寫了這么多理論的東西,但是ARM早已在CMSIS庫里的頭文件中把這部分函數(shù)API給出來了(core_cm4.h和core_cm0plus.h),而我之所以不閑麻煩的還是把這個(gè)寫出來,還是我這個(gè)知其然也要知其所以然的思想在作怪了。不過最后,我還是給出M0+和M4的中斷優(yōu)先級配置的兩個(gè)配置供廣大博友參考吧,然后其他就不多聊了,未完待續(xù):

M0+

NVIC_SetPriority(PORTA_IRQn, 1);

NVIC_SetPriority(PORTB_IRQn, 2);

M4+

NVIC_SetPriorityGrouping(0x03);

NVIC_SetPriority(PORTA_IRQn, NVIC_EncodePriority(0x03,1, 2));

NVIC_SetPriority(PORTB_IRQn, NVIC_EncodePriority(0x03, 2, 2));

-

ARM

+關(guān)注

關(guān)注

134文章

9321瀏覽量

375388 -

cpu

+關(guān)注

關(guān)注

68文章

11048瀏覽量

216121 -

嵌套

+關(guān)注

關(guān)注

0文章

16瀏覽量

8017

原文標(biāo)題:【博文精選】ARM Cortex-M4和Cortex-M0+中斷優(yōu)先級及嵌套搶占問題

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

飛思卡爾 Kinetis L系列M0+/M4中斷優(yōu)先級設(shè)置問題

28335中斷嵌套和中斷優(yōu)先級是怎么設(shè)置?

淺析stm32的中斷嵌套優(yōu)先級

STM32(Cortex-M3)中的優(yōu)先級概念

STM32中斷優(yōu)先級和開關(guān)總中斷

STM32中斷優(yōu)先級和開關(guān)總中斷

探討一下STM32中斷優(yōu)先級和開關(guān)總中斷

Stm32中斷優(yōu)先級概念及使用

msp430的中斷優(yōu)先級和中斷嵌套(及容易理解錯(cuò)誤的說明)

STM32筆記之中斷優(yōu)先級和開關(guān)總中斷

Cortex-M中斷及FreeRTOS中斷優(yōu)先級配置原理

ARM Cortex-M4中斷優(yōu)先級和嵌套

ARM Cortex-M4中斷優(yōu)先級和嵌套

評論