DDR硬件設計要點

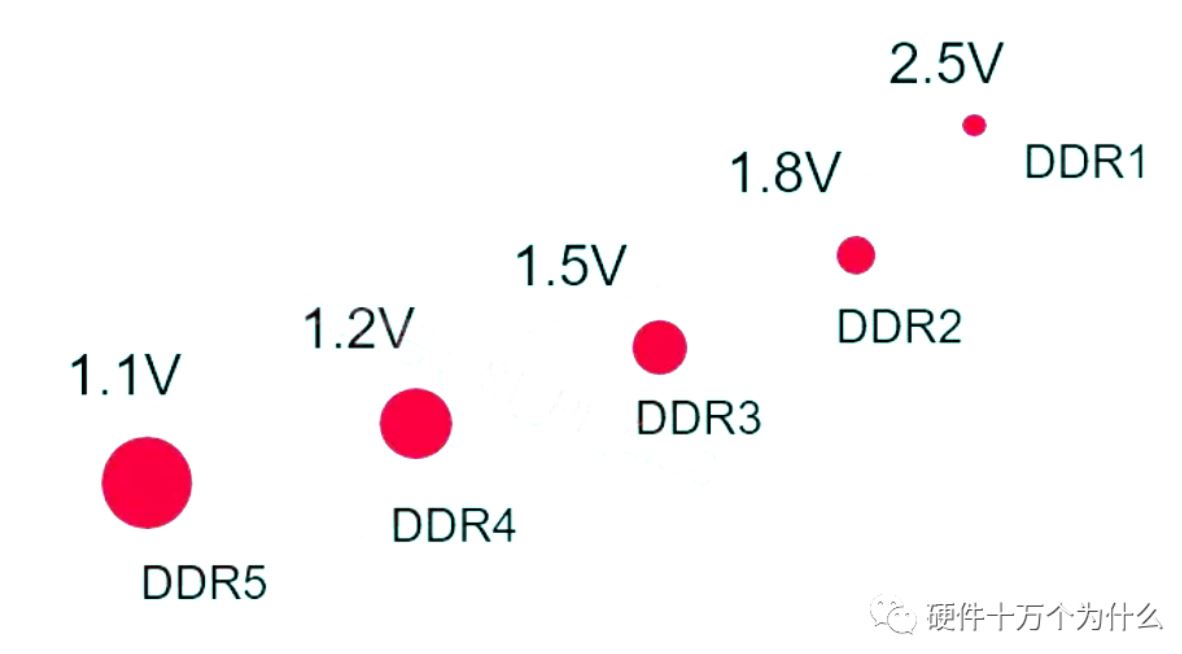

1. 電源DDR的電源可以分為三類:

a、主電源VDD和VDDQ,主電源的要求是VDDQ=VDD,VDDQ是給IO buffer供電的電源,VDD是給但是一般的使用中都是把VDDQ和VDD合成一個電源使用。

有的芯片還有VDDL,是給DLL供電的,也和VDD使用同一電源即可。電源設計時,需要考慮電壓,電流是否滿足要求,電源的上電順序和電源的上電時間,單調性等。電源電壓的要求一般在±5%以內。電流需要根據使用的不同芯片,及芯片個數等進行計算。由于DDR的電流一般都比較大,所以PCB設計時,如果有一個完整的電源平面鋪到管腳上,是最理想的狀態,并且在電源入口加大電容儲能,每個管腳上加一個100nF~10nF的小電容濾波。

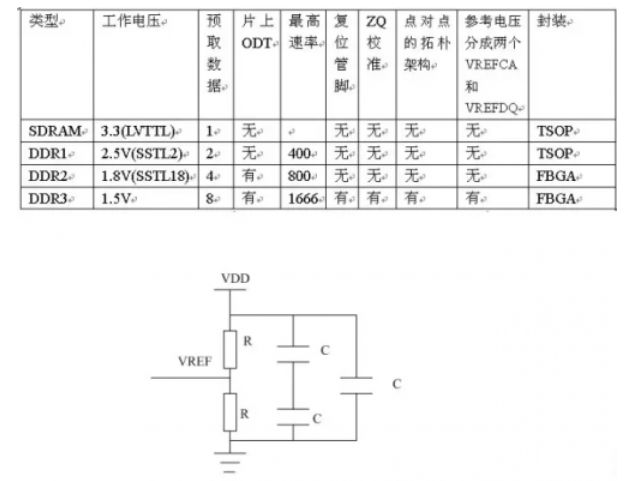

b、參考電源Vref,參考電源Vref要求跟隨VDDQ,并且Vref=VDDQ/2,所以可以使用電源芯片提供,也可以采用電阻分壓的方式得到。由于Vref一般電流較小,在幾個mA~幾十mA的數量級,所以用電阻分壓的方式,即節約成本,又能在布局上比較靈活,放置的離Vref管腳比較近,緊密的跟隨VDDQ電壓,所以建議使用此種方式。需要注意分壓用的電阻在100~10K均可,需要使用1%精度的電阻。 Vref參考電壓的每個管腳上需要加10nF的點容濾波,并且每個分壓電阻上也并聯一個電容較好。

C、用于匹配的電壓VTT(Tracking Termination Voltage)

VTT為匹配電阻上拉到的電源,VTT=VDDQ/2。DDR的設計中,根據拓撲結構的不同,有的設計使用不到VTT,如控制器帶的DDR器件比較少的情況下。如果使用VTT,則VTT的電流要求是比較大的,所以需要走線使用銅皮鋪過去。并且VTT要求電源即可以吸電流,又可以灌電流才可以。一般情況下可以使用專門為DDR設計的產生VTT的電源芯片來滿足要求。

而且,每個拉到VTT的電阻旁一般放一個10Nf~100nF的電容,整個VTT電路上需要有uF級大電容進行儲能。

在華為的設計中,在使用DDR顆粒的情況下,已經基本全部不使用VTT電源,全部采用電阻上下拉的戴維南匹配,只有在使用內存條的情況下才使用VTT電源。

一般情況下,DDR的數據線都是一驅一的拓撲結構,且DDR2和DDR3內部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到較好的信號質量。DDR2的地址和控制信號線如果是多負載的情況下,會有一驅多,并且內部沒有ODT,其拓撲結構為走T型的結構,所以常常需要使用VTT進行信號質量的匹配控制。DDR3可以采用Fly-by方式走線:

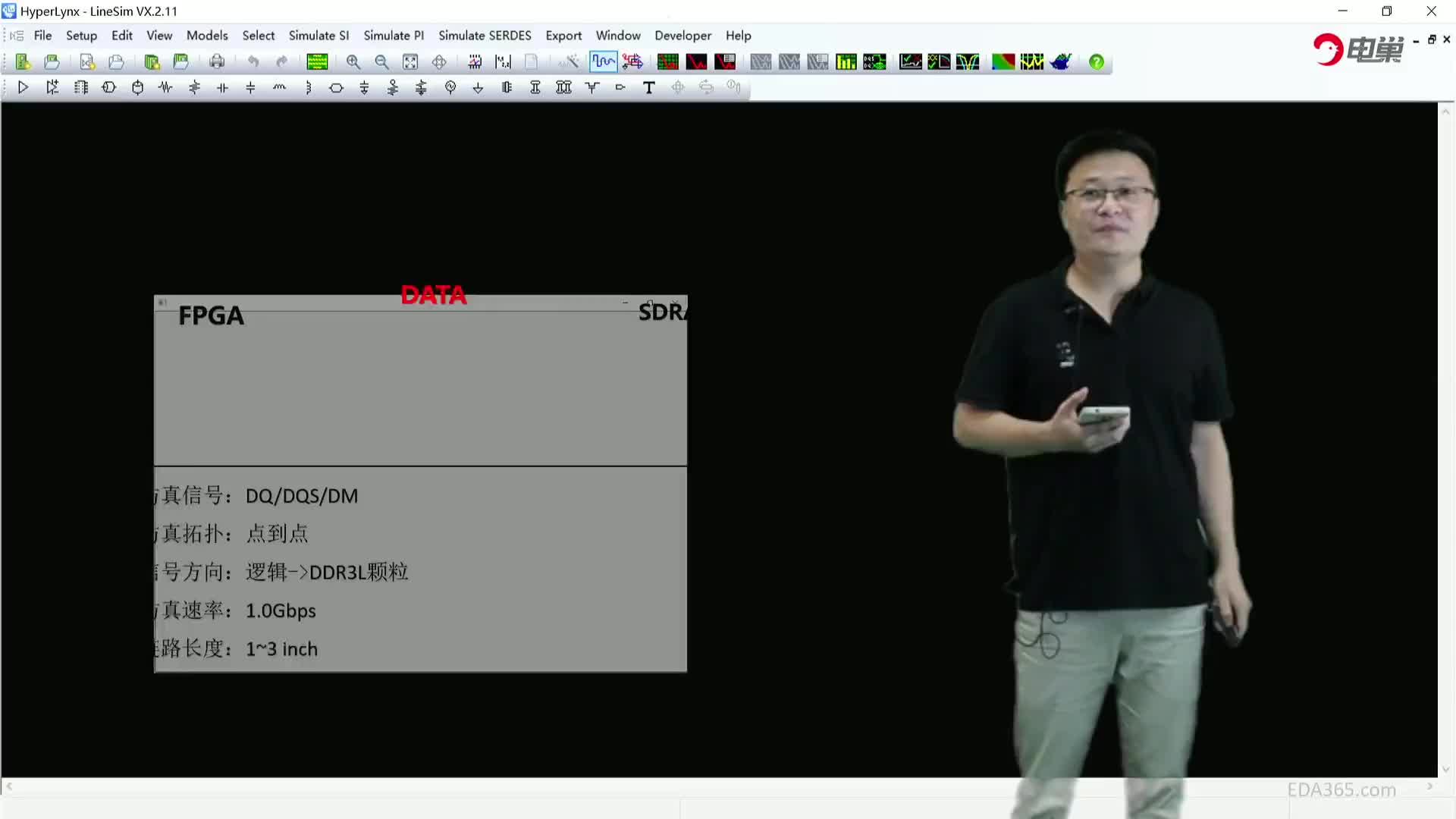

一個DDR3設計案例,來分析對比采用高阻抗負載走線和采用主線和負載走線同阻抗兩種情況的差異。

如上圖,Case1采用的是從內層控制器到各個SDRAM均為50ohm的阻抗設計。Case2則采用了主線40ohm,負載線60ohm的設計。對此通過仿真工具進行對比分析。

從以上仿真波形可以看出,使用較高阻抗負載走線的Case2在信號質量上明顯優于分支主線都采用同一種阻抗的Case1設計。而且對靠近驅動端的負載影響最大,遠離驅動端的最末端的負載影響較小。這個正是前面所分析到的,負載的分布電容導致了負載線部分的阻抗降低,如果采用主線和負載線同阻抗設計,反而導致了阻抗不連續的發生。把負載走線設計為較高的阻抗,用于平衡負載引入的分布電容,從而可以達到整條走線阻抗平衡的目的。

通過提高負載走線阻抗來平衡負載電容的做法,其實在以往的菊花鏈設計中是經常用到的方法。DDR3稱這種拓撲為fly-by,其實是有一定的含義的,意在強調負載stub走線足夠的短。

2. 時鐘

DDR的時鐘為差分走線,一般使用終端并聯100歐姆的匹配方式,差分走線差分對控制阻抗為100ohm,單端線50ohm。需要注意的是,差分線也可以使用串聯匹配,使用串聯匹配的好處是可以控制差分信號的上升沿緩度,對EMI可能會有一定的作用。

3. 數據和DQS

DQS信號相當于數據信號的參考時鐘,它在走線時需要保持和CLK信號保持等長。DQS在DDR2以下為單端信號,DDR2可作為差分信號,也可做單端,做單端時需要將DQS-接地,而DDR3為差分信號,需要走線100ohm差分線。由于內部有ODT,所以DQS不需要終端并聯100ohm電阻。每8bit數據信號對應一組DQS信號。

DQS信號在走線時需要與同組的DQS信號保持等長,控制單端50ohm的阻抗。在寫數據時,DQ和DQS的中間對齊,在讀數據時,DQ和DQS的邊沿對齊。DQ信號多為一驅一,并且DDR2和DDR3有內部的ODT匹配,所以一般在進行串聯匹配就可以了。

4. 地址和控制

地址和控制信號速度沒有DQ的速度快,以時鐘的上升沿為依據采樣,所以需要與時鐘走線保持等長。但如果使用多片DDR時,地址和控制信號為一驅多的關系,需要注意匹配方式是否適合。

5. PCB布局注意事項

PCB布局時,需要把DDR顆粒盡量靠近DDR控制器放置。每個電源管腳需要放置一個濾波電容,整個電源上需要有10uF以上大電容放在電源入口的位置上。電源最好使用獨立的層鋪到管腳上去。串聯匹配的電阻最好放在源端,如果是雙向信號,那么要統一放在同一端。如果是一驅多的DDR匹配結構,VTT上拉電阻需要放在最遠端,注意芯片的排布需要平衡。下圖是幾種DDR的拓撲結構,首先,一驅二的情況下分為樹狀結構,菊花鏈和Fly-by結構,Fly-by是一種STUB很小的菊花鏈結構。DDR2和DDR3走菊花鏈結構都是比較適合的。走樹狀結構可以把兩片芯片貼在PCB的正反兩面,對貼減小分叉的長度。一驅多的DDR拓撲結構比較復雜,需要仔細進行仿真。

6. PCB布線注意事項

PCB布線時,單端走線走50ohm,差分走線走100ohm阻抗。

注意控制差分線等長±10mil以內,同組走線根據速度的要求也有不同,一般為±50mil。

控制和地址線及DQS線和時鐘等長,DQ數據線和同組的DQS線等長。

注意時鐘及DQS和其他的信號要分開3W以上距離。

組間信號也要拉開至少3W寬的距離。

同一組信號最好在同一層布線。

盡量減少過孔的數目。

7. EMI問題

DDR由于其速度快,訪問頻繁,所以在許多設計中需要考慮其對外的干擾性,在設計時需要注意一下幾點

原理有性能指標要求的,易受干擾的電路模塊和信號,如模擬信號,射頻信號,時鐘信號等,防止DDR對其干擾,影響指標。

DDR的電源和不要與其他易受干擾的電源模塊使用同一電源,如必須使用同一電源,要注意使用電感、磁珠或電容進行濾波隔離處理。

在時鐘及DQS信號線上,預留一些可以增加的串聯電阻和并聯電容的位置,在EMI超出標準時,在信號完整性允許的范圍內增大串聯電阻或對地電容,使其信號上升延變緩,減少對外的輻射。

進行屏蔽處理,使用金屬外殼的屏蔽結構,屏蔽對外輻射。

注意保持地的完整性。

8. 測試方法

注意示波器的探頭和示波器本身的帶寬能夠滿足測試要求。

測試點的選擇要注意選到盡量靠近信號的接受端。

由于DDR信令比較復雜,因此為了能快速測試、調試和解決信號上的問題,我們希望能簡單地分離讀/寫比特。此時,最常用的是通過眼圖分析來幫助檢查DDR信號是否滿足電壓、定時和抖動方面的要求。

觸發模式的設置有幾種,首先可以利用前導寬度觸發器分離讀/寫信號。根據JEDEC規范,讀前導的寬度為0.9到1.1個時鐘周期,而寫前導的寬度規定為大于0.35個時鐘周期,沒有上限。第二種觸發方式是利用更大的信號幅度觸發方法分離讀/寫信號。通常,讀/寫信號的信號幅度是不同的,因此我們可以通過在更大的信號幅度上觸發示波器來實現兩者的分離。

測試中要注意信號的幅度,時鐘的頻率,差分時鐘的交叉點,上升沿是否單調,過沖等。

時序中最重要,最需要注意的就是建立時間和保持時間。

-

電源

+關注

關注

185文章

18352瀏覽量

256003 -

DDR

+關注

關注

11文章

732瀏覽量

66715

原文標題:一文讀懂電源DDR硬件設計要點

文章出處:【微信號:wujianying_danpianji,微信公眾號:單片機精講吳鑒鷹】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DDR硬件設計的四大注意要點

關于計算機的硬件維護的淺析

關于DDR應用的一般注意要點的詳細介紹

淺析電源DDR硬件設計技巧

普源DHO1072示波器DDR信號測試要點

淺析電源DDR硬件設計要點

淺析電源DDR硬件設計要點

評論