由于具有較好的頻帶利用率和抗噪聲性能,QPSK已成為一種在測控和通信領域廣泛使用的數字調制方式。隨著軟件無線電的不斷發展,直接中頻數字解調已變得越來越容易,而時鐘同步和載波同步是解調的關鍵問題。因而在全數字接收機中,同步過程通常通過算法在FPGA或DSP中實現,其通用性、互換性和移植性較強。

1 QPSK全數字接收機結構

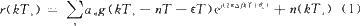

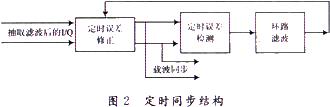

QPSK調制信號是抑制載波的信號,無法用常規的鎖相環或窄帶濾波器直接提取參考載波,但其載波相位變化只能提取有限的幾個離散值,因而可通過非線性處理恢復載波信號,從而完成相干解調。圖1是QPSK全數字接收機的框圖,首先中頻信號經抗混疊濾波后進入A/D變換器采樣。在滿足奈奎斯特采樣定理的條件下,應盡可能提高采樣率,以獲得較高的采樣信噪比,同時,模擬抗混疊濾波器也更易于實現。數字下變頻將中頻信號搬移至零頻,得到基帶的I(In-phase),Q(Quadrature)信號。由于采樣率相對于信號帶寬較大,因此需要進行抽取,降低數據率到一個合適的程度,以便于后續的信號處理。假設下變頻及抽取后的復基帶信號為:

其中,an是傳輸的數據,g(t)是系統脈沖響應,除去碼元信息an后還存在3個未知參數:時鐘誤差ε,載波相位誤差θ0和載波頻偏△f。這3個參數的分布是隨機的,只有恢復了這3個參數,an才能被正確地估計出來。

具體實現上要求解調的本振頻率振蕩在固定頻率上而頻差、相差和定時誤差的消除通過同步算法在數字信號處理器中完成。

2 同步算法

2.1 定時同步

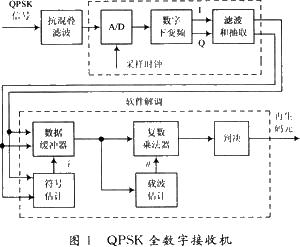

在載波同步和定時同步中,本文首先進行定時同步從而得到近最佳采樣點,以減少隨后進行的載波同步過程的計算量。也因為如此,使得定時同步時受到相位變化的影響,所以應選用對載波相位不敏感的定時同步算法,其結構如圖2所示。

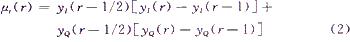

如圖2所示,下變頻后的數據經過濾波和抽取,I/Q兩路信號速率已降到2倍碼元速率,即1個碼元2個采樣點。而定時誤差檢測算法如下:

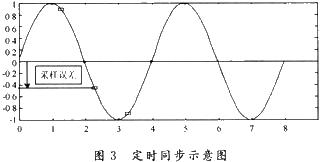

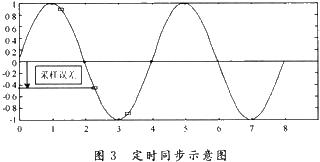

圖3中,設星號位置為最佳采樣點,1個碼元2個點。其中奇數位置是峰值,偶數位置是中間點,即過零點。而圖中的矩形點位置為實際的采樣點,可知實際采樣時鐘滯后。式(2)用幅度上的誤差來表示定時上的誤差,根據式(2)即可提取得到誤差信號。

得到的誤差信號經過環路濾波即可反饋對I/Q兩路進行修正。本文采取通過3點的二次插值運算,即拋物線插值得到近最佳采樣點,此時I,Q兩路1個碼元只有1個采樣點,從而有效地減少了后一階段載波同步的計算量。

2.2 載波同步

硬判決型COSTAS環是算術運算和邏輯運算的方法,對正交解調輸出的兩路基帶信號進行非線性處理,產生相位誤差控制信號,通過環路濾波,控制載波恢復鎖相環路。硬判決型COSTAs環具有入鎖信噪比低,誤碼率性能好的優點,適合信噪比低的PSK信號的解調。

設經過定時同步后的I,Q兩路信號分別為:

式中,△φ表示本地載波和接收信號的相位差,包括式(1)中的θ0以及由載波頻偏△f產生的相位差。然后經過鑒相器得到相位誤差,如式(5)所示:

鑒相曲線如圖4所示,其中橫坐標為弧度。

鑒相得到的相位誤差接著進行環路濾波,在定時同步時選用的是一階的濾波器,而載波同步時采用了二階環路。將得到的誤差估計值與經過定時同步的信號進行復數乘法以消除相位差的影響。但是這樣估計得到的結果存在四維相位模糊度,需通過差分編譯碼消除。

3 計算機仿真

在Matlab中,系統首先生成PN 9的偽隨機碼作為基帶信號。進行格雷碼的預差分編碼,上下變頻后得到正交和同相兩路基帶信號:

其中頻偏和初始相差在仿真中給定,通過算法來估計。

信道中的噪聲通過與隨機序列相加引入,用隨機序列代表高斯帶限白噪聲,該序列與一系數相乘,通過調整系數改變噪聲的大小,實現不同的信噪比。

采樣時,每個碼元取6個樣點,經過3倍抽取后每個碼元為2個采樣點,然后由上述算法內插出近最佳采樣序列。再用復數乘法消除掉估計出的相位誤差后進行判決和差分解碼,最后得到碼元信息。

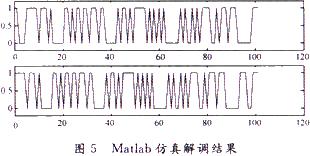

圖5分別為式(6)中的I(i)和針對他恢復出的數據,整個序列只是在時間上有一定的延時,上述算法較好地實現了數據的恢復。

4 硬件實現

4.1 VHDL設計和仿真驗證

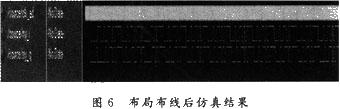

完成算法系統的全精度仿真后,使用ISE PrOjectNavigator對上述QPSK的全數字解調算法進行VHDL編程,綜合(使用ISE自帶的XST綜合工具),實現(包括轉換、映射、布局布線和時間參數提取),以及功能仿真和時序仿真。

為方便觀察輸出結果正確與否,將基帶I,Q數據設計為重復周期為15的相同數據,時間上相差一個時鐘周期。用Matlab計算出I,Q調制后的QPSK信號,保存為二進制文件,作為功能和時序仿真的輸入文件。圖6是布局布線后的時序仿真結果,最上一行為60 MHz采樣時鐘,下面兩行是解調后的I,Q數據,數據率為10 MHz。

從圖6中可以看出,經過同步后,解調后的I,Q數據是正確的,從而證明VHDL設計是成功的。

4.2 FPGA硬件電路驗證

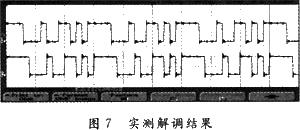

硬件方案的具體實現中,高速信號處理板包括A/D采樣芯片AD6645(最高采樣率為65 MHz,14 b),時鐘分配器CY2305,Virtex-II Pro FPGA XC2VP70和配置用的PROM(XCf32P)。微波源4438C產生中頻105 MHz、比特率20 Mb/s的QPSK信號,I,Q數據格式同上。任意波形發生器輸出60 MHz的正弦波信號作為A/D的采樣時鐘。用54622D示波器觀察高速信號處理板輸出的解調后的I,Q信號。

使用PrOject Navrigator生成下載用的.mcs.和.bit文件,將他們下載到FPGA和PROM中進行實際測試。圖7是實際觀察到的I,Q數據,從中可以看出,對寬帶QPSK信號的解調是正確的。

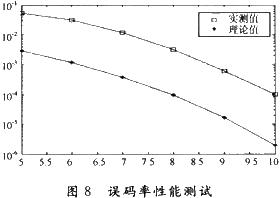

圖8是系統的誤碼率性能測試,當信噪比大于8 dB時,實測值與理論值之間有大約2 dB的差,這主要由于系統前端濾波器不匹配,進入系統的噪聲帶寬比信號帶寬大得多,影響了系統性能。對濾波器的改進將有利于系統性能的改善。

5 結 語

本文首先介紹了QPSK信號的構成,指出同步技術是QPSK信號解調的主要任務。在此基礎上,與現有成熟算法相結合,針對高碼率QPSK信號提出一種計算量小,易于實現的同步方法,他采用數字轉換跟蹤環和COSTAS環實現同步。計算機仿真及實測結果表明,該方法是可行的,適合FPGA實現。

-

通信

+關注

關注

18文章

6184瀏覽量

137468 -

變換器

+關注

關注

17文章

2132瀏覽量

110509 -

無線電

+關注

關注

61文章

2163瀏覽量

117753

發布評論請先 登錄

AnyWay變頻功率分析儀同步源來自電壓還是電流信號?

直流電機雙閉環數字調速系統設計與實現

信號線電壓高怎么回事,如何解決

PWM信號的濾波和處理方法

誤碼率測試儀的技術原理和應用場景

配網行波故障定位裝置 系統構成 廣域時鐘同步 工程安裝

數字鎖相環提取位同步信號的原理

多臺變頻器同步控制的接線和方法

同步調制異步調制的概念及優缺點

數字信號的通信指標誤碼率體現了什么

FPGA異步信號處理方法

激光云高儀如何實現精確測量云層高度?

同步電機的速度控制方法

高碼率QPSK信號的構成及實現同步的方法介紹

高碼率QPSK信號的構成及實現同步的方法介紹

評論