靜電放電(ESD: Electrostatic Discharge),應(yīng)該是造成所有電子元器件或集成電路系統(tǒng)造成過度電應(yīng)力破壞的主要元兇。因?yàn)殪o電通常瞬間電壓非常高(>幾千伏),所以這種損傷是毀滅性和永久性的,會(huì)造成電路直接燒毀。所以預(yù)防靜電損傷是所有IC設(shè)計(jì)和制造的頭號(hào)難題。

靜電,通常都是人為產(chǎn)生的,如生產(chǎn)、組裝、測試、存放、搬運(yùn)等過程中都有可能使得靜電累積在人體、儀器或設(shè)備中,甚至元器件本身也會(huì)累積靜電,當(dāng)人們在不知情的情況下使這些帶電的物體接觸就會(huì)形成放電路徑,瞬間使得電子元件或系統(tǒng)遭到靜電放電的損壞(這就是為什么以前修電腦都必須要配戴靜電環(huán)托在工作桌上,防止人體的靜電損傷芯片),如同云層中儲(chǔ)存的電荷瞬間擊穿云層產(chǎn)生劇烈的閃電,會(huì)把大地劈開一樣,而且通常都是在雨天來臨之際,因?yàn)榭諝鉂穸却笠仔纬蓪?dǎo)電通到。

那么,如何防止靜電放電損傷呢?首先當(dāng)然改變壞境從源頭減少靜電(比如減少摩擦、少穿羊毛類毛衣、控制空氣溫濕度等),當(dāng)然這不是我們今天討論的重點(diǎn)。我們今天要討論的是如何在電路里面設(shè)計(jì)保護(hù)電路,當(dāng)外界有靜電的時(shí)候我們的電子元器件或系統(tǒng)能夠自我保護(hù)避免被靜電損壞(其實(shí)就是安裝一個(gè)避雷針)。這也是很多IC設(shè)計(jì)和制造業(yè)者的頭號(hào)難題,很多公司有專門設(shè)計(jì)ESD的團(tuán)隊(duì),今天我就和大家從最基本的理論講起逐步講解ESD保護(hù)的原理及注意點(diǎn), 你會(huì)發(fā)現(xiàn)前面講的PN結(jié)/二極管、三極管、MOS管、全都用上了……

以前的專題講解PN結(jié)二極管理論的時(shí)候,就講過二極管有一個(gè)特性:正向?qū)ǚ聪蚪刂?不記得就去翻前面的課程),而且反偏電壓繼續(xù)增加會(huì)發(fā)生雪崩擊穿(Avalanche Breakdown)而導(dǎo)通,我們稱之為鉗位二極管(Clamp)。這正是我們設(shè)計(jì)靜電保護(hù)所需要的理論基礎(chǔ),我們就是利用這個(gè)反向截止特性讓這個(gè)旁路在正常工作時(shí)處于斷開狀態(tài),而外界有靜電的時(shí)候這個(gè)旁路二極管發(fā)生雪崩擊穿而形成旁路通路保護(hù)了內(nèi)部電路或者柵極(是不是類似家里水槽有個(gè)溢水口,防止水龍頭忘關(guān)了導(dǎo)致整個(gè)衛(wèi)生間水災(zāi))。那么問題來了,這個(gè)擊穿了這個(gè)保護(hù)電路是不是就徹底死了?難道是一次性的?答案當(dāng)然不是。PN結(jié)的擊穿分兩種,分別是電擊穿和熱擊穿,電擊穿指的是雪崩擊穿(低濃度)和齊納擊穿(高濃度),而這個(gè)電擊穿主要是載流子碰撞電離產(chǎn)生新的電子-空穴對(duì)(electron-hole),所以它是可恢復(fù)的。但是熱擊穿是不可恢復(fù)的,因?yàn)闊崃烤奂瘜?dǎo)致硅(Si)被熔融燒毀了。所以我們需要控制在導(dǎo)通的瞬間控制電流,一般會(huì)在保護(hù)二極管再串聯(lián)一個(gè)高電阻,另外,大家是不是可以舉一反三理解為什么ESD的區(qū)域是不能form Silicide的?還有給大家一個(gè)理論,ESD通常都是在芯片輸入端的Pad旁邊,不能在芯片里面,因?yàn)槲覀兛偸窍M饨绲撵o電需要第一時(shí)間泄放掉吧, 放在里面會(huì)有延遲的(關(guān)注我前面解剖的那個(gè)芯片PAD旁邊都有二極管。甚至有放兩級(jí)ESD的,達(dá)到雙重保護(hù)的目的。

在講ESD的原理和Process之前,我們先講下ESD的標(biāo)準(zhǔn)以及測試方法,根據(jù)靜電的產(chǎn)生方式以及對(duì)電路的損傷模式不同通常分為四種測試方式: 人體放電模式(HBM: Human-Body Model)、機(jī)器放電模式(Machine Model)、元件充電模式(CDM: Charge-Device Model)、電場感應(yīng)模式(FIM: Field-Induced Model),但是業(yè)界通常使用前兩種模式來測試(HBM, MM)。

人體放電模式(HBM)

當(dāng)然就是人體摩擦產(chǎn)生了電荷突然碰到芯片釋放的電荷導(dǎo)致芯片燒毀擊穿,秋天和別人觸碰經(jīng)常觸電就是這個(gè)原因。業(yè)界對(duì)HBM的ESD標(biāo)準(zhǔn)也有跡可循(MIL- STD-883C method 3015.7,等效人體電容為100pF,等效人體電阻為1.5Kohm),或者國際電子工業(yè)標(biāo)準(zhǔn)(EIA/JESD22-A114-A)也有規(guī)定,看你要follow哪一份了。如果是MIL-STD-883C method 3015.7,它規(guī)定小于<2kV的則為Class-1,在2kV~4kV的為class-2,4kV~16kV的為class-3。?

機(jī)器放電模式(MM)

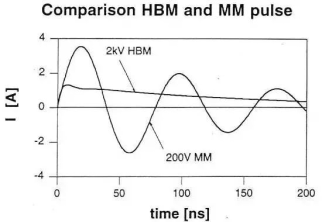

當(dāng)然就是機(jī)器(如robot)移動(dòng)產(chǎn)生的靜電觸碰芯片時(shí)由pin腳釋放,次標(biāo)準(zhǔn)為EIAJ-IC-121 method 20(或者標(biāo)準(zhǔn)EIA/JESD22-A115-A),等效機(jī)器電阻為0 (因?yàn)榻饘?,電容依舊為100pF。由于機(jī)器是金屬且電阻為0,所以放電時(shí)間很短,幾乎是ms或者us之間。但是更重要的問題是,由于等效電阻為0,所以電流很大,所以即使是200V的MM放電也比2kV的HBM放電的危害大。而且機(jī)器本身由于有很多導(dǎo)線互相會(huì)產(chǎn)生耦合作用,所以電流會(huì)隨時(shí)間變化而干擾變化。

ESD的測試方法類似FAB里面的GOI測試,指定pin之后先給他一個(gè)ESD電壓,持續(xù)一段時(shí)間后,然后再回來測試電性看看是否損壞,沒問題再去加一個(gè)step的ESD電壓再持續(xù)一段時(shí)間,再測電性,如此反復(fù)直至擊穿,此時(shí)的擊穿電壓為ESD擊穿的臨界電壓(ESD failure threshold Voltage)。通常我們都是給電路打三次電壓(3 zaps),為了降低測試周期,通常起始電壓用標(biāo)準(zhǔn)電壓的70% ESD threshold,每個(gè)step可以根據(jù)需要自己調(diào)整50V或者100V。

(1)Stress number = 3 Zaps. (5 Zaps, the worst case)

(2)Stress step

ΔVESD= 50V(100V) for VZAP<=1000VΔVESD?= 100V(250V, 500V) for VZAP?> 1000V

(3)Starting VZAP= 70% of averaged ESD failure threshold (VESD)

另外,因?yàn)槊總€(gè)chip的pin腳很多,你是一個(gè)個(gè)pin測試還是組合pin測試,所以會(huì)分為幾種組合:I/O-pin測試(Input and Output pins)、pin-to-pin測試、Vdd-Vss測試(輸入端到輸出端)、Analog-pin。

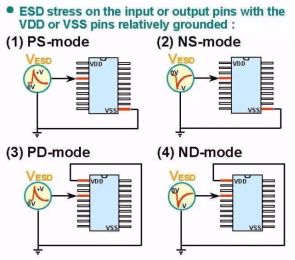

1. I/O pins

就是分別對(duì)input-pin和output-pin做ESD測試,而且電荷有正負(fù)之分,所以有四種組合:input+正電荷、input+負(fù)電荷、output+正電荷、output+負(fù)電荷。測試input時(shí)候,則output和其他pin全部浮接(floating),反之亦然。

2.pin-to-pin測試

靜電放電發(fā)生在pin-to-pin之間形成回路,但是如果要每每兩個(gè)腳測試組合太多,因?yàn)槿魏蔚腎/O給電壓之后如果要對(duì)整個(gè)電路產(chǎn)生影響一定是先經(jīng)過VDD/Vss才能對(duì)整個(gè)電路供電,所以改良版則用某一I/O-pin加正或負(fù)的ESD電壓,其他所有I/O一起接地,但是輸入和輸出同時(shí)浮接(Floating)。

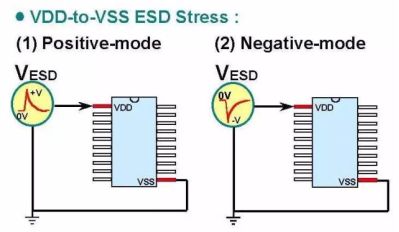

3.Vdd-Vss之間靜電放電

靜電放電發(fā)生在pin-to-pin之間形成回路,但是如果要每每兩個(gè)腳測試組合太多,因?yàn)槿魏蔚腎/O給電壓之后如果要對(duì)整個(gè)電路產(chǎn)生影響一定是先經(jīng)過VDD/Vss才能對(duì)整個(gè)電路供電,所以改良版則用某一I/O-pin加正或負(fù)的ESD電壓,其他所有I/O一起接地,但是輸入和輸出同時(shí)浮接(Floating)。

4.Analog-pin放電測試

因?yàn)?a href="http://m.xsypw.cn/analog/" target="_blank">模擬電路很多差分比對(duì)(Differential Pair)或者運(yùn)算放大器(OP AMP)都是有兩個(gè)輸入端的,防止一個(gè)損壞導(dǎo)致差分比對(duì)或運(yùn)算失效,所以需要單獨(dú)做ESD測試,當(dāng)然就是只針對(duì)這兩個(gè)pin,其他pin全部浮接(floating)。

好了,ESD的原理和測試部分就講到這里了,下面接著講Process和設(shè)計(jì)上的factor隨著摩爾定律的進(jìn)一步縮小,器件尺寸越來越小,結(jié)深越來越淺,GOX越來越薄,所以靜電擊穿越來越容易,而且在Advance制程里面,Silicide引入也會(huì)讓靜電擊穿變得更加尖銳,所以幾乎所有的芯片設(shè)計(jì)都要克服靜電擊穿問題。

靜電放電保護(hù)可以從FAB端的Process解決,也可以從IC設(shè)計(jì)端的Layout來設(shè)計(jì),所以你會(huì)看到Prcess有一個(gè)ESD的option layer,或者Design rule里面有ESD的設(shè)計(jì)規(guī)則可供客戶選擇等等。當(dāng)然有些客戶也會(huì)自己根據(jù)SPICE model的電性通過layout來設(shè)計(jì)ESD。

1、制程上的ESD

要么改變PN結(jié),要么改變PN結(jié)的負(fù)載電阻,而改變PN結(jié)只能靠ESD_IMP了,而改變與PN結(jié)的負(fù)載電阻,就是用non-silicide或者串聯(lián)電阻的方法了。

1)Source/Drain的ESD implant

因?yàn)槲覀兊腖DD結(jié)構(gòu)在gate poly兩邊很容易形成兩個(gè)淺結(jié),而這個(gè)淺結(jié)的尖角電場比較集中,而且因?yàn)槭菧\結(jié),所以它與Gate比較近,所以受Gate的末端電場影響比較大,所以這樣的LDD尖角在耐ESD放電的能力是比較差的(<1kV),所以如果這樣的Device用在I/O端口,很容造成ESD損傷。所以根據(jù)這個(gè)理論,我們需要一個(gè)單獨(dú)的器件沒有LDD,但是需要另外一道ESD implant,打一個(gè)比較深的N+_S/D,這樣就可以讓那個(gè)尖角變圓而且離表面很遠(yuǎn),所以可以明顯提高ESD擊穿能力(>4kV)。但是這樣的 話這個(gè)額外的MOS的Gate就必須很長防止穿通(punchthrough),而且因?yàn)槠骷灰粯恿耍孕枰獑为?dú)提取器件的SPICE Model。

2)接觸孔(contact)的ESD implant

在LDD器件的N+漏極的孔下面打一個(gè)P+的硼,而且深度要超過N+漏極(drain)的深度,這樣就可以讓原來Drain的擊穿電壓降低(8V-->6V),所以可以在LDD尖角發(fā)生擊穿之前先從Drain擊穿導(dǎo)走從而保護(hù)Drain和Gate的擊穿。所以這樣的設(shè)計(jì)能夠保持器件尺寸不變,且MOS結(jié)構(gòu)沒有改變,故不需要重新提取SPICE model。當(dāng)然這種智能用于non-silicide制程,否則contact你也打不進(jìn)去implant。

3)SAB (SAlicide Block)

一般我們?yōu)榱私档蚆OS的互連電容,我們會(huì)使用silicide/SAlicide制程,但是這樣器件如果工作在輸出端,我們的器件負(fù)載電阻變低,外界 ESD電壓將會(huì)全部加載在LDD和Gate結(jié)構(gòu)之間很容易擊穿損傷,所以在輸出級(jí)的MOS的Silicide/Salicide我們通常會(huì)用SAB(SAlicide Block)光罩擋住RPO,不要形成silicide,增加一個(gè)photo layer成本增加,但是ESD電壓可以從1kV提高到4kV。

4)串聯(lián)電阻法

這種方法不用增加光罩,應(yīng)該是最省錢的了,原理有點(diǎn)類似第三種(SAB)增加電阻法,我就故意給他串聯(lián)一個(gè)電阻(比如Rs_NW,或者HiR,等),這樣也達(dá)到了SAB的方法。

2、設(shè)計(jì)上的ESD

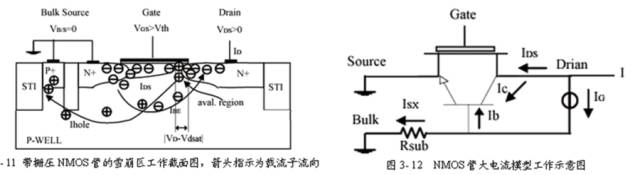

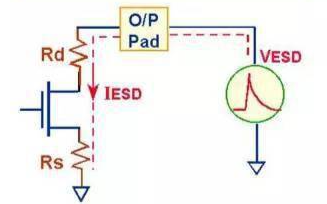

這就完全靠設(shè)計(jì)者的功夫了,有些公司在設(shè)計(jì)規(guī)則就已經(jīng)提供給客solution了,客戶只要照著畫就行了,有些沒有的則只能靠客戶自己的designer了,很多設(shè)計(jì)規(guī)則都是寫著這個(gè)只是guideline/reference,不是guarantee的。一般都是把Gate/Source/Bulk短接在一起,把Drain結(jié)在I/O端承受ESD的浪涌(surge)電壓,NMOS稱之為GGNMOS (Gate-Grounded NMOS)PMOS稱之為GDPMOS (Gate-to-Drain PMOS)。以NMOS為例,原理都是Gate關(guān)閉狀態(tài),Source/Bulk的PN結(jié)本來是短接0偏的,當(dāng)I/O端有大電壓時(shí),則Drain/Bulk PN結(jié)雪崩擊穿,瞬間bulk有大電流與襯底電阻形成壓差導(dǎo)致Bulk/Source的PN正偏,所以這個(gè)MOS的寄生橫向NPN管進(jìn)入放大區(qū)(發(fā)射結(jié)正偏,集電結(jié)反偏),所以呈現(xiàn)特性,起到保護(hù)作用。PMOS同理推導(dǎo)。

這個(gè)原理看起來簡單,但是設(shè)計(jì)的精髓(know-how)是什么?怎么觸發(fā)BJT?怎么維持?怎么撐到HBM>2KV or 4KV?

如何觸發(fā)?必須有足夠大的襯底電流,所以后來發(fā)展到了現(xiàn)在普遍采用的多指交叉并聯(lián)結(jié)構(gòu)(multi-finger)。但是這種結(jié)構(gòu)主要技術(shù)問題是基區(qū)寬度增加,放大系數(shù)減小,所以不容易開啟。而且隨著finger數(shù)量增多,會(huì)導(dǎo)致每個(gè)finger之間的均勻開啟變得很困難,這也是ESD設(shè)計(jì)的瓶頸所在。

如果要改變這種問題,大概有兩種做法(因?yàn)閠riger的是電壓,改善電壓要么是電阻要么是電流):1、利用SAB(SAlicide-Block)在I/O的Drain上形成一個(gè)高阻的non-Silicide區(qū)域,使得漏極方塊電阻增大,而使得ESD電流分布更均勻,從而提高泄放能力;2、增加一道P-ESD (Inner-Pickup imp,類似上面的接觸孔P+ ESD imp),在N+Drain下面打一個(gè)P+,降低Drain的雪崩擊穿電壓,更早有比較多的雪崩擊穿電流(詳見文獻(xiàn)論文: Inner Pickup on ESD of multi-finger NMOS.pdf)。

對(duì)于的ESD有兩個(gè)小小的常識(shí)要跟大家分享一下:

1)NMOS我們通常都能看到比較好的特性,但是實(shí)際上PMOS很難有特性,而且PMOS耐ESD的特性普遍比NMOS好,這個(gè)道理同HCI效應(yīng),主要是因?yàn)镹MOS擊穿時(shí)候產(chǎn)生的是電子,遷移率很大,所以Isub很大容易使得Bulk/Source正向?qū)ǎ荘MOS就難咯。

2) Trigger電壓/Hold電壓: Trigger電壓當(dāng)然就是之前將的的第一個(gè)拐點(diǎn)(Knee-point),寄生BJT的擊穿電壓,而且要介于BVCEO與BVCBO之間。而Hold電壓就是要維持持續(xù)ON,但是又不能進(jìn)入柵鎖(Latch-up)狀態(tài),否則就進(jìn)入二次擊穿(熱擊穿)而損壞了。還有個(gè)概念就是二次擊穿電流,就是進(jìn)入Latch-up之后I^2*R熱量驟增導(dǎo)致硅融化了,而這個(gè)就是要限流,可以通過控制W/L,或者增加一個(gè)限流高阻, 最簡單最常用的方法是拉大Drain的距離/拉大SAB的距離(ESD rule的普遍做法)。

3、柵極耦合(Gate-Couple) ESD技術(shù)

我們剛剛講過,Multi-finger的ESD設(shè)計(jì)的瓶頸是開啟的均勻性,假設(shè)有10只finger,而在ESD 放電發(fā)生時(shí),這10 支finger 并不一定會(huì)同時(shí)導(dǎo)通(一般是因Breakdown 而導(dǎo)通),常見到只有2-3 支finger會(huì)先導(dǎo)通,這是因布局上無法使每finger的相對(duì)位置及拉線方向完全相同所致,這2~3 支finger 一導(dǎo)通,ESD電流便集中流向這2~3支的finger,而其它的finger 仍是保持關(guān)閉的,所以其ESD 防護(hù)能力等效于只有2~3 支finger的防護(hù)能力,而非10 支finger 的防護(hù)能力。這也就是為何組件尺寸已經(jīng)做得很大,但ESD 防護(hù)能力并未如預(yù)期般地上升的主要原因,增打面積未能預(yù)期帶來ESD增強(qiáng),怎么辦?其實(shí)很簡單,就是要降低Vt1(Trigger電壓),我們通過柵極增加電壓的方式,讓襯底先開啟代替擊穿而提前導(dǎo)通產(chǎn)生襯底電流,這時(shí)候就能夠讓其他finger也一起開啟進(jìn)入導(dǎo)通狀態(tài),讓每個(gè)finger都來承受ESD電流,真正發(fā)揮大面積的ESD作用。

finger也一起開啟進(jìn)入導(dǎo)通狀態(tài),讓每個(gè)finger都來承受ESD電流,真正發(fā)揮大面積的ESD作用。

但是這種GCNMOS的ESD設(shè)計(jì)有個(gè)缺點(diǎn)是溝道開啟了產(chǎn)生了電流容易造成柵氧擊穿,所以他不見的是一種很好的ESD設(shè)計(jì)方案,而且有源區(qū)越小則柵壓的影響越大,而有源區(qū)越大則越難開啟,所以很難把握。

4、還有一種復(fù)雜的ESD保護(hù)電路: 可控硅晶閘管(SCR: Silicon Controlled Rectifier)

它就是我們之前講過的CMOS寄生的PNPN結(jié)構(gòu)觸發(fā)產(chǎn)生并且Latch-up,通過ON/OFF實(shí)現(xiàn)對(duì)電路的保護(hù),大家可以回顧一下,只要把上一篇里面那些抑制LATCH-up的factor想法讓其發(fā)生就可以了,不過只能適用于Layout,不能適用于Process,否則Latch-up又要fail了。

最后,ESD的設(shè)計(jì)學(xué)問太深了,我這里只是拋磚引玉給大家科普一下了,基本上ESD的方案有如下幾種:電阻分壓、二極管、MOS、寄生BJT、SCR(PNPN structure)等幾種方法。而且ESD不僅和Design相關(guān),更和FAB的process相關(guān),而且學(xué)問太深了,這里我也不是很了解,無法給再大家深入了。當(dāng)然術(shù)業(yè)專攻學(xué)無止境,工作中只有不斷學(xué)習(xí)才會(huì)創(chuàng)收更高效益。

-

ESD

+關(guān)注

關(guān)注

50文章

2269瀏覽量

175300 -

靜電

+關(guān)注

關(guān)注

2文章

523瀏覽量

37177

原文標(biāo)題:靜電放電ESD的原理和測試

文章出處:【微信號(hào):gh_f97d2589983b,微信公眾號(hào):高速射頻百花潭】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

防靜電基礎(chǔ)知識(shí)

手機(jī)防靜電要點(diǎn)分析

實(shí)施防靜電措施對(duì)產(chǎn)品設(shè)計(jì)及制造中的好處

如何應(yīng)對(duì)靜電對(duì)USB的“軟性損傷”

防靜電勞保安全鞋不容忽視

電子行業(yè)工廠防塵防靜電處理

元器件應(yīng)用中的靜電防護(hù)

靜電產(chǎn)生的原因及危害

如何預(yù)防靜電損傷?

一文講透靜電保護(hù)(ESD)原理和設(shè)計(jì)

靜電放電的保護(hù)資料詳細(xì)說明

預(yù)防靜電損傷是所有IC設(shè)計(jì)和制造的頭號(hào)難題!做好ESD保護(hù),電路免受損資料下載

預(yù)防靜電:你需要知道的關(guān)于靜電的知識(shí)

如何在IC設(shè)計(jì)和制造中預(yù)防靜電損傷?

如何在IC設(shè)計(jì)和制造中預(yù)防靜電損傷?

評(píng)論