引言

在FPGA的設計流程中,完成設計輸入以及成功綜合、布局布線,只能說明設計符合一定的語法規范,而并不能保證其滿足設計人員對功能的要求,因而需要通過仿真對設計進行驗證。仿真驗證的目的是為了發現設計的問題,而一旦發現,就需要千方百計地通過調試找到問題所在,這其實也是設計中比較困難的。

隨著FPGA可編程器件容量的不斷增大和設計復雜度的日益提高,功能調試已經成為一個很繁重的任務。為了使設計的產品盡快投入市場,設計人員需要一種簡易有效的測試工具,以盡可能縮短測試時間,提高測試效率。傳統的邏輯分析儀在測試復雜的FPGA設計時,會面臨以下幾點問題:

1) I/O引腳有限。設計中器件的選擇依據設計規模而定,通常所選器件的I/O引腳數目和設計的需求是恰好匹配的;

2) I/O引腳難以引出。設計者為減小電路板的面積,大都采用細間距工藝技術,這在不改變PCB板布線的情況下引出I/O引腳非常困難;

3)外接邏輯分析器有可能改變FPGA設計中信號的原來狀態,因此,很難保證待測信號的正確性;

4)傳統的邏輯分析器價格昂貴,會增加設計成本。

1 Signal Tap硬件調試原理

為了盡快使設計的產品投入市場,就要盡可能地縮短設計驗證所耗費的時間。為此,Altera公司推出了一種新的調試工具。這種型號的Sig-nal TapⅡ的邏輯分析器具有無干擾、便于升級、使用簡單、價格低廉等優點,可滿足FPGA開發中硬件調試的要求。

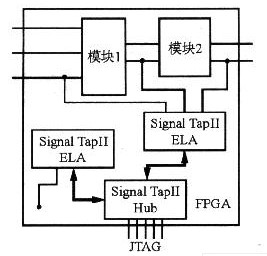

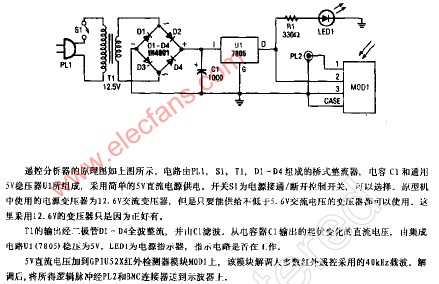

Signal TapⅡ邏輯分析器集成到QuartusⅡ設計軟件中,能夠捕獲和顯示可編程單芯片系統(SOPC)設計中的實時信號狀態,這樣,開發者就可以在整個設計過程中以系統級速度觀察硬件和軟件的交互。Signal TapⅡ可支持多達1024個通道,采樣深度高達128KB,每個分析器均有1O級觸發輸入/輸出,從而增加了采樣的精度。可以說,Signal TapⅡ為設計者提供了業界領先的SOPC設計的實時可視性,它能夠大大減少驗證過程中所花費的時間。目前,SignalTapⅡ邏輯分析器可以支持的器件系列包括:APEXTII,APEX20KE,APEX20KC,APEX20K,Cyclone,Ex-calibur,Mercury,Stratix GX,Stratix等。SignalTapⅡ將邏輯分析模塊嵌入到FPGA中,圖1所示是SignalTapⅡ的嵌入式邏輯分析器結構框圖。圖中,邏輯分析模塊可對待測節點數據進行捕獲。并將數據通過JTAG接口從FPGA傳送到QuartusⅡ中顯示。使用Signal TapⅡ無需額外的邏輯分析設備,只需將一根JTAG接口的下載電纜連接到要調試的FPGA器件,Signal TapⅡ在對FPGA的引腳和內部的連線信號進行捕獲后,便可將數據存儲在FPGA的RAM塊中。因此,需要為采樣信號、觸發信號和待測信號預留一定數目的RAM塊。

2 使用Signal Tap的一般流程

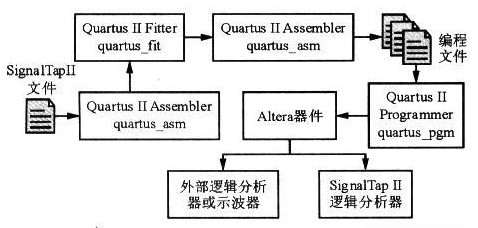

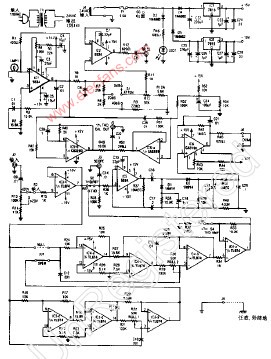

圖2所示是Signal TapⅡ的調試流程示意圖。使用Signal TapⅡ的一般流程,是在完成設計并編譯工程后,建立Signal TapⅡ(.stp)文件并加入工程,然后再配置STP文件,并將其編譯并下載設計到FPGA中,接著在QuartusⅡ軟件中顯示被測信號的波形,并在測試完畢后將該邏輯分析器從項目中刪除。

其Signal TapⅡ文件設置和采集信號數據的基本流程如下:

(1)建立新的Signal TapⅡ文件;

(2)設置采樣時鐘。采樣時鐘決定了顯示信號波形的分辨率,它的頻率要大于被測信號的最高頻率,否則將無法正確反映被測信號波形的變化。Signal TapⅡ通常在時鐘上升沿將被測信號存儲到緩存。

(3)設置被測信號。可以使用Node Finder中的SignalI TapⅡ濾波器查找所有預綜合和布局布線后的Signal TapⅡ節點,添加要觀察的信號。邏輯分析器不可測試的信號包括:邏輯單元的進位信號、PLL的時鐘輸出、JTAG引腳信號、LVDS(低壓差分)信號等。

(4)配置采樣深度,確定RAM的大小。Signal TapⅡ所能顯示的被測信號波形的時間長度為TX,其計算公式如下:

TX=NTS

式中,N為緩存中存儲的采樣點數,TS為采樣時鐘的周期;

(5)設置buffer acquisition mode。buffer ac-quisition mode包括循環采樣存儲和連續存儲兩種模式。循環采樣存儲也就是分段存儲,即將整個緩存分成多個片段(segment),每當觸發條件滿足時就捕獲一段數據。該功能可以去掉無關的數據,使采樣緩存的使用更加靈活;

(6)觸發級別。Signal TapⅡ支持多觸發級的觸發方式,最多可支持1O級觸發,設計人員可以只查看最重要的數據。

(7)觸發條件。Signal TapⅡ邏輯分析器可支持多個觸發位置以及外部觸發事件,可以使用Signal TapⅡ邏輯分析器窗口中的Signal Configu-ration面板來設置觸發器選項,也可以設定復雜的觸發條件來捕獲相應的數據,以協助調試設計。當觸發條件滿足時,可在Signal Tap時鐘的上升沿采樣被測信號。

3 使用Signal Tap調試PCI主設備控制器

Signal TapⅡ邏輯分析器的使用大大加快了PCI主設備控制器的調試進程,例如在調試DMA傳輸后的中斷產生時,由于軟件檢測不到中斷而導致DMA傳輸結束后,可能會使計算機死機而不能正常結束(完整的流程是:DMA傳輸結束,產生中斷,并在軟件檢測到中斷后進人中斷服務程序來處理中斷,然后清除)。

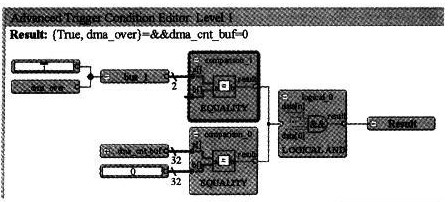

對中斷產生的條件進行檢查時,32位的DMA計數器必須為0,而且DMA傳輸結束標志信號必須有效,針對這一條件,使用普通的示波器和邏輯分析器根本無法跟蹤到,但是使用SignalTapⅡ邏輯分析器的高級設置,就可將這兩個條件作為觸發條件,從而檢測到中斷是否產生,其高級設置如圖3所示。

4 結束語

與傳統邏輯分析器相比,使用Signal TapⅡ邏輯分析器有以下優勢:

(1)不占用額外的I/O資源。若使用傳統的邏輯分析儀觀察信號波形,則必須將待觀察信號引到空閑管腳,這樣,在器件管腳緊張的時候,Signal TapⅡ邏輯分析器的優點就可以得到充分地體現。

(2)不占用PCB空間。若使用傳統邏輯分析儀,則需要從FPGA器件上引出測試管腳到PCB上,這樣會增加PCB走線難度;

(3)不破壞信號的完整性;

(4)傳統邏輯分析儀價格昂貴,而將Signal TapⅡ邏輯分析器集成在QuartusⅡ軟件中,無需另外付費;

:

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614657 -

ARM

+關注

關注

134文章

9321瀏覽量

375448 -

仿真

+關注

關注

51文章

4245瀏覽量

135380

發布評論請先 登錄

FPGA數字核脈沖分析器硬件電路

偏振分析器

CCS中性能分析器profile的使用?

Signal tap 邏輯分析儀使用教程

一種實用的脈沖幅度分析器

嵌入式邏輯分析儀在FPGA設計中的應用

協議分析器在WLAN中的應用

靜態代碼分析器

Signal tap邏輯分析儀應該如何使用?

Signal TapⅡ邏輯分析器的特點及優勢分析

Signal TapⅡ邏輯分析器的特點及優勢分析

評論