引 言

在數(shù)字視頻創(chuàng)新已經(jīng)成為數(shù)字信息產(chǎn)業(yè)熱點(diǎn)的今天,數(shù)字視頻系統(tǒng)的設(shè)計(jì)方法不斷提高,數(shù)字視頻系統(tǒng)的復(fù)雜度已經(jīng)遠(yuǎn)遠(yuǎn)超過以往任何時候。達(dá)芬奇技術(shù)成功實(shí)現(xiàn)數(shù)字視頻需要四大要素的最新進(jìn)步,即:處理器、開發(fā)工具、軟件以及系統(tǒng)專業(yè)技術(shù)。由于能夠在集成這四種要素的平臺中實(shí)現(xiàn)數(shù)字視頻、音頻、語音與話音技術(shù),因此達(dá)芬奇技術(shù)可以為數(shù)字視頻的當(dāng)前變革打下基礎(chǔ)。

本設(shè)計(jì)是在一塊60*60mm 的PCB板上來完成視頻的采集、處理與顯示。由攝像頭采集的視頻圖像經(jīng)由解碼器轉(zhuǎn)換成達(dá)芬奇處理器能夠處理的格式,在Codec Engine 中實(shí)現(xiàn)H.264 、MPEG-4編解碼,在LCD液晶屏上最高能達(dá)到1280*720 分辨率下30fps(幀/每秒)流暢顯示。這樣的數(shù)字視頻系統(tǒng)能達(dá)到尺寸小,功能強(qiáng),設(shè)計(jì)靈活,實(shí)用性廣的優(yōu)點(diǎn)。

1. 1.系統(tǒng)的總體架構(gòu)及工作原理

2. 1.1 TMS320DM*6 器件總攬 達(dá)芬奇處理器TMS320DM*6 是基于業(yè)界最高性能的DSP平臺—TI TMS320C6000? 由ARM926EJ-S 內(nèi)核、TMS320C64x+ DSP 內(nèi)核、系統(tǒng)控制、視頻處理子系統(tǒng)(VPSS)、電源管理、外部存儲器接口、外圍控制模塊等功能模塊組成。

TMS320DM*6 中的ARM926EJ-S 內(nèi)核具有16KB 指令和8KB 數(shù)據(jù)Cache 及16KB ROM 和16KB RAM 。TMS320C64x+ DSP 內(nèi)核具有32KB L1 程序R A M / C a c h e 、8 0 K B L1 數(shù)據(jù)R A M /Cache 及64KB L2 RAM/Cache 。具有DDR2 內(nèi)存控制器;64 通道增強(qiáng)型DMA 控制器;串行端口(3 個UART、I2C、SPI、音頻串口);3 個64 位通用定時器;10/100M 以太網(wǎng);USB2.0 端口;3 個PWM 端口;多達(dá)71 個通用I/O 口;支持MMC/SD/CF 卡等。系統(tǒng)控制模塊提供了看門狗、中斷控制器、電源管理控制器、復(fù)位控制器及2 個片上振蕩器。視頻處理子系統(tǒng)(VPSS) 有用于視頻輸入的視頻前端輸入(VPFF) 接口由CCD 控制器(CCDC), 預(yù)處理器、柱狀模塊、自動曝光/白平衡/聚焦模塊(H3A)和寄存器組成;和用于視頻輸出的視頻后端輸出(VPBE)接口由屏幕菜單式調(diào)節(jié)器(OSD)、視頻編碼器(VENC)和四路10bit DACs 組成。

1.2 系統(tǒng)的硬件組成及工作原理

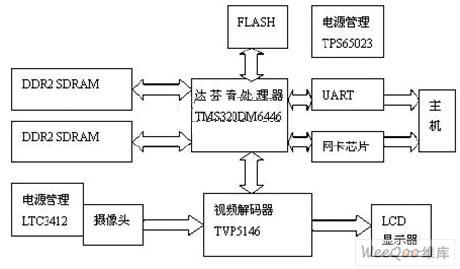

整個數(shù)字視頻系統(tǒng)采用的是由達(dá)芬奇處理器(TMS320DM*6)、DDR2 SDRAM 、NAND FLASH、視頻解碼器TVP5146 、電源管理芯片TPS65023,LTC3412 加上外圍接口芯片的方案。視頻解碼器把CCD攝像頭傳過來的模擬視頻信號進(jìn)行模/數(shù)轉(zhuǎn)換,變成符合ITU-BT.656 標(biāo)準(zhǔn)的數(shù)字視頻信號,然后將數(shù)字視頻信號傳到達(dá)芬奇處理器的視頻處理子系統(tǒng)的前端進(jìn)行預(yù)處理經(jīng)過Codec Engine 編解碼后送到視頻處理子系統(tǒng)的后端,直接輸出數(shù)字視頻信號到顯示終端上或是通過四路54MHz 的DACs來提供NTSC/PAL制式的模擬視頻輸出。DM*6 上的ARM端主要做為控制器來控制視頻解碼芯片和外圍接口芯片,DSP端主要負(fù)責(zé)視頻編解碼工作。系統(tǒng)硬件框圖如圖1所示

圖1 系統(tǒng)硬件框圖

1. 2.視頻部分的硬件結(jié)構(gòu)及其分析

2. 2.1 視頻采集與解碼

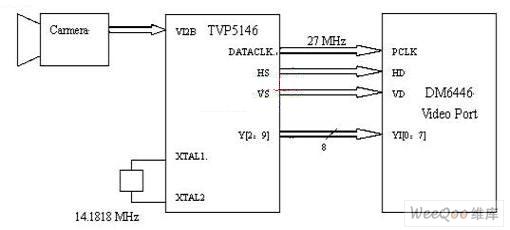

本設(shè)計(jì)選用TI公司的視頻解碼芯片TVP5146 完成從模擬到數(shù)字視頻的轉(zhuǎn)換。TVP5146 允許10路模擬視頻輸入,具有4路10bit A/D 轉(zhuǎn)換器;場同步信號VS,行同步信號HS,奇偶場信號FID,時鐘輸出信號DATACLK 等都由引腳直接引出,省去同步時鐘電路的設(shè)計(jì)。

TVP5146 上的Y[9:2]為輸出的亮度視頻信號,DATACLK 為行鎖定系統(tǒng)的輸出時鐘,像素時鐘頻率為27MHz, 用來同步數(shù)據(jù)采集,HS為行同步信號,VS為場同步信號分別與達(dá)芬奇處理器DM*6 視頻端口對應(yīng)的信號相連接。HS的高電平表示一行有效采樣點(diǎn)個數(shù),VS 的高電平表示一場有效信號,對于NTSC 制信號,單場為243 行, 奇偶場信號FID為"1" 時,表示當(dāng)前為奇數(shù)場,為"0" 表示偶數(shù)場。視頻解碼芯片與DM*6 的接口電路如圖2所示。

圖2 視頻前端模塊接口

2.2 圖像處理與顯示

實(shí)時圖像處理系統(tǒng)設(shè)計(jì)的難點(diǎn)是如何在有限的時間內(nèi)完成大量圖像數(shù)據(jù)的處理。只有圖像處理系統(tǒng)的處理速度達(dá)到每秒25幀以上時才能達(dá)到實(shí)時的效果并且要想在顯示終端上顯示出高清晰的圖像最重要的就是在Codec Engine 中的視頻編解碼運(yùn)算。而達(dá)芬奇處理器能通過多種復(fù)雜的視頻編解碼來實(shí)現(xiàn)高清視頻輸出,如MPEG-4編解碼能顯示30fps分辨率為720p(1280*720);H.264 編解碼能顯示30fps 分辨率為D1(720*480) 等。TMS320DM*6 處理器視頻處理子系統(tǒng)中的視頻后端提供的在線視頻顯示處理器既能夠顯示兩組獨(dú)立的視頻窗口或兩組獨(dú)立的OSD窗口,還可以以一個視頻窗口、一個OSD窗口和一個屬性窗口的形式顯示。視頻編碼器完成圖像數(shù)據(jù)編碼后可以通過內(nèi)部的LCD控制器直接輸出數(shù)字視頻信號到液晶顯示器上也可以通過四路54MHz 的DACs 進(jìn)行D/A轉(zhuǎn)換,來提供NTSC/PAL、S-video 等格式的視頻或音頻輸出。

3.電源設(shè)計(jì)

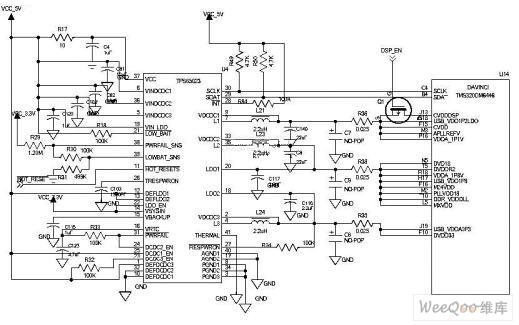

本設(shè)計(jì)采用的是TI 最新的基于達(dá)芬奇技術(shù)的TMS320DM*x DSP 的電源管理芯片TPS65023 在高達(dá)1.5A 的最寬負(fù)載電流范圍內(nèi)可實(shí)現(xiàn)高性能的數(shù)控功能與效率最大化。TPS65023 集成了三個降壓轉(zhuǎn)換器以支持系統(tǒng)的內(nèi)核電壓、外設(shè)、I/O 以及存儲器電壓,還集成了兩個可由外部輸入引腳啟動的通用200mA 線性低壓降 (LDO) 穩(wěn)壓器。每個LDO 的輸入電壓范圍都在2.5 V 至6.5 V 之間,因此既可通過其中一個集成降壓轉(zhuǎn)換器供電,也能直接通過電池供電。

在本設(shè)計(jì)中TPS65023 的VDCDC1 管腳輸出1.2V 電壓用于DM*6 的內(nèi)核供電,VDCDC2 管腳輸出1.8V 電壓用于DM*6 的存儲器接口供電,VDCDC3 管腳輸出3.3V 電壓用于DM*6 的外設(shè)接口供電。由于TPS65023 只提供1A/1.8V 電壓不夠供應(yīng)兩片DDR2 SDRAM,故還需一個輸出1.8V 的電源管理芯片來為DDR2 供電,此系統(tǒng)選用的是LTC3412A 輸出電流3A。這樣用兩個電源管理芯片就能滿足系統(tǒng)供電。TPS65023 與達(dá)芬奇DM*6 的接口電路如圖3 所示。

圖3 TPS65023 與DM*6 的接口電路

4.軟件實(shí)現(xiàn)

達(dá)芬奇軟件架構(gòu)涵蓋低級的OS 驅(qū)動程序乃至應(yīng)用API。在達(dá)芬奇軟件平臺中可以細(xì)分為多任務(wù)的CODEC, 即視頻(Video) 、影像(Image) 、語音(Speech) 、音頻(Audio),統(tǒng)稱VISA。另外還包含具有多媒體框架組件的CODEC 引擎遠(yuǎn)程服務(wù)器。由此構(gòu)成的信號處理層(SPL) 一方面通過VISA API 接口與應(yīng)用層(APL)連接,另一方面則通過DSP/BIOS 與底層內(nèi)核溝通。APL 包含客戶增值差異化設(shè)計(jì)軟件模塊,并通過Linux API 溝通底層內(nèi)核的許多外圍接口驅(qū)動。

eXpressDSP 配置工具的使用使得配置一個CODEC 的過程極其簡單,下面就是一個完整的應(yīng)用程序開發(fā)步驟:

第一步,開發(fā)并完成Codec。就是要開發(fā)音視頻編解碼的核心算法,按照xDM 標(biāo)準(zhǔn)封裝成為Codec 庫,Codec 主要完成音視頻的核心算法,應(yīng)用程序運(yùn)行時被調(diào)用,并不參與其他功能。

第二步,將Codec 集成到Codec Engine 中。將第一步開發(fā)完成的Codec 或已有的符合xDM 的Codec 集成到Codec Engine 中,這一步需要配置兩個JavaScript. 的腳本文件,其中一個腳本文件表明了,Codec 的使用和配置信息,文件名一般為*.cfg, 另一個描述了Codec 在達(dá)芬奇上的內(nèi)存分配的配置,文件名一般為*tcf ,配置好這兩個文件后,使用make 命令即可生成Codec Engine, 其文件名一般為*.X64P 。可被應(yīng)用程序直接調(diào)用。

第三步,開發(fā)音視頻應(yīng)用程序,并在其中調(diào)用Codec Engine 。在Linux 下開發(fā)音視頻應(yīng)用程序,包括用戶界面,音視頻的采集、播放、同步等,其中完成對Codec Engine 的調(diào)用,應(yīng)用程序也要完成一個擴(kuò)展名為cfg 的腳本配置文件,以表明對Codec Engine 的使用狀況。

第四步,加載DSPLINK 和CMEM 模塊,運(yùn)行應(yīng)用程序至此一個完整的達(dá)芬奇音視頻應(yīng)用程序就完成了,其中許多過程是通過腳本文件配置完成的,過程非常簡單易懂,下面我們需要在達(dá)芬奇上運(yùn)行它,首先要加載DSPLINK 和CMEM 兩個驅(qū)動程序模塊,其中DSPLINK 主要實(shí)現(xiàn)了arm 和dsp 的底層通信,而CMEM 則主要是完成了在物理段上分配連續(xù)內(nèi)存的功能,加載完這兩個模塊,這樣便可以直接運(yùn)行已完成的應(yīng)用程序。

5.結(jié)論

基于TMS320DM*6 為核心處理器的數(shù)字視頻系統(tǒng)已經(jīng)實(shí)現(xiàn)并且功能強(qiáng)大,性能穩(wěn)定,擴(kuò)展性強(qiáng),功耗低,能很好的加速數(shù)字視頻創(chuàng)新。本文的創(chuàng)新點(diǎn):1.基于TI 強(qiáng)大的達(dá)芬奇處理器(雙核)能夠?qū)崿F(xiàn)H.264 等復(fù)雜的編解碼。2.利用TI 專門針對達(dá)芬奇供電的電源管理芯片TPS65023 為其供電,很好的解決干擾、EMI/EMC 的問題而且還能達(dá)到功耗低的效果。

-

芯片

+關(guān)注

關(guān)注

459文章

52282瀏覽量

437449 -

數(shù)字視頻

+關(guān)注

關(guān)注

0文章

109瀏覽量

19581 -

電池

+關(guān)注

關(guān)注

84文章

11017瀏覽量

134256

發(fā)布評論請先 登錄

請問TPS65023的I2C接口可以不使用嗎?

如何設(shè)計(jì)數(shù)字視頻監(jiān)控系統(tǒng)?

開源硬件-TIDA-00604-采用 TPS65023 的 Altera Cyclone III FPGA 電源 PCB layout 設(shè)計(jì)

開源硬件-TIDA-00605-采用 TPS65023 的 Altera Cyclone IV FPGA 電源 PCB layout 設(shè)計(jì)

TPS65023在多電壓便攜式產(chǎn)品中的應(yīng)用

基于SOPC的數(shù)字視頻監(jiān)控系統(tǒng)設(shè)計(jì)

數(shù)字視頻圖像采集和存儲的ASIC芯片設(shè)計(jì)

TPS65023,TPS65023B,pdf(Power M

TPS65023-Q1,pdf(Power Manageme

基于TPS65023為OMAP 3供電的電源電路設(shè)計(jì)

基于Lorenz混沌系統(tǒng)的數(shù)字視頻加密

數(shù)字視頻監(jiān)控系統(tǒng)中預(yù)錄像的實(shí)現(xiàn)

達(dá)芬奇技術(shù)的數(shù)字視頻系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

采用TPS65023的恩智浦i.MX 6電源設(shè)計(jì)

使用TPS65023的NXP i.MX 7電源設(shè)計(jì)

如何利用TPS65023芯片實(shí)現(xiàn)數(shù)字視頻系統(tǒng)的設(shè)計(jì)?

如何利用TPS65023芯片實(shí)現(xiàn)數(shù)字視頻系統(tǒng)的設(shè)計(jì)?

評論