AD9054 高速A/D采集技術(shù)已在許多領(lǐng)域得到愈來(lái)愈廣泛的應(yīng)用,本文將詳細(xì)論述采用CPLD技術(shù)來(lái)實(shí)現(xiàn)120MHz高速A/D采集卡的設(shè)計(jì)方法,該采集卡具有包括負(fù)延遲觸發(fā)在內(nèi)的多種觸發(fā)方式,采用CPLD復(fù)雜可編程邏輯器件(又稱(chēng)FPGA)EPM7128SQC100-7和AD公司的高速模數(shù)轉(zhuǎn)換器(A/D)AD9054BST-135來(lái)實(shí)現(xiàn)。

1 芯片介紹

1.1 EPM7128SQC100-7簡(jiǎn)介

EPM7128SQC100-7內(nèi)含128個(gè)宏單元(或2500個(gè)可用門(mén)),其引腳到引腳的最短傳輸延時(shí)為7ns,采用單+5V電源供電,可通過(guò) JTAG接口實(shí)現(xiàn)在線(xiàn)編程,并帶有可供84個(gè)用戶(hù)使用的I/O腳(其中4個(gè)為專(zhuān)用輸入腳)。該器件采用PQFP-100封裝。其中TDI、TDO、 TMS、TCLK腳為編程腳;GCLK、GOE、GCLEAR、REDIN腳為專(zhuān)用輸入腳;VCCINT、VCCIO腳接+5V電源;GND腳接地; I/O為用戶(hù)可編程輸入輸出腳。在I/O腳作輸出使用時(shí),可由用戶(hù)設(shè)定為0,1和Z三種狀態(tài)。

1.2 AD9054BST-135簡(jiǎn)介

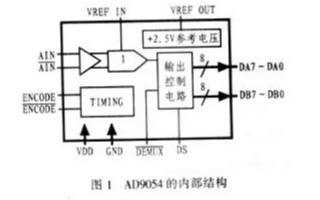

AD9054BST-135是一種低價(jià)位135MSPS的8位A/D轉(zhuǎn)換器,其模擬輸入電壓峰峰值為1V,且內(nèi)置2.5V參考電壓,采用+5V單電源供電,并可與TTL電平接口,具有單8位或雙8位A/D轉(zhuǎn)換結(jié)果輸出模式,采用TQFP-44腳封裝形式,其內(nèi)部結(jié)構(gòu)如圖1所示,各管腳的定義如下:

AIN:模擬電壓輸入正端;

非AIN:模擬電壓輸入負(fù)端;

ENCODE:時(shí)鐘輸入正端;

非ENCODE:時(shí)鐘輸入負(fù)端,通常應(yīng)通過(guò)電容耦合接地;

非DEMUX:輸出數(shù)據(jù)模式設(shè)置引腳。該腳為1時(shí),采用單8位A/D轉(zhuǎn)換結(jié)果輸出模式。該腳為0時(shí),采用雙8位A/D轉(zhuǎn)換結(jié)果輸出模式;

DS:數(shù)據(jù)同步控制引腳,正脈沖輸入;

AD7~DA0:A/D轉(zhuǎn)換輸出;

D B7~DB0:A/D轉(zhuǎn)換輸出;

V REFOUT:+2.5V參考電壓輸出;

V REFIN:參考電壓輸入;

DVD:+5V電源輸入端;

GND:電源地。

使用時(shí),如將接地,則AD9054工作于雙8路數(shù)據(jù)輸出模式。上電后,DA7~DA0及DB7~DB0均以二分之一的ENCODE頻率(即120MHz/2)輸出A/D 轉(zhuǎn)換結(jié)果,因此從DA7~DA0及DB7~DB0讀取的A/D轉(zhuǎn)換結(jié)果,無(wú)法知曉DA口與DB口的數(shù)據(jù)所對(duì)應(yīng)的采樣點(diǎn)在時(shí)序上的先后。這樣,需要加一個(gè)數(shù)據(jù)同步脈沖DS信號(hào),并讓DS正脈沖的后沿后的4個(gè)時(shí)鐘周期上的DA口與DB口同步有效,即在DS后沿的第2N+1與2N+3個(gè)ENCODE上升沿期間輸出第K點(diǎn)采樣值的轉(zhuǎn)換結(jié)果;在DS后沿后第2N+2與2N+4個(gè)ENCODE上升沿期間輸出第K+1點(diǎn)采樣值的轉(zhuǎn)換結(jié)果(注:N≥1,K≥0,K=0對(duì)應(yīng)的采樣值為DS下降沿后ENCODE第一次上升沿時(shí)刻所對(duì)應(yīng)的采樣輸入值)。因此,在施加DS信號(hào)后就可以得知任一時(shí)刻A口數(shù)據(jù)與B口數(shù)據(jù)所對(duì)應(yīng)的采樣點(diǎn)在時(shí)間上的先后順序,以便讀取有用的A/D轉(zhuǎn)換數(shù)據(jù)。

2 系統(tǒng)設(shè)計(jì)原理

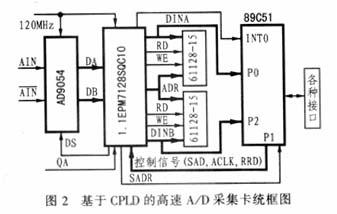

圖2是基于CPLD的高速 A/D采集卡的系統(tǒng)設(shè)計(jì)原理框圖。圖中,89C51送往EPM7128S的控制信號(hào)包括一個(gè)A/D啟動(dòng)信號(hào)SAD、一個(gè)讀SRAM信號(hào)RRD和一個(gè)地址加一控制脈沖ACLK。而EPM7128S送往AD9054的信號(hào)為一個(gè)DS同步信號(hào),送往89C51的信號(hào)為轉(zhuǎn)換結(jié)束信號(hào)(接INT0)和超前觸發(fā)地址串行輸出信號(hào)SADR。

EPM7128S送往61128-15SRAM的信號(hào)包括讀信號(hào)RD、寫(xiě)信號(hào)WE、數(shù)據(jù)信號(hào)DINA0~7和DINB0~7以及地址信號(hào)ADR0~16。其中兩片SRAM的地址信號(hào)共用。為了節(jié)省EPM7128S的I/O口線(xiàn),可將61128-15的片選線(xiàn)接地。

QA信號(hào)為外觸發(fā)A/D轉(zhuǎn)換控制信號(hào)。

在本文所介紹的A/D數(shù)據(jù)采集卡中,負(fù)延遲觸發(fā)存貯深度為2k字節(jié)。上電復(fù)位后, 89C51向EPM7128S發(fā)一個(gè)A/D啟動(dòng)信號(hào)時(shí),EPM7128S也會(huì)發(fā)一個(gè)DS同步脈沖給AD9054,在四個(gè)時(shí)鐘后,EPM7128S輸出WE 信號(hào)有效,同時(shí)將AD9054輸出的雙8位數(shù)據(jù)信號(hào)以60MHz的頻率經(jīng)鎖存處理后送往SRAM,每鎖存AD9054數(shù)據(jù)一次(2字節(jié))將地址 ADR0~13加1。當(dāng)?shù)刂窞?FF時(shí)(即1k),清地址計(jì)數(shù)器以使其為零。此后,地址計(jì)數(shù)器仍以60MHz的頻率加1計(jì)數(shù),而鎖存器仍以60MHz的頻率鎖存雙8位數(shù)據(jù)并寫(xiě)入SRAM。當(dāng)?shù)刂窞?FF時(shí)再一次清零,在外觸發(fā)信號(hào)QA到來(lái)之前,CPLD就這樣控制著整個(gè)電路以使其在2k字節(jié)存貯深度內(nèi)作超前循環(huán)采集。當(dāng)某一時(shí)刻的QA信號(hào)到來(lái)時(shí),CPLD首先將此時(shí)的地址信號(hào)的前10位ADR0~9鎖存,隨后將地址計(jì)數(shù)器置為400H,而后地址計(jì)數(shù)器仍以 60MHz的頻率加1計(jì)數(shù),而鎖存器也以60MHz的頻率鎖存雙8位數(shù)據(jù)并寫(xiě)入SRAM。當(dāng)?shù)刂酚?jì)數(shù)器為1FFFFH(即128k)時(shí),地址計(jì)數(shù)器停止計(jì)數(shù),鎖存器停止鎖存數(shù)據(jù)并對(duì)外輸出高阻態(tài),CPLD向89C51送出轉(zhuǎn)換結(jié)束信號(hào)ADEND,并置WE信號(hào)無(wú)效。

當(dāng)89C51收到ADEND中斷信號(hào)后,就可以讀取SRAM中的A/D數(shù)據(jù)以及CPLD中的超前地址ADR0~9。首先89C51將送出一個(gè)RRD信號(hào)給 EPM7128S,EPM7128S收到RRD信號(hào)后立即置RD信號(hào)有效,同時(shí)將地址計(jì)數(shù)器清零。此時(shí),兩片SRAM均輸出地址為0的單元的數(shù)據(jù),同時(shí)由 CPLD的SADR線(xiàn)輸出負(fù)延遲觸發(fā)地址ADR0~9中的ADR0位。89C51則可通過(guò)P0和P2口由DINA和DINB分別讀取SRAM中的數(shù)據(jù),并通過(guò)P1口由SADR讀地址ADR0位。此后89C51便向EPM7128S發(fā)出一個(gè)地址加一脈沖ACLK,EPM7128S在收到這個(gè)ACLK脈沖后使 ADR0~13加1,同時(shí)CPLD由SADR線(xiàn)輸出負(fù)延遲觸發(fā)地址ADR0~9中的ADR1位。這樣,89C51便可通過(guò)不斷地發(fā)ACLK脈沖來(lái)使P0、 P2口的DINA和DINB分別讀取SRAM中的數(shù)據(jù),并通過(guò)P1口來(lái)由SADR讀負(fù)延遲觸發(fā)地址ADR0~9。

3 CPLD部分的設(shè)計(jì)

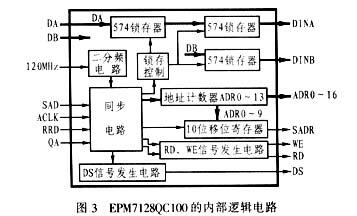

由于EPM7128SQC100的內(nèi)部邏輯電路是整個(gè)系統(tǒng)設(shè)計(jì)的關(guān)鍵,因此,了解EPM7128SQC100的內(nèi)圖2基于CPLD的高速A/D采集卡統(tǒng)框圖基于復(fù)雜可編程邏輯器件(CPLD)的120MHz高速A/D采集卡的設(shè)計(jì)部結(jié)構(gòu)十分重要。圖3是其內(nèi)部結(jié)構(gòu)原理框圖。

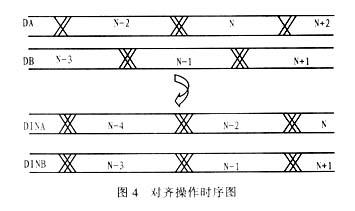

圖3中有三個(gè)574鎖存器,其作用是將AD9054輸出的在時(shí)序上未對(duì)齊的DA、DB兩組數(shù)據(jù)變?yōu)闀r(shí)序上對(duì)齊的兩組數(shù)據(jù)DINA、DINB,圖4是其對(duì)齊操作時(shí)序圖。

將120MHz信號(hào)二分頻后所得到的60MHz信號(hào)可作為整個(gè)邏輯電路的工作頻率。工作時(shí),同步控制電路首先將外輸入信號(hào)與內(nèi)部60MHz信號(hào)同步,然后送往各單元電路。地址計(jì)數(shù)器的工作情況有兩種:一是進(jìn)行A/D采集時(shí)以60MHz頻率計(jì)數(shù),二是89C51讀數(shù)時(shí)以ACLK脈沖頻率計(jì)數(shù)。RD、WE發(fā)生電路的作用是當(dāng)89C51發(fā)SAD信號(hào)時(shí),電路輸出WE信號(hào)有效,RD信號(hào)無(wú)效;而當(dāng)89C51發(fā)RRD信號(hào)時(shí),電路輸出RD信號(hào)有效,WE信號(hào)無(wú)效。 DS信號(hào)發(fā)生電路的作用是在收到89C51的SAD信號(hào)時(shí)發(fā)送一個(gè)DS正脈沖。

10位移位寄存器的作用是當(dāng)外觸發(fā)信號(hào)QA到達(dá)時(shí)將地址計(jì)數(shù)器中的ADR0~9鎖存,當(dāng)收到RRD信號(hào)后,系統(tǒng)每接收一個(gè)ACLK脈沖便將寄存器移位輸出一次,順序是低位在前。 4 單片機(jī)的軟件設(shè)計(jì)

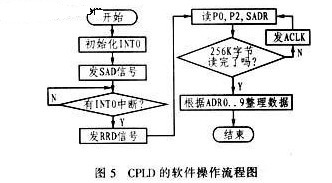

單片機(jī)的軟件設(shè)計(jì)主要是負(fù)責(zé)把各種控制信號(hào)和數(shù)據(jù)送給CPLD,并把采集到的數(shù)據(jù)通過(guò)接口送到上位機(jī)或其它設(shè)備。本卡中的接口有串口和并口兩種類(lèi)型。對(duì)CPLD的操作的軟件流程框圖如圖5所示。

由于采用了負(fù)延遲觸發(fā),所以由SRAM所讀取的256k字節(jié)并不是按時(shí)間的先后順序存放的,因此必須進(jìn)行重新排序整理。

5 注意事項(xiàng)

在利用本文的設(shè)計(jì)方法進(jìn)行120MHz A/D設(shè)計(jì)時(shí)應(yīng)注意以下幾點(diǎn):

(1)應(yīng)選用高速器件。

(2)電路中的器件布局要合理,高頻信號(hào)線(xiàn)應(yīng)盡量的短。

(3)進(jìn)行時(shí)序分析時(shí)應(yīng)充分考慮器件延時(shí),必要時(shí)應(yīng)考慮長(zhǎng)線(xiàn)傳輸延時(shí),這也是高頻信號(hào)線(xiàn)應(yīng)盡量短些的原因之一。

(4)盡量采用同步設(shè)計(jì)。也就是說(shuō)整個(gè)電路要盡最大可能按某一高頻時(shí)鐘同步工作。本電路的同步時(shí)鐘為60MHz。

(5)電路內(nèi)部要盡量濾去毛刺。特別是觸發(fā)器、計(jì)數(shù)器的時(shí)鐘信號(hào)、清零信號(hào)和置位信號(hào),更應(yīng)如此。

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

9036瀏覽量

151653 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

171438 -

可編程邏輯器件

+關(guān)注

關(guān)注

5文章

145瀏覽量

30625

發(fā)布評(píng)論請(qǐng)先 登錄

基于復(fù)雜可編程邏輯器件(CPLD)的120MHZ高速A/D采集卡的設(shè)計(jì)

如何利用CPLD技術(shù)來(lái)設(shè)計(jì)120MHz高速A/D采集卡?

如何采用CPLD技術(shù)來(lái)實(shí)現(xiàn)120MHz高速A/D采集卡的設(shè)計(jì)?

基于PCI總線(xiàn)的高速數(shù)據(jù)采集卡系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

基于復(fù)雜可編程邏輯器件(CPLD)的120MHZ高速AD采集

基于CPLD的120MHz高速AD采集卡的設(shè)計(jì)

基于FPGA/CPLD和USB技術(shù)的無(wú)損圖像采集卡

FPGA/CPLD與USB技術(shù)的無(wú)損圖像采集卡

多種觸發(fā)功能的可編程高速數(shù)據(jù)采集模塊

CPLD在視頻采集卡中的應(yīng)用

基于FPGA_CPLD和USB技術(shù)的無(wú)損圖像采集卡

采用FPGA器件和模數(shù)轉(zhuǎn)換器實(shí)現(xiàn)A/D數(shù)據(jù)采集卡的設(shè)計(jì)

基于EPM7128SQC100和AD9054BST實(shí)現(xiàn)120MHz高速A/D采集卡的設(shè)計(jì)

AD采集卡設(shè)計(jì)方案:630-基于PCIe的高速模擬AD采集卡

高速視頻采集卡設(shè)計(jì)方案:620-基于PCIe的高速視頻采集卡

采用CPLD技術(shù)實(shí)現(xiàn)有多種觸發(fā)方式的120MHz高速A/D采集卡設(shè)計(jì)

采用CPLD技術(shù)實(shí)現(xiàn)有多種觸發(fā)方式的120MHz高速A/D采集卡設(shè)計(jì)

評(píng)論