視頻監(jiān)控以其直觀、方便、信息內(nèi)容豐富而廣泛應(yīng)用于許多場(chǎng)合。視頻監(jiān)控成為人們生活中不可缺少的技術(shù)。在一些危險(xiǎn)場(chǎng)所,用視頻監(jiān)控代替人工監(jiān)視,可以保證人們的生命安全。鑒于一路視頻的視野范圍有限,要充分收集目標(biāo)的信息,就需要有多路視頻來(lái)對(duì)同一個(gè)物體在不同方位進(jìn)行監(jiān)控。因此需要有一個(gè)良好的控制手段,確保多路視頻控制穩(wěn)定,可靠。針對(duì)織布機(jī)告警系統(tǒng)的需求,提出一種基于FPGA的多路視頻通道控制系統(tǒng),本系統(tǒng)設(shè)計(jì)利用FPGA間接控制2塊MAX4312選通所需要的視頻通道,實(shí)現(xiàn)各個(gè)視頻通道間相互切換。根據(jù)開(kāi)關(guān)控制信號(hào)的設(shè)計(jì)思想在FPGA中對(duì)撥動(dòng)開(kāi)關(guān)輸入信號(hào)做去抖動(dòng)處理,然后對(duì)不同的開(kāi)關(guān)操作進(jìn)行編碼,最后將信號(hào)送給DSP進(jìn)行處理。

1 系統(tǒng)總體結(jié)構(gòu)

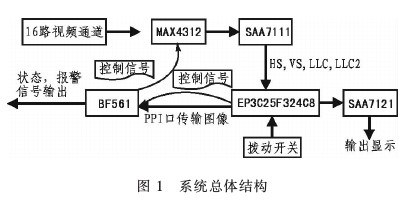

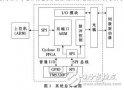

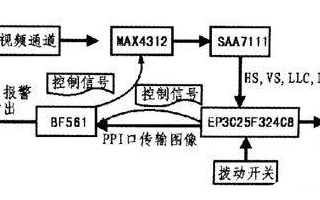

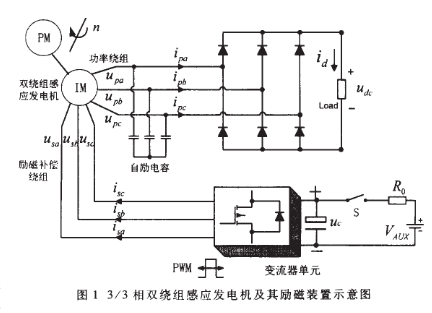

系統(tǒng)總體結(jié)構(gòu)如圖1所示。在1臺(tái)工業(yè)織布機(jī)上安裝了16個(gè)CCD圖像傳感器對(duì)布匹進(jìn)行圖像監(jiān)控,通過(guò)2片MAX4312選擇16路圖像視頻信號(hào)中的一路,經(jīng)可編程視頻輸入器件SAA7111處理后從VP0輸出數(shù)字圖像信號(hào)。同時(shí)SAA7111輸出相應(yīng)的行、場(chǎng)同步信號(hào)HS,VS以及與HS鎖定的時(shí)鐘信號(hào)LLC、LLC2,利用這些信號(hào)在EP3C25F324C8中對(duì)圖像進(jìn)行預(yù)處理。然后將處理后的圖像通過(guò)PPI口送給BF561中進(jìn)行算法處理,最后將處理結(jié)果送給報(bào)警和狀態(tài)指示裝置,實(shí)現(xiàn)織布機(jī)告警功能。為了使圖像監(jiān)控更方便,該系統(tǒng)設(shè)計(jì)增添了電平撥動(dòng)開(kāi)關(guān)和脈沖撥動(dòng)開(kāi)關(guān)。電平開(kāi)關(guān)使輸入圖像停止切換,固定于其中一路視頻輸人圖像。脈沖開(kāi)關(guān)可以左右撥動(dòng),每次向左或向右撥動(dòng)都會(huì)產(chǎn)生一個(gè)很短的上升沿脈沖,同時(shí)圖像向前或向后進(jìn)行切換,實(shí)現(xiàn)手動(dòng)選擇視頻輸入通道的功能。

2 軟件模塊設(shè)計(jì)

2.1 開(kāi)關(guān)控制信號(hào)

實(shí)際工程中,BF56l連接在FPGA上的PF引腳比較少。為了節(jié)約資源,只通過(guò)BF561中的BF9來(lái)識(shí)別2個(gè)撥動(dòng)開(kāi)關(guān)的動(dòng)作。因此首先需要將2個(gè)撥動(dòng)開(kāi)關(guān)輸入信號(hào)在FPGA中進(jìn)行處理整合,得到合適的信號(hào)。

本系統(tǒng)開(kāi)關(guān)控制信號(hào)的設(shè)計(jì)思想:由于設(shè)計(jì)這個(gè)信號(hào)的目的是識(shí)別開(kāi)關(guān)控制動(dòng)作。因此,只要任何一個(gè)開(kāi)關(guān)發(fā)生了動(dòng)作就需要產(chǎn)生一個(gè)脈沖。如果只有脈沖信號(hào)就只能知道開(kāi)關(guān)發(fā)生了動(dòng)作,而不知道是哪個(gè)開(kāi)關(guān)發(fā)生了什么動(dòng)作。所以,要識(shí)別具體是哪個(gè)開(kāi)關(guān)發(fā)生了什么動(dòng)作就必須配合雙口RAM中的數(shù)據(jù)進(jìn)行解碼。該系統(tǒng)設(shè)計(jì)的脈沖持續(xù)時(shí)間對(duì)BF561來(lái)說(shuō)并不重要,只要BF561能識(shí)別這個(gè)脈沖即可。由于系統(tǒng)中的2個(gè)撥動(dòng)開(kāi)關(guān),一個(gè)是電平撥動(dòng)開(kāi)關(guān),另一個(gè)是脈沖撥動(dòng)開(kāi)關(guān),因此,只要根據(jù)電平撥動(dòng)開(kāi)關(guān)的動(dòng)作制作相應(yīng)的脈沖信號(hào),再用這個(gè)信號(hào)與脈沖撥動(dòng)開(kāi)關(guān)產(chǎn)生的原始信號(hào)邏輯相與,就能得到所需要的目的信號(hào)。

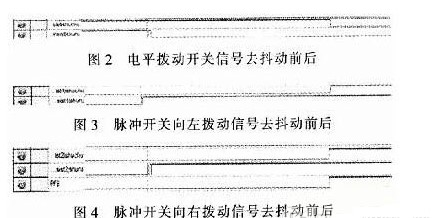

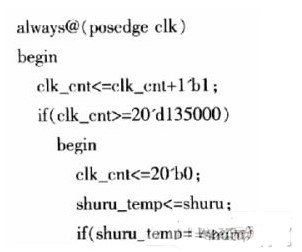

由于撥動(dòng)開(kāi)關(guān)是機(jī)械觸點(diǎn),當(dāng)其斷開(kāi)、閉合時(shí)會(huì)有相應(yīng)的前沿、后沿抖動(dòng),為了使每次動(dòng)作都只做一次響應(yīng),就必須對(duì)原始開(kāi)關(guān)信號(hào)做去抖動(dòng)處理。抖動(dòng)信號(hào)可以分為2種:一種是時(shí)間很短的干擾信號(hào),如高頻毛刺;另一種是時(shí)間較長(zhǎng)的干擾信號(hào),如開(kāi)關(guān)抖動(dòng)。這里的撥動(dòng)開(kāi)關(guān)都是人為操作,因此每次觸發(fā)的時(shí)間都不會(huì)很短,一般小于10 Hz。根據(jù)上述分析開(kāi)關(guān)抖動(dòng)信號(hào)屬于后一種。因此在每次開(kāi)關(guān)操作后,對(duì)其產(chǎn)生的信號(hào)進(jìn)行連續(xù)采樣,如果每次采樣都是低電平或者都是高電平,就認(rèn)為此信號(hào)不是抖動(dòng),確實(shí)開(kāi)關(guān)狀態(tài)發(fā)生了變化。整個(gè)設(shè)計(jì)過(guò)程使用Verilog硬件描述語(yǔ)言編寫(xiě),然后在QuartusⅡ平臺(tái)上編譯,并采用SignalTapⅡLogic Arlalvzer對(duì)信號(hào)采樣分析,調(diào)試通過(guò)后連同其他程序一起燒寫(xiě)進(jìn)FPGA的配置器件EPCSl6中。圖2~圖4分別是各個(gè)開(kāi)關(guān)動(dòng)作去抖動(dòng)前和去抖動(dòng)后的實(shí)時(shí)信號(hào)采樣圖。去抖動(dòng)模塊中的部分代碼如下:

其中,clk為13.5 MHz頻率的時(shí)鐘信號(hào),clk_cnt為采樣時(shí)間間隔計(jì)數(shù)器,當(dāng)clk_cnt為135 000時(shí)采樣1次,即每隔10 ms采樣1次。寄存器shuru_temp存儲(chǔ)前一次開(kāi)關(guān)信號(hào)狀態(tài),shum存儲(chǔ)當(dāng)前開(kāi)關(guān)信號(hào)狀態(tài)。如果shuru_temp的值等于shtlm的值,則計(jì)數(shù)器test_cnt自動(dòng)加l。如果連續(xù)4次采樣值相等,即test_cnt=4時(shí)去抖動(dòng)輸出才隨輸入變化。

用電平撥動(dòng)開(kāi)關(guān)信號(hào)作為輸入,制作了一個(gè)脈沖信號(hào)用于識(shí)別開(kāi)關(guān)動(dòng)作,其代碼如下:

代碼中寄存器level_contrl_TEMP存儲(chǔ)level_contrl延時(shí)256個(gè)時(shí)鐘周期后的信號(hào),然后用level_eontrl_TEMP中存儲(chǔ)的信號(hào)與level_co-ntrl的值相異或產(chǎn)生所需要的脈沖信號(hào)。

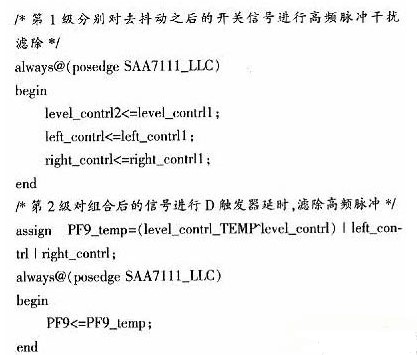

調(diào)試中發(fā)現(xiàn),去抖動(dòng)后的信號(hào)經(jīng)常混有持續(xù)時(shí)間很短的高頻脈沖干擾信號(hào),因此設(shè)計(jì)中使用兩級(jí)D觸發(fā)器延時(shí)來(lái)徹底消除高頻脈沖干擾,其程序代碼如下:

2.2 雙口RAM及開(kāi)關(guān)信號(hào)編碼設(shè)計(jì)

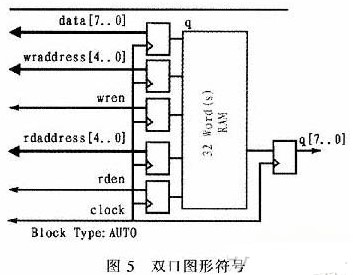

雙口RAM分為真、假2種雙口。真雙口2個(gè)端口都可以讀寫(xiě),互不干擾。本次設(shè)計(jì)根據(jù)實(shí)際需要,添加的RAM模塊一端只讀,另一端只寫(xiě),讀寫(xiě)互不干擾。根據(jù)上述分析可知,開(kāi)關(guān)控制信號(hào)只能知道有開(kāi)關(guān)控制動(dòng)作發(fā)生,但是不能識(shí)別具體哪個(gè)開(kāi)關(guān)發(fā)生了動(dòng)作。因此,設(shè)計(jì)中首先利用MegaWizardPlug_In Manager中的宏功能塊RAM:2_PORT產(chǎn)生1個(gè)雙口RAM存儲(chǔ)塊,然后對(duì)這個(gè)宏功能模塊的參數(shù)進(jìn)行適當(dāng)調(diào)整,產(chǎn)生一個(gè)滿足自己特定要求的模塊,如圖5所示。

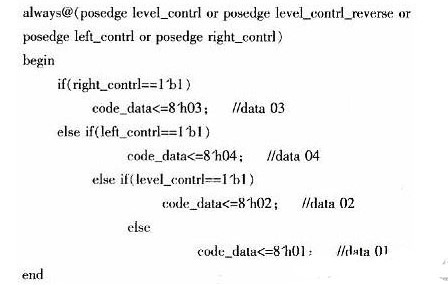

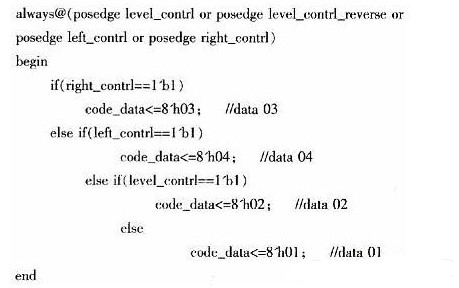

設(shè)計(jì)過(guò)程中,首先將開(kāi)關(guān)動(dòng)作進(jìn)行編碼。然后將編碼后的數(shù)據(jù)存進(jìn)空間大小為8的雙口RAM中。當(dāng)BF561檢測(cè)到PF9上的脈沖后,在PF中斷中讀取RAM中指定地址的數(shù)據(jù),然后根據(jù)這個(gè)數(shù)據(jù)進(jìn)行開(kāi)關(guān)狀態(tài)解碼并按解碼后的控制信息對(duì)2塊MAX4312器件進(jìn)行操作以控制視頻通道。對(duì)開(kāi)關(guān)動(dòng)作進(jìn)行的編碼程序代碼如下:

整個(gè)設(shè)計(jì)有4種開(kāi)關(guān)動(dòng)作,程序中分別將其編碼成數(shù)據(jù)0l、02、03、04,然后將編碼后的這4個(gè)數(shù)據(jù)存入雙口模塊中,等待BF561來(lái)讀取并進(jìn)行解碼。圖6是SignalTapⅡLogic Analyzer中對(duì)脈沖開(kāi)關(guān)向右撥動(dòng)后存入RAM中的數(shù)據(jù)進(jìn)行采樣。

程序中RAM的讀信號(hào)rden_signal是由DSP發(fā)送的地址信號(hào)DSP_A、BANK選擇信號(hào)DSP_AMSl以及DSP讀信號(hào)DSP_ARE進(jìn)行控制的。當(dāng)DSP不從雙口讀取數(shù)據(jù)時(shí),必須給DSP的數(shù)據(jù)線賦值高阻,以免影響SDRAM對(duì)DSP數(shù)據(jù)線的操作。賦值指令如下:assignDSP_D=(rden_signal=l ‘b1)?DSP_D_TEMP;8 ’hzz;其中DSP_D_TEMP是從雙口中讀取的數(shù)據(jù)。

3 結(jié)論

首先介紹了整個(gè)系統(tǒng)的工業(yè)背景和硬件架構(gòu),然后著重闡述了怎樣在FPGA中處理開(kāi)關(guān)控制信號(hào),以達(dá)到可靠響應(yīng)每個(gè)開(kāi)關(guān)動(dòng)作的目的。整個(gè)設(shè)計(jì)程序是在QuartusⅡ平臺(tái)上用Verilog硬件描述語(yǔ)言編寫(xiě),利用QuartusⅡ中的下載工具和SignalTapⅡLogic Analyzer工具進(jìn)行下載、實(shí)時(shí)采樣,并多次調(diào)試驗(yàn)證。本次設(shè)計(jì)已經(jīng)成功應(yīng)用于布機(jī)告警系統(tǒng)中,每次撥動(dòng)開(kāi)關(guān)都能準(zhǔn)確、可靠的切換視頻通道。雖然此系統(tǒng)中只有兩種開(kāi)關(guān),但是整個(gè)程序的設(shè)計(jì)思想對(duì)多種開(kāi)關(guān)控制也是通用的,只需在細(xì)節(jié)上稍作改變就能識(shí)別多種開(kāi)關(guān)動(dòng)作。

-

dsp

+關(guān)注

關(guān)注

554文章

8059瀏覽量

350496 -

FPGA

+關(guān)注

關(guān)注

1630文章

21799瀏覽量

606120 -

圖像傳感器

+關(guān)注

關(guān)注

68文章

1919瀏覽量

129708

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于DSP+FPGA多視頻通道的切換控

DSP+FPGA電機(jī)控制系統(tǒng)

一種基于DSP+FPGA的多通道視頻監(jiān)控系統(tǒng)設(shè)計(jì)

一種基于FPGA的多通道頻率測(cè)量系統(tǒng)的實(shí)現(xiàn)方法介紹

基于DSP+FPGA的控制系統(tǒng)方案設(shè)計(jì)介紹

基于FPGA怎么實(shí)現(xiàn)各個(gè)視頻通道間相互切換?

振動(dòng)控制系統(tǒng)中DSP后向通道的設(shè)計(jì)與實(shí)現(xiàn)

基于多DSP架構(gòu)的電機(jī)控制系統(tǒng).pdf

基于DSP與FPGA的多視頻通道的切換控制

基于DSP和FPGA的多通道CMOS圖像監(jiān)控系統(tǒng)

基于DSP和FPGA的多軸運(yùn)動(dòng)控制系統(tǒng)設(shè)計(jì)

基于CDMA多通道技術(shù)的視頻監(jiān)控系統(tǒng)

基于DSP+FPGA多視頻通道視頻監(jiān)控系統(tǒng)剖析

一種基于FPGA的多路視頻通道控制系統(tǒng)設(shè)計(jì)總體分析

采用DSP和FPGA器件實(shí)現(xiàn)電機(jī)勵(lì)磁控制系統(tǒng)的設(shè)計(jì)

基于FPGA器件與DSP技術(shù)實(shí)現(xiàn)視頻多通道的控制系統(tǒng)設(shè)計(jì)

基于FPGA器件與DSP技術(shù)實(shí)現(xiàn)視頻多通道的控制系統(tǒng)設(shè)計(jì)

評(píng)論