引言

無人機廣泛應用于軍事偵察以及民用測繪等領域,其中的機載視頻圖像系統是機載電子系統中的重要環節之一。無人機在高空飛行中對地面景物攝像,所得圖像幀內目標像素小且目標數量大,這要求增大圖像分辨率以提高目標物體的辨識度。此時數據量隨之顯著增加,與有限的無線帶寬資源成為矛盾,故要求應用高效的視頻編解碼技術。在偵察等特殊應用領域要求視頻傳輸的實時性,此時需要保證實時的視頻編解碼以及較小的圖像延遲。在需多路視頻傳輸且總數據率固定的情況下,可通過降低單路視頻分辨率或提高單路壓縮比來實現,故系統應可動態切換分辨率和壓縮比,具備較大的靈活性。無人機與地面的通信中,除了要回傳視頻數據以外,還要向地面傳輸飛行器本身的下行遙測數據,若采用兩個獨立信道會導致傳輸效率較低,此時設計一個包括傳統遙測數據和視頻數據的廣義遙測系統成為必需。

本文設計并實現了一種基于FPGA和DSP的機載高清視頻圖像系統,包括機載設備端和地面站端兩部分,最高支持分辨率為1 280× 720,每秒25幀的MPEG-4實時視頻編解碼,碼速率在5 Mbps以下。并可通過上行遙控指令動態切換圖像分辨率和視頻碼率,同時實現了視頻數據與遙測數據的組幀傳輸。

本文首先對機載視頻圖像遙測系統進行概述,提出了系統的總體實現結構。然后具體給出系統的設計,分為硬件平臺和程序算法兩部分。硬件平臺設計包括機載端視頻采集、FPGA和DSP處理器和地面端CPCI總線接口的設計,程序算法設計包括視頻編解碼算法、機載端DSP程序和地面端上位機軟件的設計。文章最后給出了系統掛飛實驗的結果并作以總結。

1 系統概述

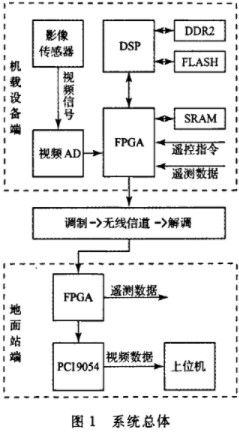

機載視頻圖像系統主要由機載設備端和地面站端兩部分組成,系統總體結構圖如圖1所示。

1)機載設備端

視頻AD將影像傳感器輸出的高清視頻模擬信號進行模數轉換傳遞給FPGA,FPGA將預處理后的原始數字視頻數據傳遞給DSP進行實時視頻編碼,DSP完成視頻編碼后將壓縮碼流回傳給FPGA,在FPGA 中,壓縮視頻碼流與下行遙測數據組幀后進入調制部分;同時上行遙控指令進入FPGA,對圖像分辨率、視頻碼率進行控制。

2)地面站端

解調后的數據進入FPGA,FPGA將視頻數據與遙測數據分離,其中遙測數據進入后續的分析處理,視頻數據經PCI9054,通過CPCI接口上傳給上位機,上位機完成對視頻壓縮碼流的實時解碼播放以及存儲回放。

2 系統設計

2.1 硬件平臺

2.1.1 機載端視頻采集

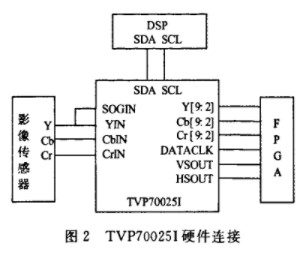

高清模擬視頻信號為保證信號質量,常采用分量輸出格式,如亮度信號(Y)和色差信號(Cr、Cb)三分量輸出,同時場同步和行同步信號可采取疊加在分量信號上的內同步方式輸出。本系統中高清視頻信號采用720 P(1 280×720)格式,25幀/秒,選用TI公司的視頻ADC芯片TVP70025I完成該高清模擬視頻的模數轉換,采樣精度及方式選取為8位,4:2:2(Y:Cb:Cr)采樣。TVP70025I與外部器件連接關系如圖2所示。TVP7OO25I輸出數字化視頻分量(Y、Cb和Cr)、數據時鐘(DATACLK)、場同步(VS0UT)和行同步(HSOUT)信號給FPGA,DSP通過I C總線對TVP70025I內部寄存器進行初始化設置,并啟動模數轉換過程。

2.1.2 機載端DSP+FPGA處理器

機載端處理部分主要完成數字視頻信號獲取、視頻壓縮編碼和遙控遙測接口功能,考慮到DSP強大的數字信號處理能力和FPGA 的大規模邏輯設計能力,系統采用FPGA+DSP的硬件架構。

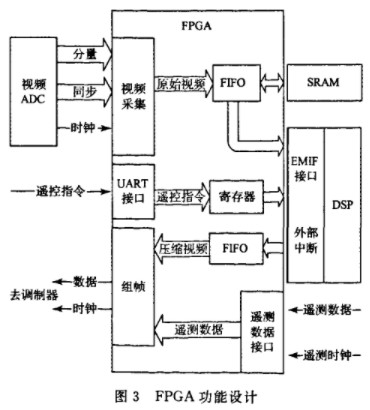

FPGA 選用Altera 公司StratixII 系列芯片EP2S30F672C5,該芯片有豐富的邏輯資源和嵌人式存儲器,支持LVTTL、LVDS等接口電平標準。主要功能設計如圖3所示。

包括以下3個方面:

1)數字視頻獲取

FPGA通過TVP70025I輸出的場同步和行同步信號判斷一場和一行視頻的起始,接收原始視頻數據(Y/Cb/Cr)并存人FPGA 內部開辟的FIFO之中,考慮到數據傳輸的高效性,需緩存若干行圖像并一次性傳遞至DSP,由于FPGA內部存儲器有限,故外掛SRAM 作為數據緩沖。

2)DSP與FPGA間數據傳輸

DSP與FPGA之間通過DSP的EMIFA 接口連接,FPGA內開辟FIFO 或者寄存器,DSP通過EMIFA讀寫FIFO或寄存器內的數據實現數據傳輸。本系統中分別開辟原始視頻FIFO(Y/Cb/Cr 3個)、壓縮視頻FIFO和遙控指令寄存器,對應于DSP中的5個地址空間,以地址線的最高3位進行區分。考慮到最大數據吞吐率為原始視頻的傳遞,EMIFA 數據寬度設為32位,數據時鐘選取4O M Hz。

3)遙控及遙測

本系統中可接受地面測控站傳遞的上行遙控指令,通過改變采樣方式,對視頻分辨率進行切換,包括QCIF(176×144)、CIF(352×288)、標清(720×576)和高清(1 280×720)4種模式。同時可根據遙控指令改變編碼算法中的參數,進而實現視頻數據的碼率控制,分為最高至最低5個碼率等級。

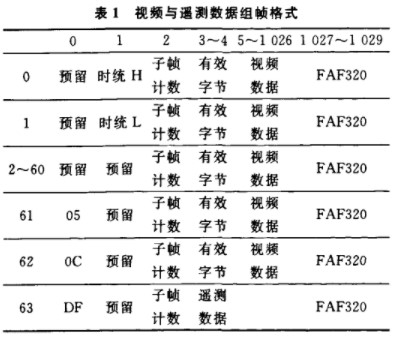

編碼后的視頻數據與下行遙測數據進行組幀,作為整體碼流進入調制階段。系統中設計幀格式如表1所示。

每大幀包括64個子幀,以1字節子幀計數標識,大幀計數以兩字節時統信息標識。前63個子幀用于傳輸視頻數據,考慮到采用變長視頻編碼算法后每幀壓縮圖像字節數不固定,組幀過程中需填充無效字節以保證每子幀中1 022字節的視頻數據,故我們以兩字節有效字節數來標識有效的視頻字節數。第64子幀用于傳輸遙測數據。每個子幀以3字節同步碼作為結束。

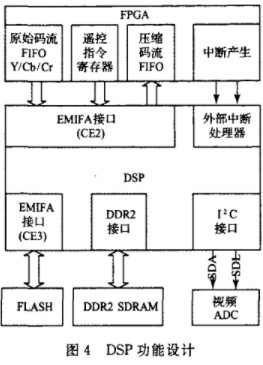

DSP選用TI公司的新一代高性能定點DSPTMS320C6455,它基于C64x+ 內核結構,片內采用L1/L2兩級緩存結構,主頻達1.2 GHz,最大峰值速度9 600 MIPS。

此外,TMS32OC6455擁有豐富的外部接口,如總線接口(FC等)和外部存儲器接口(EMIFA、DDR2)等。主要功能設計如圖4所示。

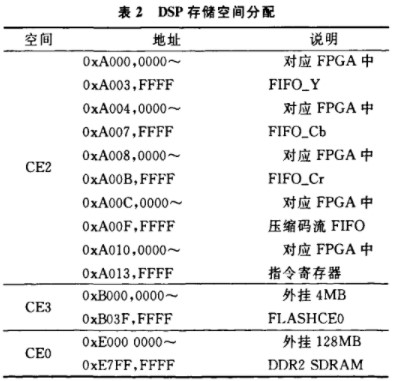

DSP部分的設計主要為存儲空間的分配,本系統中分配方式如表2所示。其中CE2空間主要用于與FPGA之間的數據交互,CE3空間主要用于代碼的非易失性存儲,CE0空間主要作為程序和數據運行的外部空問。

地面端采用FPGA+PCI接口芯片的架構實現,其中,FPGA主要完成視頻與遙測數據分離以及接口時序等功能,而PCI協議部分由接口芯片來實現,該種方式減小了FPGA的邏輯設計量。系統中FPGA選用Ahera公司Cyclone系列芯片EPIC12Q24oc8,PCI接口芯片選用PLX公司的PCI9054。PCI9054的PCI總線接口與CPCI插槽相連,本地總線接口與FPGA相連,EEPROM 用于加載配置數據。

2.2 程序算法

2.2.1 視頻編解碼算法

目前使用較多的視頻編解碼標準有國際標準化組織(ISO)與國際電工委員會(IEC)制定的MPEG一4標準,以及IS0和國際電信聯盟(ITU)制定的H.264標準。相比MPEG一4標準,H.264的復雜度高,尤其對于高分辨率的應用,硬件實現難度很大,而MPEG一4以其實現復雜度低,同時適用于高低碼率視頻的特點,在嵌入式視頻編解碼系統中得到了廣泛的應用。考慮到以上幾點,本系統中選用MPEG一4標準作為視頻編解碼算法。

系統中選用開源的MPEG一4視頻編解碼器XVIDSimple Profile作為源代碼。機載端完成視頻編碼功能。

將源代碼去除用戶交互等部分冗余代碼后,完成向TMSC320C6455平臺的移植。針對PC的XⅥD程序并不能滿足實時編碼的要求,需對程序進行優化:提高運行速度。首先對部分算法進行了優化,采用基于預測的運動估計 。其次進行代碼優化:第一步利用CCS軟件分析各部分代碼的耗時,觀察出效率較低的部分;第二步采取C語言級別的優化,如使用關鍵字、偽指令向編譯器提供優化信息,使用內聯函數,編寫軟件流水等;第三步選出第二步優化效果不明顯的代碼段,如量化/逆量化、1/2像素內插、運動補償部分,用線性匯編改寫。地面站端的上位機完成視頻解碼功能,經測試源代碼即可滿足視頻解碼的實時性。

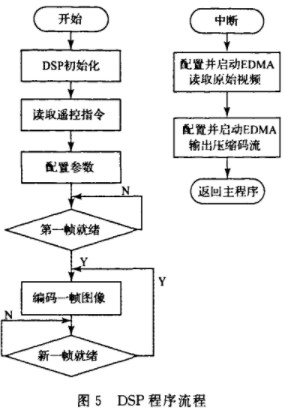

2.2.2 機載端DSP程序

DSP程序分為主程序和中斷程序兩部分,其流程圖如圖5所示。系統上電或復位后,DSP開始運行主程序,首先完成DSP內部鎖相環、EMIFA接口、DDR2接口、I C總線以及中斷的初始化,此時DSP進入正常工作狀態。然后通過EMIFA接口讀取FPGA中的遙控指令寄存器,獲取分辨率和視頻碼率信息。接下來根據獲取的信息初始化MPEG-4編碼算法的相應參數,對視頻ADC進行配置并啟動視頻采集。FPGA在視頻ADC啟動后,每采集4行原始視頻向DSP提出一次中斷。DSP響應中斷后,通過EMIFA讀取4行原始視頻,并輸出1 264字節視頻壓縮碼流。以高清(1 280×720)為例,需180次中斷完成一幀圖像的傳遞,且支持每幀圖像壓縮后最大為220 K字節。主程序判斷新的一幀到來后,開始對這一幀進行編碼。原始視頻及壓縮碼流存儲區均采用乒乓操作,與FPGA 的數據傳遞采用EDMA方式,故編碼與數據傳輸互不影響,保證了實時性。

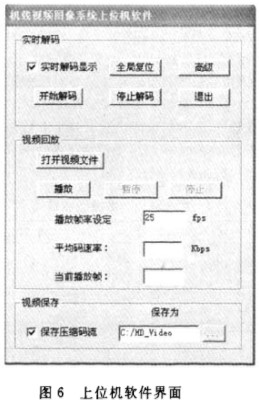

2.2.3 地面端上位機軟件

地面端上位機軟件界面采用VC MFC編寫,CPCI設備驅動程序采用Driver Studio編寫,軟件主要完成通過CPCI接口對視頻壓縮碼流的讀取、實時視頻解碼播放、視頻文件保存回放等功能。軟件操作簡便、人機交互良好,界面如圖6所示。

3 實驗結果

本文設計的機載高清視頻圖像系統設備體積小,功耗低,可靠性高,圖7(a)、(b)分別為機載設備端板卡與地面站端板卡實物圖。

本系統成功進行了有人機掛飛實驗,共進行了兩次實際飛行。每次的飛行測試時間為2 h,飛行高度為3 km,飛行半徑為5 km,飛行速度在200 km/h左右。實驗結果表明系統實現了分辨率為176×144、352×288、720×576和1 280×720,每秒25幀的MPEG-4實時視頻編解碼,同時支持視頻碼率控制,提供五個等級的視頻質量的碼流,平均碼速率在5 Mbps以下。上位機解碼后視頻圖像層次清晰,色彩飽滿,系統帶來的圖像延遲小于500 ms,滿足無人機偵察等領域的需求。不同分辨率及碼率可通過遙控[1 ” 指令動態切換,同時遙測數據正確與視頻數據組幀并分離,表明機載高清視頻圖像系統與遙控遙測系統得到了很好的融合。

4 結論

本文設計并實現了一種基于FPGA+DSP的機載高清視頻圖像系統,包括機載設備端和地面站端兩部分,具備以下特點:

1)最高支持720 P,每秒25幀的MPEG一4實時視頻編解碼,滿足當今無人機對高分辨圖像的需求;

2)視頻分辨率及碼率可通過遙控指令動態切換,視頻與遙測數據組幀傳輸,實現與傳統遙控遙測系統的融合;

3)設備體積小、功耗低、可靠性高,滿足機載苛刻的環境要求。

-

處理器

+關注

關注

68文章

19824瀏覽量

233718 -

dsp

+關注

關注

555文章

8148瀏覽量

355506 -

FPGA

+關注

關注

1643文章

21982瀏覽量

614561 -

無人機

+關注

關注

230文章

10757瀏覽量

185709

發布評論請先 登錄

【TL6748 DSP申請】基于視覺伺服控制無人機的自主飛行的研究

【TL6748 DSP申請】基于DSP和FPGA 圖像處理的系統設計

都在談論無人機:教你10種利用無人機賺錢的方法

Ameya360 無人機視覺、高級傳感與處理解決方案

無人機中的MCU是如何工作的?

遠程臨場無人機系統研發測試成功

航模/無人機遙控的解決方案

基于FPGA的無人機多路視頻監控系統設計

基于32位ARM處理器的無人機勘察系統設計

一種基于DSP+FPGA視頻圖像采集處理系統的設計與實現

利用FPGA器件和DSP處理器實現無人機高清視頻圖像系統的設計

利用FPGA器件和DSP處理器實現無人機高清視頻圖像系統的設計

評論