AD6644是Analog Devices公司推出的新型ADC器件,具有精度高、轉(zhuǎn)換速度快等特點,是當前用于中頻數(shù)字處理的優(yōu)選器件。闡述了基于AD6644的數(shù)字接收系統(tǒng)的組成,并詳盡說明了中頻數(shù)字處理模塊及接口的設(shè)計。

隨著高速A/D轉(zhuǎn)換技術(shù)和DSP技術(shù)的發(fā)展,中頻數(shù)字處理技術(shù)亦得到發(fā)展。中頻數(shù)字處理技術(shù)是提高現(xiàn)代通信接收機性能的重要技術(shù)之一。作為中頻數(shù)字處理的核心器件,早期的A/D轉(zhuǎn)換器由于速度和精度的限制,難以滿足中頻數(shù)字接收機高速數(shù)字化的要求。本文將以基于軟件無線電技術(shù)的差分跳頻電臺中頻數(shù)字接收機為例,給出一種基于新型ADC器件-AD6644的中頻數(shù)字處理模塊的設(shè)計方案。

1 系統(tǒng)總體結(jié)構(gòu)設(shè)計

本方案的中頻數(shù)字接收系統(tǒng)結(jié)構(gòu)如圖1所示。因差分跳頻系統(tǒng)是一種異步跳頻系統(tǒng),省去了同步電路,結(jié)構(gòu)得以簡化。該系統(tǒng)主要由射頻前端、中頻預(yù)處理和中頻數(shù)字處理三部分組成。系統(tǒng)主要功能為:工作在短波頻段(2~30MHz),對跳頻速率為5000跳/s、帶寬為2.56MHz的信號進行不低于12bit的采樣,以合適的數(shù)據(jù)率送入DSP,然后由DSP完成各種算法處理。

射頻信號先經(jīng)過2~30MHz的前置濾波放大電路放大。為了有效抑制組合頻率干擾和副波道干擾,本系統(tǒng)的中頻預(yù)處理部分采用高中頻方案3。信號經(jīng)濾波放大后,再經(jīng)二次下變頻得到5.12MHz的低中頻信號。該信號經(jīng)帶通濾波放大電路后,進入A/D采樣。為了保證不發(fā)生頻譜混疊,設(shè)計ADC的采樣速率為8倍于信號帶寬,即20.48MHz。關(guān)于二中頻選擇及采樣速率的確定,請參見參考文獻3,這里不再贅述。采樣后的數(shù)據(jù)率達到14bit×20.48MHz=286.72Mbit/s,經(jīng)FIFO緩沖后,送入DSP進行正交變換、FFT、頻點識別和解跳、信道譯碼等處理。下面著重就中頻數(shù)字處理模塊的硬件實現(xiàn)進行詳細說明。

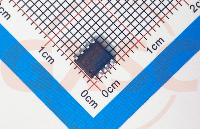

圖2 AD6644內(nèi)部結(jié)構(gòu)框圖

2 中頻數(shù)字處理模塊硬件電路設(shè)計

由圖1可以看出,中頻數(shù)字處理模塊的主要功能是對5.12MHz中頻的帶通信號進行A/D轉(zhuǎn)換,將采樣數(shù)據(jù)經(jīng)緩沖送入DSP進行處理。硬件設(shè)計主要包括ADC、FIFO、DSP三種器件的使用以及它們之間的兩個接口,下面分別介紹。

2.1 ADC器件

ADC的采樣率要求20.48MHz。對于2~30MHz的HF信號,在該采樣速率下,要求ADC器件的動態(tài)范圍達到60~90dB。美國AD公司的AD6644是理想的選擇。

AD6644是一種具有14位精度、最高采樣率為65MSPS的A/D轉(zhuǎn)換器。主要特性有:多音無雜散動態(tài)范圍(SFDR)達到100dB,典型SNR為74dB,功率耗散為1.3W,數(shù)字采樣輸出為2的補碼格式,并且有數(shù)據(jù)輸出指示信號DRY。

AD6644片上提供了采樣保持電路和基準電位,使其能成為一個完整的A/D轉(zhuǎn)換解決方案。AD6644的轉(zhuǎn)換靈敏度達到134μV,在奈奎斯特帶寬上獲得了100dB的SFDR,大大增強了當其輸入端存在雜散分量時從中檢測出有用小信號的能力,這種突破性的改進放寬了多模數(shù)字接收機(軟件無線電)的性能瓶頸。AD6644內(nèi)部采用三級子區(qū)式轉(zhuǎn)換結(jié)構(gòu),既保證了精度又降低了功耗。其內(nèi)部結(jié)構(gòu)框圖如圖2所示。

2.1.1 采樣電路

AD6644的采樣時鐘要求質(zhì)量高且相位噪聲低,如果時鐘信號抖動較大,信噪比容易惡化,很難保證14位的精度。為了優(yōu)化性能,AD6644的采樣時鐘信號采用差分形式。時鐘信號可通過一個變壓器或電容交流耦合到ENCODE和ENCODE引腳,這兩個引腳在片內(nèi)被偏置,無需外加偏置電路。為了提高時鐘信號的差分輸入質(zhì)量,本設(shè)計采用了Motorola公司的低壓差分接收芯片MC100LVEL16。整個AD6644的采樣電路如圖3所示。由于采樣電路的性能關(guān)系到最后的采樣精度,所以在布線時,應(yīng)保證從晶振到時鐘輸入腳距離盡量短,采樣電路與其它數(shù)字電路盡量隔離。在整個采樣電路下應(yīng)大面積輔銅接地,以降低可能受到的電磁干擾,同時也可降低對其它電路的干擾。

2.1.2 模擬信號輸入

作為新型的高速、大動態(tài)范圍ADC,AD6644的模擬信號輸入也要求差分形式。這樣在模擬信號階段,差分信號可以濾掉偶次諧波分量、共模的干擾信號(如由電源和地引入的噪聲),對晶振的反饋信號也有很好的濾波作用,有利于提高AD6644性能。

AD6644的模擬輸入電壓在芯片內(nèi)部被偏置到2.4V,驅(qū)動AD6644的模擬信號通過交流耦合送進輸入端。AD6644的差分輸入阻抗為1kΩ,差分輸入電壓的峰-峰值為1.1V,所以模擬輸入的功率為-2dBm,這大大簡化了模擬信號驅(qū)動放大電路。充分利用AD6644輸入阻抗高的優(yōu)點,根據(jù)變壓器阻抗變換和最佳阻抗匹配理論,在實際應(yīng)用中可采用如圖4所示的參考電路,則信號輸入端可接匹配阻抗為50Ω、滿量程驅(qū)動功率約為4.8dBm的模擬信號源。變壓器次級的串聯(lián)電阻起隔離和限流作用。

2.1.3 應(yīng)用注意事項

AD6644的供電電源必須穩(wěn)定性好,由于電源的高頻分量容易產(chǎn)生輻射,所以在靠近AD6644各電源引腳的地方,應(yīng)放置0.1μF的去耦電容。為了防止高速的數(shù)字輸出變化將開關(guān)電流耦合進模擬電源,AD6644的數(shù)字電源和模擬電源應(yīng)該分開。模擬電源應(yīng)該在5V±5%的范圍內(nèi),數(shù)字電源應(yīng)為3.3V,同時盡可能地靠近電源放置0.1~0.01μF的陶瓷電容來進行高頻濾波,并聯(lián)放置10μF的鉭電容濾除低頻噪聲。

為了很好地接收AD6644的數(shù)字輸出信號,應(yīng)盡量減小容性負載。AD6644的數(shù)字輸出有一個固定的輸出轉(zhuǎn)換擺率(1V/ns),一個典型的CMOS門加上布線約有10pF的電容,因此每bit的轉(zhuǎn)換會有10mA(10pF×1V/1ns)的動態(tài)電流出入器件,一個滿量程的轉(zhuǎn)換動態(tài)電流最大可能達140mA(14bit×10mA/bit)。在實際應(yīng)用中,每條數(shù)據(jù)輸出線上應(yīng)放置100Ω電阻,目的是要盡量限制這些電流流入接收器件。另外還應(yīng)注意,額外的容性負載會增加傳輸時延,要滿足數(shù)字輸出的時延要求,容性負載應(yīng)限制在10pF以內(nèi)。

2.2 FIFO器件

AD6644輸出的數(shù)據(jù)率高達286.72Mbit/s。如此高的數(shù)據(jù)率,如果直接用DSP的EMIF接口接收,會使DSP負荷過重。此外,如果存儲控制系統(tǒng)不能及時地接收數(shù)據(jù),上次的數(shù)據(jù)會馬上被下次的數(shù)據(jù)更新,造成數(shù)據(jù)丟失,因此必須采用高速緩存。目前常用的緩存多為FIFO、SRAM及雙口RAM等。雙口RAM和SRAM存儲量較大,但必須配以復(fù)雜的地址發(fā)生器。對于FIFO芯片,數(shù)據(jù)順序進出,且允許數(shù)據(jù)以不同的速率寫入和讀出,并且外圍電路簡單,所以本設(shè)計選用TI公司的觸發(fā)式FIFO SN74ACT7804作為數(shù)據(jù)緩存。

SN74ACT7804是一種高速的512×18bit的FIFO器件,存取速度最高可達50MHz,數(shù)據(jù)訪問時間可達15ns。數(shù)據(jù)在LDCK的上升沿寫入,在UNCK的上升沿讀出。FIFO的狀態(tài)可通過狀態(tài)位:滿(/FULL)、空(/EMPTY)、半滿(HF)以及近空/近滿(AF/AE)獲得。SN74ACT7804只能上電復(fù)位。

2.3 DSP器件

由于ADC的高數(shù)據(jù)率輸出,用DSP進行實時處理會有很大壓力。在DSP進行運算之前,必須先進行數(shù)字下變頻以降低數(shù)據(jù)率。通過對DSP算法運算量的整體分析,TI公司的TMS320C6201可滿足設(shè)計需要。作為定點DSP,TMS320C6201主頻可達200MHz,處理速度可達1600MIPS,并且它的外部存儲器接口(EMIF)支持各種同步和異步存儲器,對FIFO有很好的支持。

圖5 AD6644-FIFO-DSP接口框圖

2.4 硬件接口設(shè)計

為了保證AD6644的采樣輸出信號準確、高效地送入DSP,在ADC與DSP之間將兩片FIFO并列,構(gòu)成雙FIFO緩沖結(jié)構(gòu),并以32bit總線寬度連接到DSP的EMIF接口,具體連接如圖5所示。通過這種接口設(shè)計,在充分利用EMIF的32bit數(shù)據(jù)線寬度的同時,又巧妙地實現(xiàn)了采樣數(shù)據(jù)的奇偶分離,為DSP的數(shù)字濾波和FFT運算提供了方便。

首先介紹ADC與FIFO的接口。AD6644的14位采樣信號輸出D130與兩個FIFO的數(shù)據(jù)輸入D150相連(FIFO的D15和D14懸空),DRY信號經(jīng)二分頻后,一路連接低16位FIFO1的LDCK引腳,另一路經(jīng)“非”門反相后連接FIFO2的LDCK引腳, DRY腳輸出的是ENCODE信號的同頻反向延遲信號。從時序圖圖6中可以看出,在DRY的上升沿處,采樣信號D130準備輸出,DRY信號可準確地作為后續(xù)FIFO的觸發(fā)存儲時鐘信號。經(jīng)二分頻后的DRY信號在上升沿處交替觸發(fā)FIFO1和FIFO2的寫時鐘,將奇偶采樣信號分別存入不同的FIFO。

接著介紹FIFO與EMIF的接口。對于讀FIFO的操作,這里用到EMIF異步存儲器控制信號:輸出使能AOE和讀使能ARE、CEn是外部空間選擇信號。從圖中邏輯關(guān)系可看出,當AOE與CEn都有效時,OE有效,片選使能兩個FIFO。當CEn和ARE同時有效時,UNCK無效,待讀出的數(shù)據(jù)在此時進行初始化,隨后ARE會跳變?yōu)檎娖饯煟搐牐梗眨危茫水a(chǎn)生上升沿,FIFO中數(shù)據(jù)被讀出。圖中兩個FIFO的半滿信號HF經(jīng)過一個“與”門連接至DSP外部中斷引腳EXT_INT,在運行中不斷檢測HF管腳狀態(tài)。當兩個FIFO皆達到半滿時,“與”門輸出由低變高,上升沿觸發(fā)DSP外部中斷EXT_INT。DSP啟動DMA(直接存儲器存取)以突發(fā)的方式讀取FIFO數(shù)據(jù)。FIFO1中數(shù)據(jù)作為低16位,FIFO2中數(shù)據(jù)作為高16位,合并為32位數(shù)據(jù)讀入DSP內(nèi)部存儲空間。

有一個問題值得注意,兩個FIFO在本次讀取完成之前,有可能再次達到半滿狀態(tài),使得“與”門提前產(chǎn)生上升沿,而當本次讀取完成后,“與”門輸出已保持為高電平,不會再產(chǎn)生上升沿來觸發(fā)新的中斷,而中斷是靠上升沿觸發(fā)的,所以會導(dǎo)致傳輸停止。為了解決這個問題,將DSP計時器的TINP0管腳配置為通用I/O口,也與“與”門輸出相連,用來輔助檢測FIFO的半滿狀態(tài)。這樣當本次讀操作完成時,如果檢測TINP0口為“1”,說明FIFO又一次都達到半滿,則再次啟動DMA進行數(shù)據(jù)傳輸。因此,在程序設(shè)計進入外部EXT_INT中斷服務(wù)程序時,首先屏蔽EXT_INT,保證在本次DMA傳輸中不對中斷的任何觸發(fā)做出響應(yīng),然后啟動DMA進行本次數(shù)據(jù)傳輸,完成本次傳輸后,發(fā)送一個幀傳輸結(jié)束信號到CPU,DMA傳輸中斷。在此DMA中斷服務(wù)程序中,檢測TINP0,如果為高電平,便再次啟動DMA傳輸;否則使能中斷EXT_INT,等待“與”門的下一次上升沿觸發(fā)。這種中斷與輪詢方式的雙重機制保證了數(shù)據(jù)傳輸?shù)目煽啃浴?/span>

3 布線調(diào)試經(jīng)驗及結(jié)論

由于本模塊涉及模數(shù)混合的高速電路設(shè)計,所以電路板應(yīng)嚴格分為模擬區(qū)和數(shù)字區(qū),以ADC作為兩區(qū)的交界。內(nèi)層地也應(yīng)相應(yīng)分為數(shù)字地和模擬地,并在ADC附近通過磁珠在一點相連,以消除數(shù)字地對模擬地的干擾。ADC的時鐘與模擬信號的輸入應(yīng)盡量隔離,晶振放置應(yīng)盡量遠離供電電路。對于FIFO,為了使LDCK、UNCK、HF、RESET等信號正確且波形良好,保證數(shù)據(jù)的讀取不會產(chǎn)生丟失和誤讀,應(yīng)減少對這些信號線的干擾,可采取走線適當加粗、加信號包地的措施。在實際調(diào)試過程中發(fā)現(xiàn),由于AD6644的DRY信號輸出的驅(qū)動能力較小,使得FIFO數(shù)據(jù)有時發(fā)生漏讀現(xiàn)象。采用門電路進行整形和驅(qū)動,漏讀現(xiàn)象可得到解決。

本設(shè)計通過少量集成芯片輔以很少的分立元件,實現(xiàn)了中頻數(shù)字處理模塊的功能,并且精度和可靠性都有一定的保證。在ADC與DSP之間通過奇偶數(shù)據(jù)分離的FIFO緩沖接口,在降低數(shù)據(jù)率的同時,還能為后續(xù)多相濾波等算法提供奇偶分離。經(jīng)過調(diào)試,該接收系統(tǒng)在輸入中頻為5.12MHz、帶寬為2.56MHz的模擬信號時,其采樣精度可保證在12位以上,滿足了DSP信號處理的要求。

-

dsp

+關(guān)注

關(guān)注

556文章

8148瀏覽量

355752 -

接口

+關(guān)注

關(guān)注

33文章

8963瀏覽量

153335 -

AD6644

+關(guān)注

關(guān)注

0文章

4瀏覽量

9584

發(fā)布評論請先 登錄

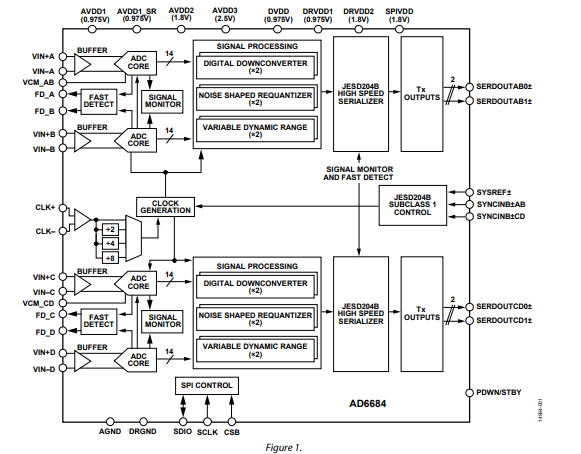

AD6684 135MHz四通道中頻接收機技術(shù)手冊

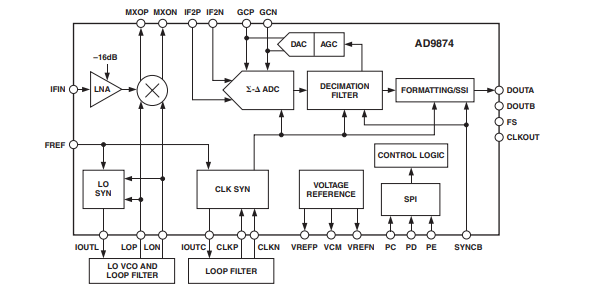

AD9874低功耗中頻數(shù)字化子系統(tǒng)技術(shù)手冊

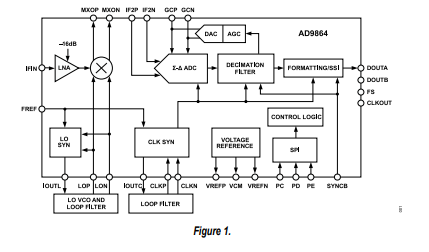

AD9864中頻數(shù)字化子系統(tǒng)技術(shù)手冊

將640x480的視頻數(shù)據(jù)輸入給TVP5158進行解碼處理,輸出的是640 x 240的視頻數(shù)據(jù),為什么?

DIT4096作為發(fā)送端,并使用雙絞線的網(wǎng)線傳輸AES數(shù)字音頻數(shù)據(jù),怎么做才能完成與DIT4096的對接呢?

數(shù)字輸出接口有哪些,數(shù)字輸出接口的作用

工頻數(shù)字電源系統(tǒng)中的實時鎖相技術(shù)

中科億海微SoM模組——中頻信號采集存儲卡

labview 數(shù)據(jù)采集 采集卡頻繁啟動造成采集緩慢

TAS3108/TAS3108IA音頻數(shù)字信號處理器數(shù)據(jù)表

TAS3308帶模擬接口的數(shù)字音頻處理器數(shù)據(jù)表

TAS3208帶模擬接口的數(shù)字音頻處理器數(shù)據(jù)表

支持多種數(shù)字音頻接口和集成多種音效算法的DSP音頻處理芯片-DU562

AD6644做中頻數(shù)字處理模塊及接口的設(shè)計

AD6644做中頻數(shù)字處理模塊及接口的設(shè)計

評論