如何區(qū)分CPLD或FPGA和哪一個(gè)更適合自己?這是一個(gè)老生常談的問(wèn)題,尤其是學(xué)生和初學(xué)者。如果您也在這個(gè)問(wèn)題上很迷茫,那么就請(qǐng)聽小編為您區(qū)分FPGA與CPLD。

CPLD

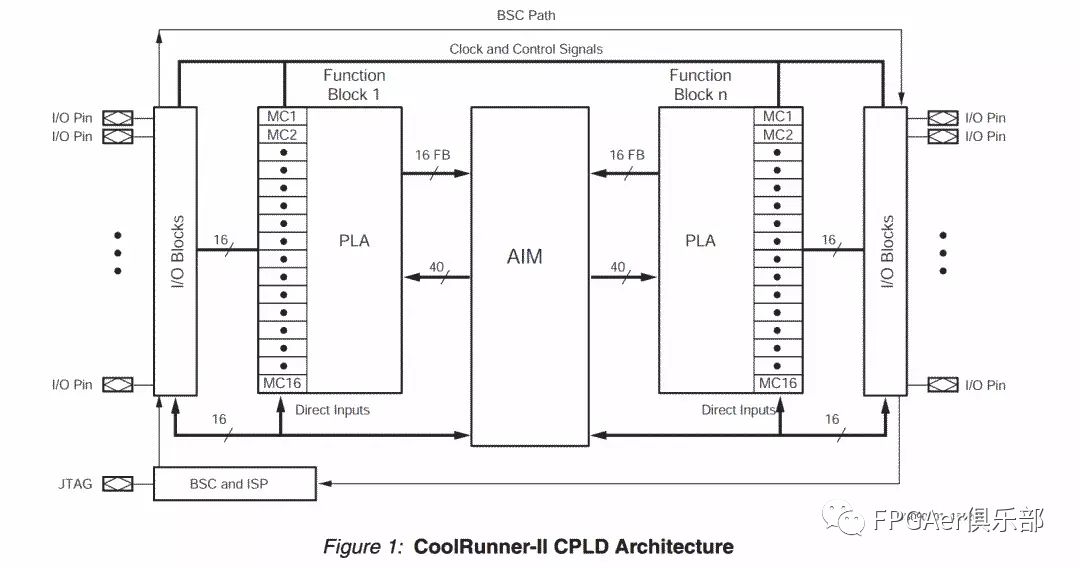

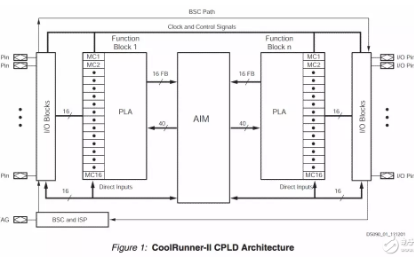

我們先來(lái)看看CPLD,在此以Xilinx CoolRunner-II為例。下圖是Xilinx CoolRunner-II的架構(gòu)圖。

現(xiàn)在小編為您解釋一下上圖的內(nèi)容。

1.該CPLD具有從“功能塊1”到“功能塊n”開始的功能塊很少(在CoolRunner-II CPLD的情況下,此編號(hào)范圍為2到32)

2.每個(gè)功能塊的16行輸出進(jìn)入AIM(高級(jí)互連矩陣),而40行信號(hào)從AIM輸入功能塊。

3.每個(gè)功能塊都有16個(gè)MacroCell(MC1到MC16)。

4.每個(gè)MacroCell都可以訪問(wèn)來(lái)自I / O塊的16個(gè)信號(hào)

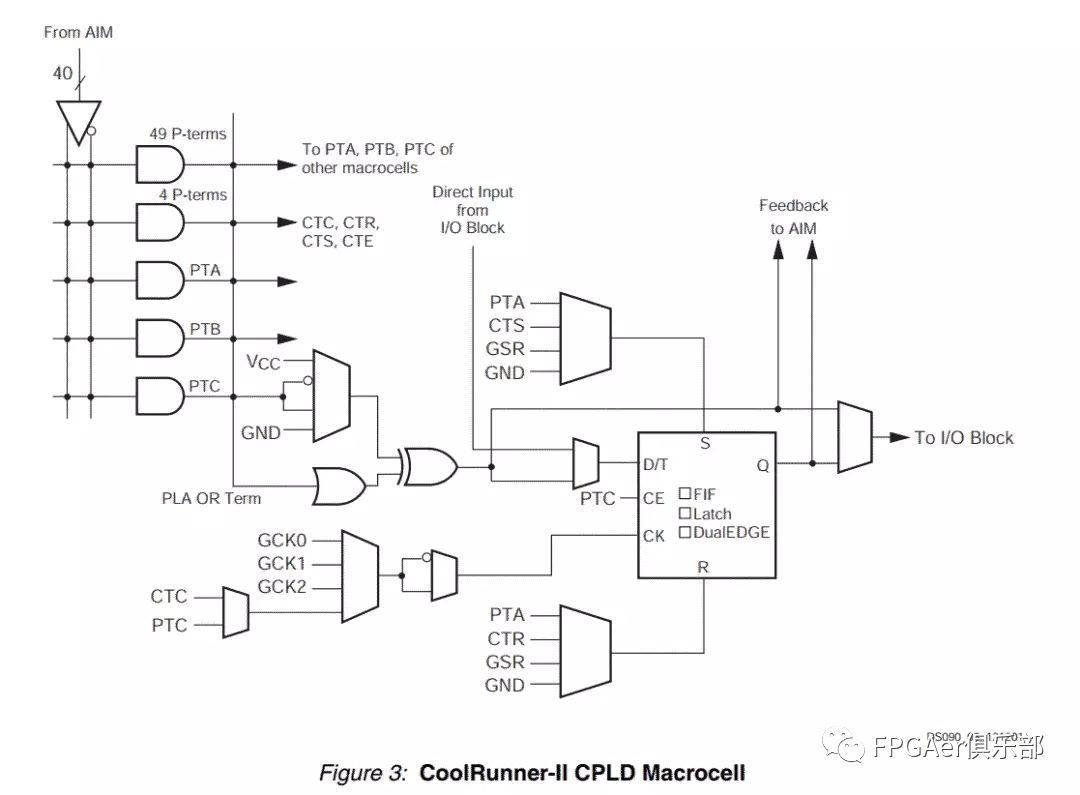

5.MacroCell的結(jié)構(gòu)如下所示。每個(gè)宏單元包含1個(gè)觸發(fā)器和PLA陣列的產(chǎn)品和,用戶可以利用它來(lái)創(chuàng)建組合或順序邏輯。因此,CoolRunner-II CLPD(XC2C512)中可用的最大觸發(fā)器數(shù)量為512!(記住這個(gè)數(shù)字,我們將它與FPGA中的觸發(fā)器數(shù)量進(jìn)行比較)

6.可以對(duì)AIM進(jìn)行編程,以便根據(jù)需要互連信號(hào)。但正如我們?cè)谏厦娴牡诙€(gè)要點(diǎn)中看到的那樣,每個(gè)功能塊的信號(hào)數(shù)量都是有限的。

與PLA(programmable Logic Array,可編程邏輯陣列)相同,CPLD在每個(gè)宏單元中的邏輯功能通過(guò)JTAG上的系統(tǒng)編程(ISP)接口進(jìn)行電氣編程。編程后,這些基于閃存的連接多年來(lái)一直保持不變。這為CPLD提供了“即時(shí)啟動(dòng)”工作的獨(dú)特優(yōu)勢(shì)。也就是說(shuō),CPLD一上電就開始工作,因?yàn)槌绦蛲ㄟ^(guò)ISP閃存燒入。但FPGA的情況不盡相同,我們后文再討論。

總結(jié)一下,我們可以說(shuō),在CPLD中,有幾百個(gè)功能塊(或邏輯塊),通常少于1000個(gè),可由單個(gè)大型邏輯單元互連訪問(wèn)。

FPGA

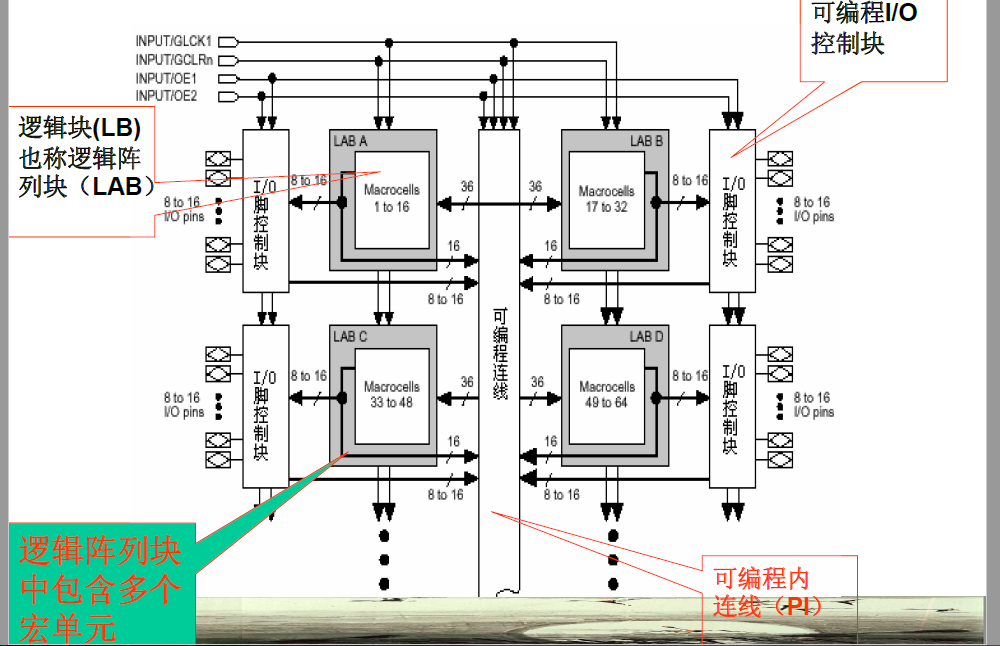

雖然制造商沒有公開發(fā)布確切的FPGA架構(gòu),但我們?nèi)匀豢梢垣@得更高級(jí)別的架構(gòu),這將有助于理解FPGA及其工作原理。讓我們先來(lái)看一下Xilinx的的高級(jí)示例。

在FPGA中,有許多可配置邏輯塊(Configurable Logic Block,CLB )嵌入在可編程互連的“海洋”中。與CPLD的宏單元相比,這些CLB非常復(fù)雜,并且可以實(shí)現(xiàn)更復(fù)雜的邏輯功能。它們主要由查找表(LUT),多路復(fù)用器和觸發(fā)器組成。FPGA可以在單個(gè)器件中包含數(shù)百萬(wàn)個(gè)CLB!數(shù)以百萬(wàn)計(jì)的觸發(fā)器(Xilinx VU13P中約為345.6萬(wàn)個(gè)觸發(fā)器),與Xilinx同廠性能最好的CPLD中的512個(gè)觸發(fā)器相比顯得非常龐大。邏輯門數(shù)量的巨大差異也決定了FPGA的用途。

如上圖所示,F(xiàn)PGA還具有用于各種功能的專用硬件,如RAM,高速串行收發(fā)器,數(shù)字信號(hào)處理(DSP)模塊,外部存儲(chǔ)器控制器,PLL和MMCM,PCIe等!就多種選擇和靈活性而言,CPLD與FPGA無(wú)法匹敵。

如前文所述,F(xiàn)PGA基于LUT。當(dāng)FPGA上電時(shí),器件始終為空白。存在稱為配置電路的特殊電路,其從外部ROM讀取配置數(shù)據(jù),并根據(jù)外部ROM中存在的用戶設(shè)計(jì)來(lái)配置LUT。FPGA配置需要一些時(shí)間,F(xiàn)PGA將在配置加載完成后才開始工作。當(dāng)然也有例外。一些制造商已經(jīng)提出內(nèi)置配置閃存的FPGA。即使在這種情況下,配置數(shù)據(jù)也沒有嵌入到結(jié)構(gòu)中,并且仍然適用一些對(duì)時(shí)間的設(shè)置與配置。

CPLD與FPGA比較匯總

小編總結(jié)了一個(gè)表格,可以概括一下兩者的異同。

FPGA即使在運(yùn)行時(shí)也可以改變電路結(jié)構(gòu)!(因?yàn)樗皇歉戮哂胁煌瑑?nèi)容的LUT的問(wèn)題)這稱為部分重配置,當(dāng)FPGA需要繼續(xù)運(yùn)行設(shè)計(jì)并同時(shí)根據(jù)需要使用不同的設(shè)計(jì)更新它時(shí)非常有用。此功能廣泛用于加速計(jì)算。

CPLD和FPGA的用途區(qū)分

如果設(shè)計(jì)需要簡(jiǎn)單的組合邏輯電路,無(wú)需進(jìn)行太多更改,或者需要瞬時(shí)接通電路,那么CPLD是不錯(cuò)的選擇。否則,對(duì)于大多數(shù)其他應(yīng)用,F(xiàn)PGA通常是首選。有時(shí)您可以在設(shè)計(jì)案例中看到CPLD + FPGA的組合設(shè)計(jì)。在這些案例中,CPLD通常用于實(shí)現(xiàn)前面提到的簡(jiǎn)單組合邏輯功能,并負(fù)責(zé)“引導(dǎo)”FPGA以及控制整個(gè)電路板的復(fù)位和引導(dǎo)順序。因此,根據(jù)應(yīng)用程序,您可能需要在設(shè)計(jì)中使用它們。

隨著AI技術(shù)的發(fā)展,F(xiàn)PGA又一次站在了風(fēng)口上——它以內(nèi)置龐大的邏輯門電路,合理的功耗,在GPU、ASIC之后,為AI從業(yè)者提供了一種更為靈活的算法實(shí)現(xiàn)方案。在此業(yè)態(tài)下,F(xiàn)PGA的發(fā)展也會(huì)給它的傳統(tǒng)應(yīng)用領(lǐng)域——以高速通信為主的通信領(lǐng)域和以驅(qū)動(dòng)組合邏輯芯片為主的LED顯示行業(yè)注入新的發(fā)展契機(jī)。

-

FPGA

+關(guān)注

關(guān)注

1640文章

21887瀏覽量

610890 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

170489

原文標(biāo)題:告別選擇困難癥——區(qū)分FPGA與CPLD

文章出處:【微信號(hào):FPGAer_Club,微信公眾號(hào):FPGAer俱樂部】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA與CPLD怎么區(qū)分

FPGA與CPLD該怎么區(qū)分?

如何區(qū)分CPLD與FPGA,怎么選擇?

Altera FPGA/CPLD設(shè)計(jì)(高級(jí)篇)

altera fpga/cpld設(shè)計(jì)

關(guān)于CPLD和FPGA的區(qū)別

CPLD和FPGA兩者的區(qū)別

如何區(qū)分FPGA與CPLD?本文告訴你答案!

FPGA教程之CPLD與FPGA的基礎(chǔ)知識(shí)說(shuō)明

CPLD和FPGA這兩者到底有什么區(qū)別呢

Altera FPGA CPLD學(xué)習(xí)筆記

FPGA CPLD中的Verilog設(shè)計(jì)小技巧

常用FPGA/CPLD設(shè)計(jì)思想與技巧

CPLD和FPGA的區(qū)別是什么

如何區(qū)分FPGA和CPLD?

如何區(qū)分FPGA和CPLD?

評(píng)論