? ?0. 概述

乒乓操作

串并轉換

流水線操作

數據接口同步化

都是FPGA/CPLD邏輯設計的內在規律的體現,合理地采用這些設計思想能在FPGA/CPLD設計工作種取得事半功倍的效果。

FPGA/CPLD的設計思想與技巧是一個非常大的話題,由于篇幅所限,本文僅介紹這4個常用的設計思想與技巧,希望本文能引起工程師們的注意,如果能有意識地利用這些原則指導日后的設計工作,將取得事半功倍的效果!

下載鏈接: 《FPGA五問五答系列合集》 GPT-5后NLP大模型逐步走向收斂,ASIC將大有可為 《70+篇半導體行業“研究框架”合集》 《人工智能AI大模型技術合集》 信創從“芯”開始 云計算通用可編程DPU發展白皮書(2023年) 《42份智能網卡和DPU合集》 227份重磅ChatGPT專業報告 GPT4專題:構建模型理解能力,商業落地未來可期 華為昇騰服務器研究框架(2023) 《華為鯤鵬產業鏈深度研究合集》 1、華為鯤鵬生態研究框架 2、產業鏈深度研究:鯤鵬生態助力華為涅槃

1. 乒乓操作

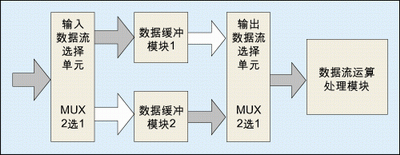

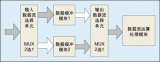

乒乓操作是一個常常應用于數據流控制的處理技巧,典型的乒乓操作方法如下圖所示:

乒乓操作的處理流程為:

輸入數據流通過“輸入數據選擇單元”將數據流等時分配到兩個數據緩沖區,數據緩沖模塊可以為任何存儲模塊,比較常用的存儲單元: 雙口RAM(DPRAM)、單口RAM(SPRAM)、FIFO 等。

在第1個緩沖周期,將輸入的數據流緩存到數據緩沖模塊1;

在第2個緩沖周期,通過輸入數據選擇單元的切換,將輸入的數據流緩存到數據緩沖模塊2,同時將數據緩沖模塊1緩存的第1個周期數據通過輸入數據選擇單元的選擇,送到數據流運算處理模塊進行運算處理;

在第3個緩沖周期,通過輸入數據選擇單元的再次切換,將輸入的數據流緩存到數據緩沖模塊1,同時將數據緩沖模塊2緩存的第2個周期的數據通過輸入數據選擇單元切換,送到數據流運算處理模塊進行運算處理。

如此循環。

乒乓操作的最大特點是通過“輸入數據選擇單元”和“輸出數據選擇單元”按節拍、相互配合的切換,將經過緩沖的數據流沒有停頓地送到“數據流運算處理模塊” 進行運算與處理。

把乒乓操作模塊當做一個整體,站在這個模塊的兩端看數據,輸入數據流和輸出數據流都是連續不斷的,沒有任何停頓,因此非常適合對數據流進行流水線式處理。所以乒乓操作常常應用于流水線式算法,完成數據的無縫緩沖與處理。

乒乓操作的第二個優點是可以節約緩沖區空間。

比如在WCDMA基帶應用中,1個幀是由15個時隙組成的,有時需要將 1整幀的數據延時一個時隙后處理,比較直接的辦法是將這幀數據緩存起來,然后延時1個時隙進行處理。這時緩沖區的長度是1整幀數據長,假設數據速率是3.84Mbps,1幀長10ms,則此時需要緩沖區長度是 38400 位。

如果采用乒乓操作,只需定義兩個能緩沖 1個時隙數據的RAM(單口RAM即可)。當向一塊 RAM 寫數據的時候,從另一塊 RAM 讀數據,然后送到處理單元處理,此時每塊 RAM 的容量僅需 2560 位即可,

2 塊 RAM 加起來也只有 5120 位的容量。

另外,巧妙運用乒乓操作還可以達到用低速模塊處理高速數據流的效果。

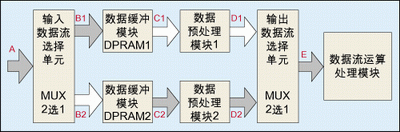

如上圖所示,數據緩沖模塊采用了雙口RAM,并在DPRAM后引入了一級數據預處理模塊,這個數據預處理可以根據需要的各種數據運算,比如在WCDMA設計中,對輸入數據流的解擴、解擾、去旋轉等。假設端口A的輸入數據流的速率為100Mbps,乒乓操作的緩沖周期是10ms。以下分析各個節點端口的數據速率。

A端口處輸入數據流速率為100Mbps,在第1個緩沖周期10ms內,通過“輸入數據選擇單元”,從 B1 到達 DPRAM1。B1 的數據速率也是 100Mbps,DPRAM1 要在 10ms 內寫入 1Mb 數據。

同理,在第 2 個 10ms,數據流被切換到 DPRAM2,端口 B2 的數據速率也是 100Mbps,DPRAM2在第 2 個 10ms 被寫入 1Mb 數據。

在第3 個 10ms,數據流又切換到 DPRAM1,DPRAM1 被寫入1Mb 數據。

仔細分析就會發現到第3個緩沖周期時,留給DPRAM1讀取數據并送到“數據預處理模塊1”的時間一共是20ms。

有的工程師困惑于 DPRAM1 的讀數時間為什么是 20ms,這個時間是這樣得來的:

首先,在在第 2 個緩沖周期向 DPRAM2 寫數據的 10ms 內,DPRAM1 可以進行讀操作;

另外,在第 1 個緩沖周期的第 5ms 起(絕對時間為 5ms 時刻),DPRAM1 就可以一邊向 500K 以后的地址寫數據,一邊從地址 0 讀數,到達 10ms 時,DPRAM1 剛好寫完了 1Mb 數據,并且讀了 500K 數據,這個緩沖時間內 DPRAM1 讀了 5ms;

在第 3 個緩沖周期的第 5ms 起(絕對時間為 35ms 時刻),同理可以一邊向 500K 以后的地址寫數據一邊從地址0 讀數,又讀取了5 個ms,所以截止 DPRAM1 第一個周期存入的數據被完全覆蓋以前,DPRAM1 最多可以讀取 20ms時間,而所需讀取的數據為 1Mb,所以端口 C1 的數據速率為:1Mb/20ms=50Mbps。因此,“數據預處理模塊 1”的最低數據吞吐能力也僅僅要求為 50Mbps。

同理,“數據預處理模塊 2”的最低數據吞吐能力也僅僅要求為 50Mbps。

換言之,通過乒乓操作,“數據預處理模塊”的時序壓力減輕了,所要求的數據處理速率僅僅為輸入數據速率的 1/2。

通過乒乓操作實現低速模塊處理高速數據的實質是:通過 DPRAM 這種緩存單元實現了數據流的串并轉換,并行用“數據預處理模塊 1”和“數據預處理模塊 2”處理分流的數據,是面積與速度互換原則的體現!

2. 串并轉換設計技巧

串并轉換是FPGA設計的一個重要技巧,它是數據流處理的常用手段,也是面積與速度互換思想的直接體現。

串并轉換的實現方法多種多樣,根據數據的排序和數量的要求,可以選用 寄存器、RAM 等實現。

前面在乒乓操作的圖例中,就是通過 DPRAM 實現了數據流的串并轉換,而且由于使用了DPRAM,數據的緩沖區可以開得很大,對于數量比較小的設計可以采用寄存器完成串并轉換。

如無特殊需求,應該用同步時序設計完成串并之間的轉換。

比如數據從串行到并行,數據排列順序是高位在前,可以用下面的編碼實現:

prl_temp<={prl_temp,srl_in};

其中,prl_temp是并行輸出緩存寄存器,srl_in是串行數據輸入。

對于排列順序有規定的串并轉換,可以用case語句判斷實現。

對于復雜的串并轉換,還可以用狀態機實現。串并轉換的方法比較簡單,在此不必贅述。

3. 流水線操作設計思想

首先需要聲明的是,這里所講述的流水線是指一種處理流程和順序操作的設計思想,并非FPGA、ASIC設計中優化時序所用的Pipelining。

流水線處理是高速設計中的一個常用設計手段。如果某個設計的處理流程分為若干步驟,而且整個數據處理是“單流向”的,即沒有反饋或者迭代運算,前一個步驟的輸出是下一個步驟的輸入,則可以考慮采用流水線設計方法來提高系統的工作頻率。

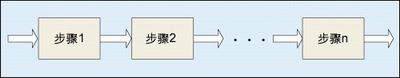

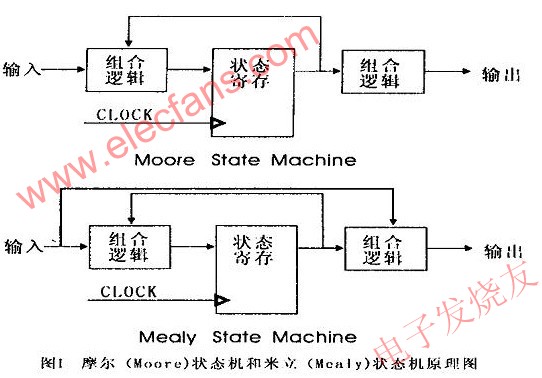

流水線設計的結構示意圖如上圖所示。

其基本結構為:將適當劃分的 n 個操作步驟單流向串聯起來。

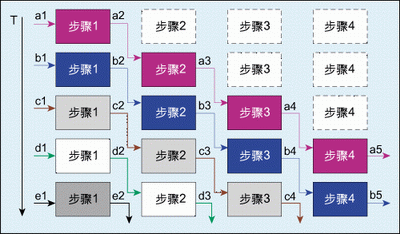

流水線操作的最大特點和要求是,數據流在各個步驟的處理從時間上看是連續的,如果將每個操作步驟簡化假設為通過一個D觸發器(就是用寄存器打一個節拍),那么流水線操作就類似一個移位寄存器組,數據流依次流經D觸發器,完成每個步驟的操作。流水線設計時序如下圖所示。

流水線設計的一個關鍵在于整個設計時序的合理安排,要求每個操作步驟的劃分合理。

如果前級操作時間恰好等于后級的操作時間,設計最為簡單,前級的輸出直接匯入后級的輸入即可;

如果前級操作時間大于后級的操作時間,則需要對前級的輸出數據適當緩存才能匯入到后級輸入端;

如果前級操作時間恰好小于后級的操作時間,則必須通過復制邏輯,將數據流分流,或者在前級對數據采用存儲、后處理方式,否則會造成后級數據溢出。

在WCDMA設計中經常使用到流水線處理的方法,如 RAKE 接收機、搜索器、前導捕獲等。

流水線處理方式之所以頻率較高,是因為復制了處理模塊,它是面積換取速度思想的又一種具體體現。

4. 數據接口的同步方法

數據接口的同步是 FPGA/CPLD 設計的一個常見問題,也是一個重點和難點,很多設計不穩定都是源于數據接口的同步有問題。

在電路圖設計階段,一些工程師手工加入BUFT或者非門調整數據延遲,從而保證本級模塊的時鐘對上級模塊數據的建立、保持時間要求。還有一些工程師為了有穩定的采樣,生成了很多相差90度的時鐘信號,時而用正沿打一下數據,時而用負沿打一下數據,用以調整數據的采樣位置。

這兩種做法都十分不可取,因為一旦芯片更新換代或者移植到其它芯片組的芯片上,采樣實現必須重新設計。而且,這兩種做法造成電路實現的余量不夠,一旦外界條件變換(比如溫度升高),采樣時序就有可能完全紊亂,造成電路癱瘓。

下面簡單介紹幾種不同情況下數據接口的同步方法:

輸入、輸出的延時(芯片間、PCB布線、一些驅動接口元件的延時等)不可測,或者有可能變動的條件下,如何完成數據同步?

對于數據的延遲不可測或變動,就需要建立同步機制,可以用一個同步使能或同步指示信號。

另外,使數據通過RAM或者FIFO的存取,也可以達到數據同步目的。

把數據存放在RAM或FIFO的方法如下:將上級芯片提供的數據隨路時鐘作為寫信號,將數據寫入RAM或者 FIFO,然后使用本級的采樣時鐘(一般是數據處理的主時鐘)將數據讀出來即可。這種做法的關鍵是數據寫入RAM或者FIFO要可靠,如果使用同步 RAM 或者 FIFO,就要求應該有一個與數據相對延遲關系固定的隨路指示信號,這個信號可以是數據的有效指示,也可以是上級模塊將數據打出來的時鐘。對于慢速數據,也可以采樣 異步RAM 或者 FIFO,但是不推薦這種做法。

數據是有固定格式安排的,很多重要信息在數據的起始位置,這種情況在通信系統中非常普遍。通訊系統中,很多數據是按照“幀”組織的。而由于整個系統對時鐘要求很高,常常專門設計一塊時鐘板完成高精度時鐘的產生與驅動。而數據又是有起始位置的,如何完成數據的同步,并發現數據的“頭”呢?

數據的同步方法完全可以采用上面的方法,采用同步指示信號,或者使用RAM、FIFO 緩存一下。

找到數據頭的方法有兩種,第一種很簡單,隨路傳輸一個數據起始位置的指示信號即可,對于有些系統,特別是異步系統,則常常在數據中插入一段同步碼(比如訓練序列),接收端通過狀態機檢測到同步碼后就能發現數據的“頭”了,這種做法叫做“盲檢測”。上級數據和本級時鐘是異步的,也就是說上級芯片或模塊和本級芯片或模塊的時鐘是異步時鐘域的。

前面在輸入數據同步化中已經簡單介紹了一個原則:如果輸入數據的節拍和本級芯片的處理時鐘同頻,可以直接用本級芯片的主時鐘對輸入數據寄存器采樣,完成輸入數據的同步化;如果輸入數據和本級芯片的處理時鐘是異步的,特別是頻率不匹配的時候,則只有用處理時鐘對輸入數據做兩次寄存器采樣,才能完成輸入數據的同步化。

需要說明的是,用寄存器對異步時鐘域的數據進行兩次采樣,其作用是有效?防止亞穩態(數據狀態不穩定)?的傳播,使后級電路處理的數據都是有效電平。但是這種做法并不能保證兩級寄存器采樣后的數據是正確的電平,這種方式處理一般都會產生一定數量的錯誤電平數據。所以僅僅適用于對少量錯誤不敏感的功能單元。為了避免異步時鐘域產生錯誤的采樣電平,一般使用 RAM、FIFO 緩存的方法完成異步時鐘域的數據轉換。

最常用的緩存單元是DPRAM,在輸入端口使用上級時鐘寫數據,在輸出端口使用本級時鐘讀數據,這樣就非常方便的完成了異步時鐘域之間的數據交換。

設計數據接口同步是否需要添加約束?

建議最好添加適當的約束,特別是對于高速設計,一定要對周期、建立、保持時間等添加相應的約束。

這里附加約束的作用有兩點:

a. 提高設計的工作頻率,滿足接口數據同步要求。通過附加周期、建立時間、保持時間等約束可以控制邏輯的綜合、映射、布局和布線,以減小邏輯和布線延時,從而提高工作頻率,滿足接口數據同步要求。

b. 獲得正確的時序分析報告。幾乎所有的FPGA設計平臺都包含靜態時序分析工具,利用這類工具可以獲得映射或布局布線后的時序分析報告,從而對設計的性能做出評估。靜態時序分析工具以約束作為判斷時序是否滿足設計要求的標準,因此要求設計者正確輸入約束,以便靜態時序分析工具輸出正確的時序分析報告。

Xilinx和數據接口相關的常用約束有Period、OFFSET_IN_BEFORE、OFFSET_IN_AFTER、OFFSET_OUT_BEFORE 和 OFFSET_OUT_AFTER;

Altera與數據接口相關的常用約束有Period、tsu、tH、tco等。

電子發燒友App

電子發燒友App

評論