Abstract

在Verilog中,always block可以用來代表Flip-Flop, Combination Logic與Latch,本文比較在不寫else下,always block所代表的電路。

Introduction

在C語言裡,省略else只是代表不處理而;已但在Verilog裡,省略else所代表的是不同的電路。

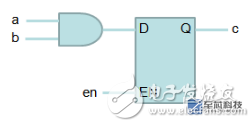

always@(a or b or en)

if (en)

c = a & b;

在combination logic中省略else,由於必須在~en保留原本的值,所以會產(chǎn)生latch。

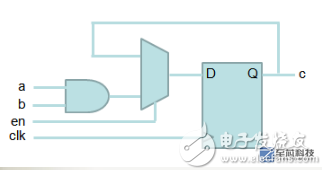

always@(posedge clk)

if (en)

c <= a & b;

雖然也必須在~en保留原本的值,但由於flip-flop就有記憶的功能,所以不會產(chǎn)生latch。if將產(chǎn)生mux,並將flip-flop的值拉回給mux。

Conclusion

在Verilog中,雖然只是小小的差異,但結(jié)果卻有天大的差異。

全文完。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615359

發(fā)布評論請先 登錄

半導體器件

200w開關(guān)電源__功率級電路設計總結(jié)

淺談Verilog和VHDL的區(qū)別

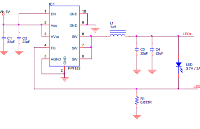

手電筒控制IC,LED手電筒驅(qū)動芯片F(xiàn)P7153同步降壓LED驅(qū)動IC應用說明與電路設計原理

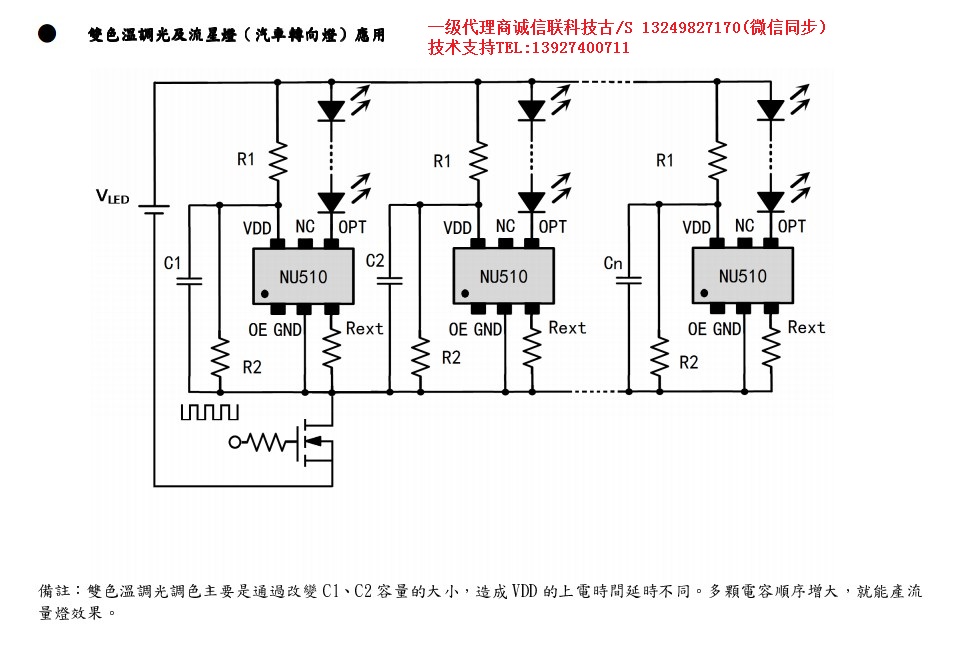

汽車儀表盤車燈照明驅(qū)動芯片NU510

Verilog 與 ASIC 設計的關(guān)系 Verilog 代碼優(yōu)化技巧

Verilog 測試平臺設計方法 Verilog FPGA開發(fā)指南

Verilog與VHDL的比較 Verilog HDL編程技巧

Verilog硬件描述語言參考手冊

如何利用Verilog-A開發(fā)器件模型

always block內(nèi)省略else所代表的電路 (SOC) (Verilog)

always block內(nèi)省略else所代表的電路 (SOC) (Verilog)

評論