Xilinx(賽靈思)是全球領(lǐng)先的可編程邏輯完整解決方案的供應(yīng)商。Xilinx研發(fā)、制造并銷(xiāo)售范圍廣泛的高級(jí)集成電路、軟件設(shè)計(jì)工具以及作為預(yù)定義系統(tǒng)級(jí)功能的IP(Intellectual Property)核

-

賽靈思

+關(guān)注

關(guān)注

33文章

1797瀏覽量

132168 -

IP

+關(guān)注

關(guān)注

5文章

1791瀏覽量

151648 -

可編程邏輯

+關(guān)注

關(guān)注

7文章

524瀏覽量

44629

發(fā)布評(píng)論請(qǐng)先 登錄

基于A(yíng)D9613與Xilinx MPSoC平臺(tái)的高速AD/DA案例分享

XILINX XCZU67DR FPGA完整原理圖

Xilinx Shift RAM IP概述和主要功能

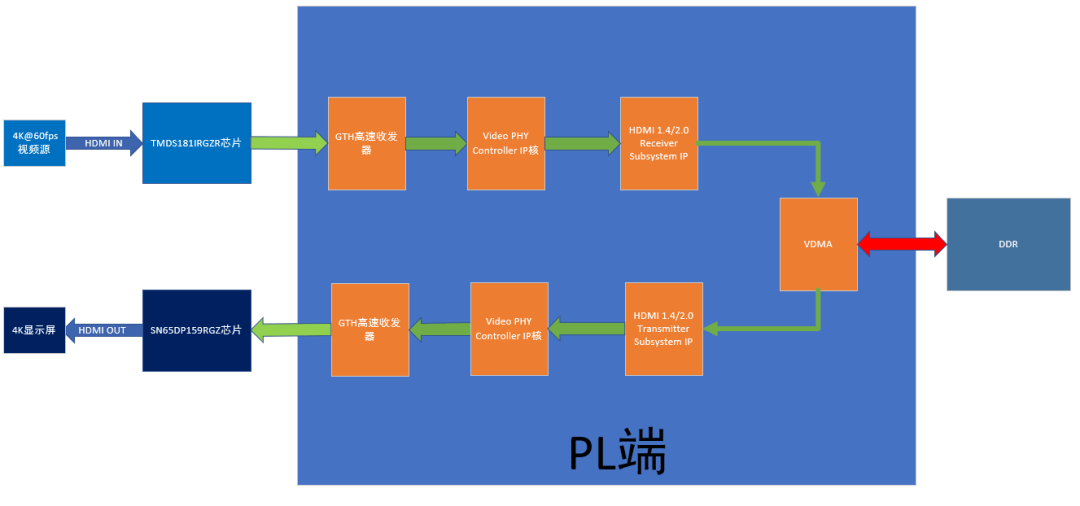

解鎖4K,Xilinx MPSoC ARM + FPGA高清視頻采集與顯示方案!

ADS54J64EVM開(kāi)發(fā)板可以配套使用哪些Xilinx FPGA開(kāi)發(fā)板呢?

SRIO介紹及xilinx的vivado 2017.4中生成srio例程代碼解釋

基于Xilinx ZYNQ7000 FPGA嵌入式開(kāi)發(fā)實(shí)戰(zhàn)指南

【米爾-Xilinx XC7A100T FPGA開(kāi)發(fā)板試用】測(cè)試一

采用Xilinx FPGA的AFE79xx SPI啟動(dòng)指南

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

如何申請(qǐng)xilinx IP核的license

[XILINX] 正點(diǎn)原子ZYNQ7035/7045/7100開(kāi)發(fā)板發(fā)布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

如何在ModelSim中添加Xilinx仿真庫(kù)

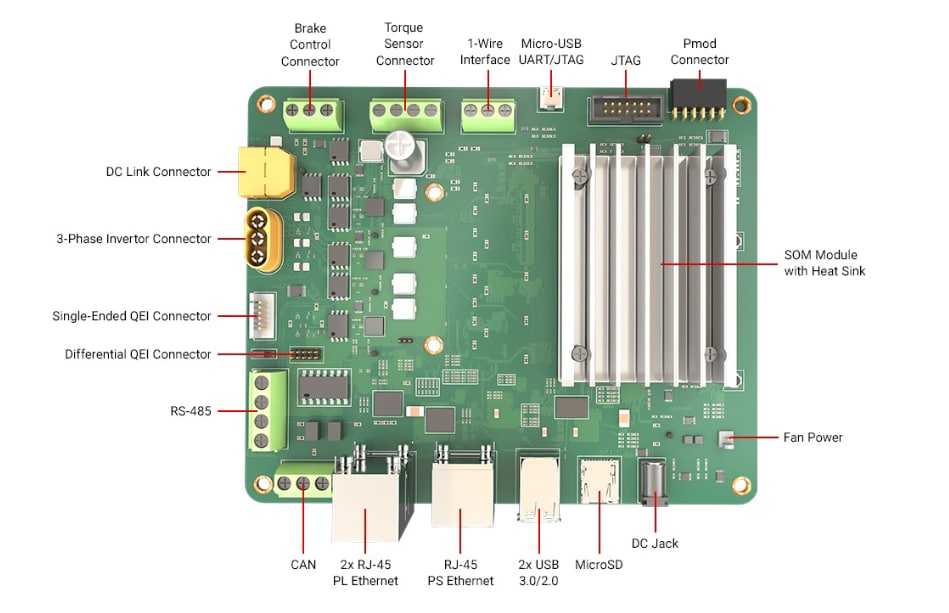

快速開(kāi)箱即用體驗(yàn) AMD / Xilinx Kria? KD240驅(qū)動(dòng)器入門(mén)套件

對(duì)Xilinx的了解介紹

對(duì)Xilinx的了解介紹

評(píng)論