分頻器的設計-奇偶分頻

2的n次方分頻實現

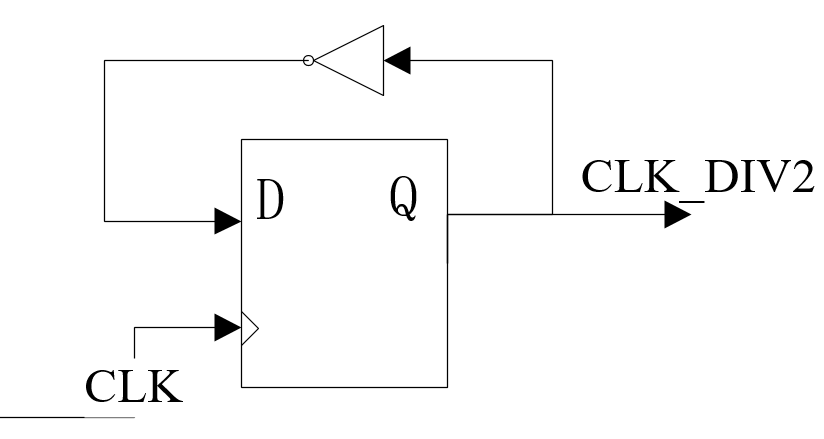

如下電路可以實現對CLK的2分頻。原理很簡單,上電復位先給寄存器一個初始值,然后只有在CLK上升沿CLK_DIV2才會翻轉一次。故CLK兩個上升沿之后,CLK_DIV2才完成兩次翻轉。

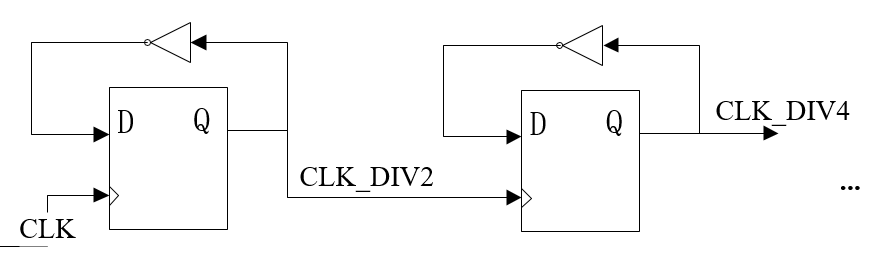

要實現2的n次方分頻可以通過復用n次這個電路。如下所示。

偶數倍分頻

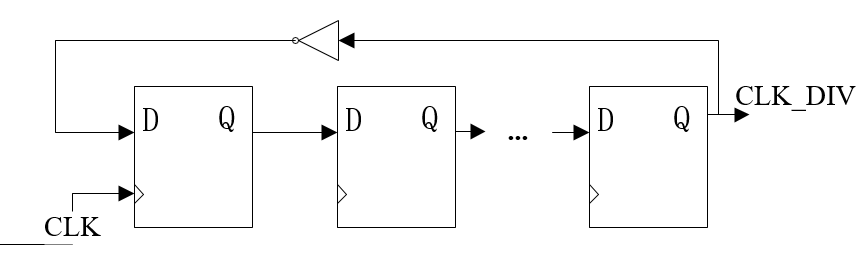

方式一:如下所示。通過移位寄存器實現分頻。例如要實現2n倍分頻,則需要用n個寄存器。

優點:不需要其它任何控制邏輯,只需要寄存器加一個反相器。

缺點:當分頻倍數很大時,需要的寄存器也是倍增。當然你也可以采用復用的方式去減少所需寄存器數目,例如,36分頻,可以做兩個6分頻器相連,則所需寄存器為6個,需要的寄存器數大大減少。

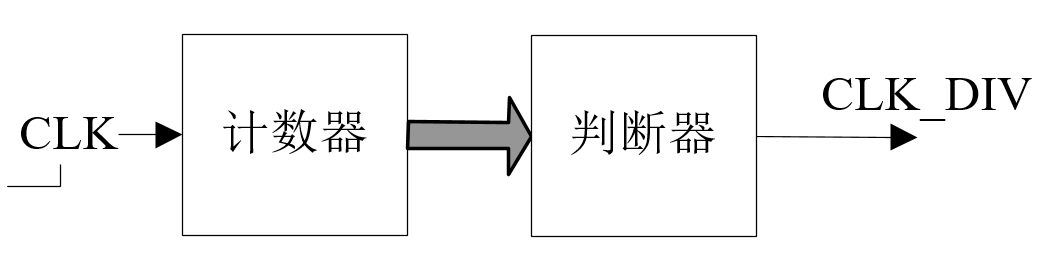

方式二:如下圖所示,通過計數器來實現分頻。比如,做一個2n分頻器,則計數器計數從0到n-1,CLK_DIV就翻轉一次。

代碼如下(分頻數為DIV_NUM=20):

仿真波形:

奇數倍分頻

如上方式只能實現偶數倍分頻,是因為寄存器都是源時鐘CLK上升沿觸發的,因此DIV_CLK只能在上升沿去發生跳轉,這導致DIV_CLK必定只能是CLK的偶數倍分頻關系(CLK跳轉兩次,DIV_CLK才可能跳轉一次)。

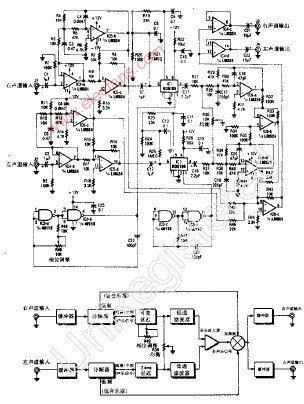

奇數倍分頻的一種實現方式如下。一路計數器用CLK的非CLK_N控制,一路用CLK控制。最后將兩路的輸出分頻波形相亦或,得到最后的分頻輸出。如果難以理解可以對著最后的波形去看。

Verilog實現如下(分頻數為DIV_NUM=9):

仿真波形如下:

思考

大家以上面的為基礎,思考一下占空比可調的分頻時鐘的實現。

-

寄存器

+關注

關注

31文章

5439瀏覽量

124925 -

分頻器

+關注

關注

43文章

493瀏覽量

51272

原文標題:分頻器的設計-奇偶分頻

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

分頻器設計與制作 (電子書)

分頻器的定義及電子、功率分頻器的比較

分頻器有哪些_分頻器分類

音箱分頻器怎么接線_音箱分頻器接線圖解

FPGA學習-分頻器設計

分頻器的設計-奇偶分頻

分頻器的設計-奇偶分頻

評論