SPI 協議簡介

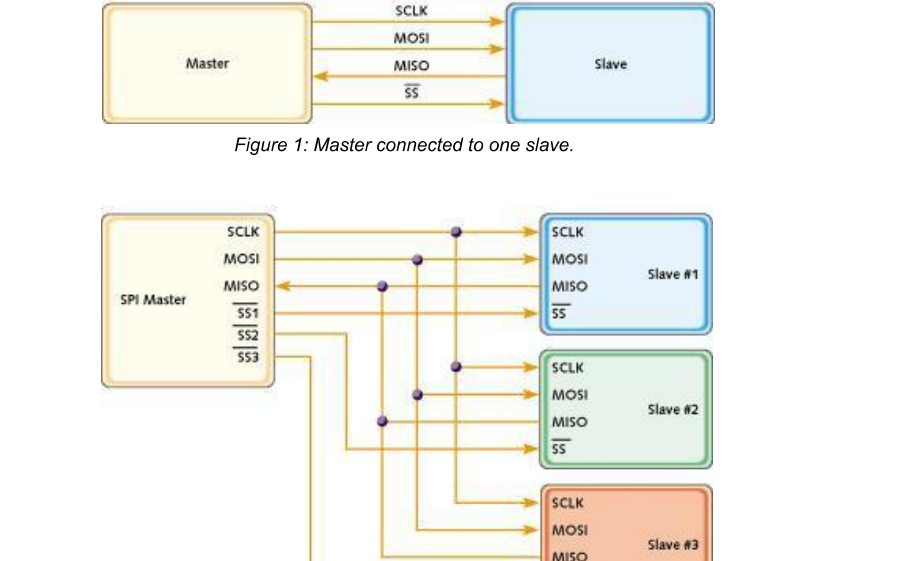

SPI是單master多slave的總線協議,全雙工通信。如下圖所示,一個master可以控制多個slave,通過ss信號選擇需要控制的slave,ss低電平有效。

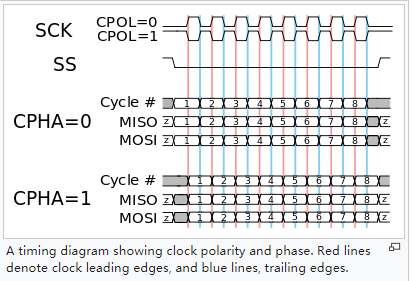

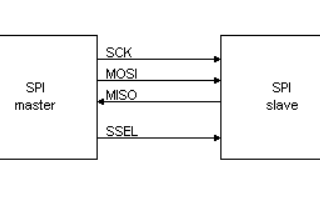

數據傳輸要遵循如下時序要求(下圖是以收發數據位數為8作為示例)。其中SCK為SCLK,由master發出,SS為Slave片選信號。其中CPOL,CPHA為模式選擇。master與slave的模式需要一致。MISO(單bit)為slave的輸出數據線,master的輸入數據線(未選中的slave的MISO為高阻態);MOSI(單bit)為master的輸出數據線,slave的輸入數據線。數據都是先發低位。

當CPOL=0,CPHA=0時:空閑時,SCLK為低電平;master和slave,在SCLK上升沿采集數據,下降沿發出數據。并在第一個SCLK上升沿之前,數據的第一bit必須送上數據線。

當CPOL=0,CPHA=1時:空閑時,SCLK為低電平;master和slave,在SCLK上升沿發出數據,下降沿采集數據。

當CPOL=1,CPHA=0時:空閑時,SCLK為高電平;master和slave,在SCLK上升沿發出數據,下降沿采集數據。并在第一個SCLK下降沿之前,數據的第一bit必須送上數據線。

當CPOL=1,CPHA=1時:空閑時,SCLK為高電平;master和slave,在SCLK上升沿采集數據,下降沿發出數據。

設計概述

本次提供了一個master接口與slave接口的參考設計。并且要求clk的時鐘頻率最好為SCLK時鐘頻率的三倍以上。當SCLK為clk的奇數倍分頻時需要考慮誤差積累問題。

SPI_master_if(SPI master接口驅動)的信號端口說明如下表:

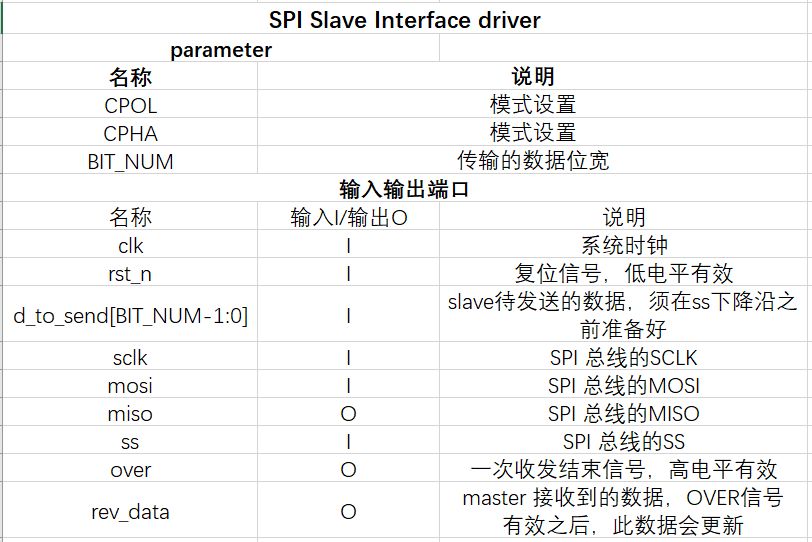

SPI_slave_if(SPI slave接口驅動)的信號端口說明如下表:

并且還提供了一個簡單的TB(SPI_tb.sv)。大家可以跑跑仿真。

目前此設計只是做了功能仿真,并未上板與其他SPI設備進行實測,如有問題,希望大家給予反饋。

-

仿真

+關注

關注

51文章

4245瀏覽量

135366 -

SPI

+關注

關注

17文章

1785瀏覽量

94878 -

驅動電路

+關注

關注

155文章

1581瀏覽量

109660

原文標題:SPI 接口驅動電路設計

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

求助。SPI接口主模式電路設計。

SPI接口主模式電路設計

無線傳感器節點SPI接口電路設計

基于CP2120的SPI與I2C總線接口轉換電路設計

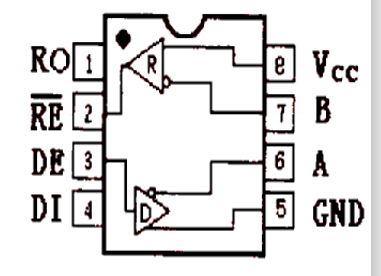

基于SPI總線的RS-422接口電路設計

基于SPI接口的凌陽單片機鍵盤設計

LED驅動電路設計中文資料概述

串行接口技術的詳細資料概述

帶有N的SPI總線詳細資料概述

SPI接口驅動電路設計的資料概述

SPI接口驅動電路設計的資料概述

評論