FPGA 的神經(jīng)網(wǎng)絡(luò)加速器如今越來越受到 AI 社區(qū)的關(guān)注,本文對基于 FPGA 的深度學(xué)習(xí)加速器存在的機(jī)遇與挑戰(zhàn)進(jìn)行了概述。

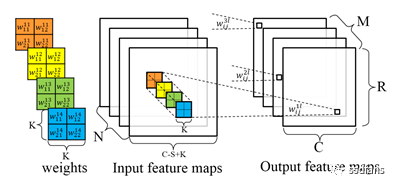

近年來,神經(jīng)網(wǎng)絡(luò)在各種領(lǐng)域相比于傳統(tǒng)算法有了極大的進(jìn)步。在圖像、視頻、語音處理領(lǐng)域,各種各樣的網(wǎng)絡(luò)模型被提出,例如卷積神經(jīng)網(wǎng)絡(luò)、循環(huán)神經(jīng)網(wǎng)絡(luò)。訓(xùn)練較好的 CNN 模型把 ImageNet 數(shù)據(jù)集上 5 類頂尖圖像的分類準(zhǔn)確率從 73.8% 提升到了 84.7%,也靠其卓越的特征提取能力進(jìn)一步提高了目標(biāo)檢測準(zhǔn)確率。RNN 在語音識別領(lǐng)域取得了最新的詞錯率記錄。總而言之,由于高度適應(yīng)大量模式識別問題,神經(jīng)網(wǎng)絡(luò)已經(jīng)成為許多人工智能應(yīng)用的有力備選項(xiàng)。

然而,神經(jīng)網(wǎng)絡(luò)模型仍舊存在計(jì)算量大、存儲復(fù)雜問題。同時,神經(jīng)網(wǎng)絡(luò)的研究目前還主要聚焦在網(wǎng)絡(luò)模型規(guī)模的提升上。例如,做 224x224 圖像分類的最新 CNN 模型需要 390 億浮點(diǎn)運(yùn)算(FLOP)以及超過 500MB 的模型參數(shù)。由于計(jì)算復(fù)雜度直接與輸入圖像的大小成正比,處理高分辨率圖像所需的計(jì)算量可能超過 1000 億。

因此,為神經(jīng)網(wǎng)絡(luò)應(yīng)用選擇適度的計(jì)算平臺特別重要。一般來說,CPU 每秒能夠完成 10-100 的 GFLOP 運(yùn)算,但能效通常低于 1 GOP/J,因此難以滿足云應(yīng)用的高性能需求以及移動 app 的低能耗需求。相比之下,GPU 提供的巔峰性能可達(dá)到 10TOP/S,因此它是高性能神經(jīng)網(wǎng)絡(luò)應(yīng)用的絕佳選擇。此外,Caffe 和 TensorFlow 這樣的編程框架也能在 GPU 平臺上提供易用的接口,這使得 GPU 成為神經(jīng)網(wǎng)絡(luò)加速的首選。

除了 CPU 和 GPU,F(xiàn)PGA 逐漸成為高能效神經(jīng)網(wǎng)絡(luò)處理的備選平臺。根據(jù)神經(jīng)網(wǎng)絡(luò)的計(jì)算過程,結(jié)合為具體模型設(shè)計(jì)的硬件,F(xiàn)PGA 可以實(shí)現(xiàn)高度并行并簡化邏輯。一些研究顯示,神經(jīng)網(wǎng)絡(luò)模型能以硬件友好的方式進(jìn)行簡化,不影響模型的準(zhǔn)確率。因此,F(xiàn)PGA 能夠取得比 CPU 和 GPU 更高的能效。

回顧 20 世紀(jì) 90 年代,那時 FPGA 剛出現(xiàn),但不是為了神經(jīng)網(wǎng)絡(luò),而是為了電子硬件原型的快速開發(fā)而設(shè)計(jì)的。由于神經(jīng)網(wǎng)絡(luò)的出現(xiàn),人們開始探索、改進(jìn)其應(yīng)用,但無法確定其發(fā)展方向。盡管在 1994 年,DS Reay 首次使用 FPGA 實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)加速,但由于神經(jīng)網(wǎng)絡(luò)自身發(fā)展不夠成熟,這一技術(shù)并未受到重視。直到 2012 年 ILSVRC 挑戰(zhàn)賽 AlexNet 的出現(xiàn),神經(jīng)網(wǎng)絡(luò)的發(fā)展?jié)u為明晰,研究社區(qū)才開始往更深、更復(fù)雜的網(wǎng)絡(luò)研究發(fā)展。后續(xù),出現(xiàn)了 VGGNet、GoogleNet、ResNet 這樣的模型,神經(jīng)網(wǎng)絡(luò)越來越復(fù)雜的趨勢更為明確。當(dāng)時,研究者開始注意到基于 FPGA 的神經(jīng)網(wǎng)絡(luò)加速器,如下圖 1 所示。直到去年,IEEE eXplore 上發(fā)表的基于 FPGA 的神經(jīng)網(wǎng)絡(luò)加速器數(shù)量已經(jīng)達(dá)到了 69 個,且還在一直增加。這足以說明該方向的研究趨勢。

圖 1:基于 FPGA 的神經(jīng)網(wǎng)絡(luò)加速器開發(fā)歷史

論文:A Survey of FPGA Based Deep Learning Accelerators: Challenges and Opportunities

論文地址:https://arxiv.org/abs/1901.04988

摘要:隨著深度學(xué)習(xí)的快速發(fā)展,神經(jīng)網(wǎng)絡(luò)和深度學(xué)習(xí)算法已經(jīng)廣泛應(yīng)用于各個領(lǐng)域,如圖片、視頻和語音處理等。但是,神經(jīng)網(wǎng)絡(luò)模型也變得越來越大,這體現(xiàn)在模型參數(shù)的計(jì)算上。雖然為了提高計(jì)算性能,研究者在 GPU 平臺上已經(jīng)做了大量努力,但專用硬件解決方案仍是必不可少的,而且與純軟件解決方案相比正在形成優(yōu)勢。在這篇論文中,作者系統(tǒng)地探究了基于 FPGA 的神經(jīng)網(wǎng)絡(luò)加速器。具體來講,他們分別回顧了針對特定問題、特定算法、算法特征、通用模板的加速器,還比較了不同設(shè)備和網(wǎng)絡(luò)模型中基于 FPGA 加速器的設(shè)計(jì)和實(shí)現(xiàn),并將其與 CPU 和 GPU 的版本進(jìn)行了比較。最后,作者討論了 FPGA 平臺上加速器的優(yōu)勢和劣勢,并進(jìn)一步探索了未來研究存在的機(jī)會。

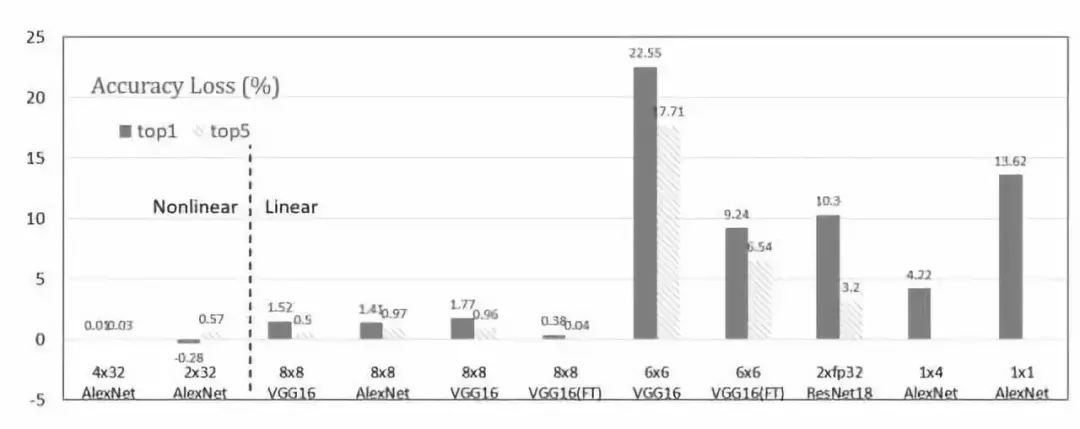

圖 2: 不同數(shù)據(jù)量化方法的比較

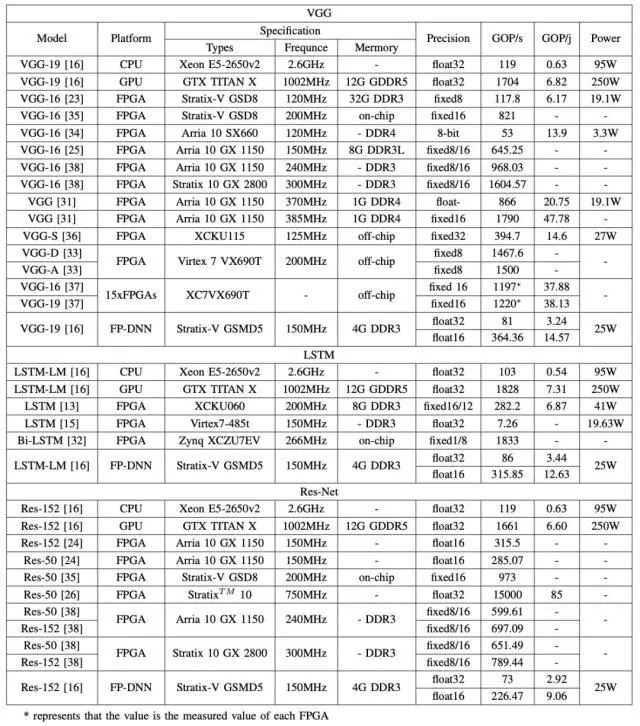

表 1: 不同平臺上不同模型的性能比較

機(jī)遇和挑戰(zhàn)

早在 20 世紀(jì) 60 年代,Gerald Estrin 就提出了可重構(gòu)計(jì)算的概念。但是直到 1985 年,第一個 FPGA 芯片才被 Xilinx 引入。盡管 FPGA 平臺的并行性和功耗非常出色,但由于其重構(gòu)成本高,編程復(fù)雜,該平臺沒有引起人們的重視。隨著深度學(xué)習(xí)的持續(xù)發(fā)展,其應(yīng)用的高并行性使得越來越多的研究人員投入到基于 FPGA 的深度學(xué)習(xí)加速器研究中來。這也是時代的潮流。

基于 FPGA 加速器的優(yōu)勢

1)高性能,低能耗:高能效的優(yōu)點(diǎn)不容小覷,之前的許多研究已經(jīng)證明了這一點(diǎn)。從表 1 中可以看出,GOP/j 在 FPGA 平臺上的表現(xiàn)可以達(dá)到在 CPU 平臺上的幾十倍,它在 FPGA 平臺上表現(xiàn)的最低水平與其在 GPU 平臺上的表現(xiàn)處于一個層級。這足以說明基于 FPGA 的神經(jīng)網(wǎng)絡(luò)加速器的高能效優(yōu)勢。

2)高并行性:高并行性是選擇 FPGA 平臺加速深度學(xué)習(xí)的主要特性。由于 FPGA 的可編輯邏輯硬件單元,可以使用并行化算法輕松優(yōu)化硬件,已達(dá)到高并行性。

3)靈活性:由于 FPGA 具有可重構(gòu)性,它可以適用于復(fù)雜的工程環(huán)境。例如,在硬件設(shè)計(jì)和應(yīng)用設(shè)計(jì)完成之后,通過實(shí)驗(yàn)發(fā)現(xiàn)性能未能達(dá)到理想狀態(tài)。可重構(gòu)性使得基于 FPGA 的硬件加速器能夠很好地處理頻繁的設(shè)計(jì)變更并滿足用戶不斷變化的需求。因此,與 ASIC 平臺相比,這種靈活性也是 FPGA 平臺的亮點(diǎn)。

4)安全性:當(dāng)今的人工智能時代需要越來越多的數(shù)據(jù)用于訓(xùn)練。因此,數(shù)據(jù)的安全性越來越重要。作為數(shù)據(jù)的載體,計(jì)算機(jī)的安全性也變得更加顯著。目前,一提到計(jì)算機(jī)安全性,想到的都是各種殺毒軟件。但是這些軟件只能被動地防御,不能消除安全風(fēng)險(xiǎn)。相比之下,從硬件架構(gòu)層級著手能夠更好地提高安全性。

基于 FPGA 的加速器的劣勢

1)可重構(gòu)成本:FPGA 平臺的可重構(gòu)性是一把雙刃劍。盡管它在計(jì)算提速方面提供了許多便利,但是不同設(shè)計(jì)的重構(gòu)所消耗的時間卻不容忽視,通常需要花幾十分鐘到幾個小時。此外,重構(gòu)過程分為兩種類型:靜態(tài)重構(gòu)和動態(tài)重構(gòu)。靜態(tài)重構(gòu),又叫編譯時重構(gòu),是指在任務(wù)運(yùn)行之前配置硬件處理一個或多個系統(tǒng)功能的能力,并且在任務(wù)完成前將其鎖定。另一個也稱為運(yùn)行時配置。動態(tài)重構(gòu)是在上下文配置模式下進(jìn)行的。在執(zhí)行任務(wù)期間,硬件模塊應(yīng)該按照需要進(jìn)行重構(gòu)。但是它非常容易延遲,從而增加運(yùn)行時間。

2)編程困難:盡管可重構(gòu)計(jì)算架構(gòu)的概念被提出很久了,也有很多成熟的工作,但可重構(gòu)計(jì)算之前并未流行起來。主要有兩個原因:

從可重構(gòu)計(jì)算的出現(xiàn)到 21 世紀(jì)初的 40 年時間是摩爾定律的黃金時期,其間技術(shù)每一年半更迭一次。所以這種架構(gòu)更新帶來的性能提升不像技術(shù)進(jìn)步那么直接、有力;對成熟的系統(tǒng)而言,在 CPU 上傳統(tǒng)的編程采用高階抽象編程語言。但是,可重構(gòu)計(jì)算需要硬件編程,而通常使用的硬件編程語言(Verilog、VHDL)需要程序員花費(fèi)大量時間才能掌握。

期望

盡管基于 FPGA 的神經(jīng)網(wǎng)絡(luò)加速器仍舊有這樣、那樣的問題,但其未來發(fā)展依然可期。以下幾個方向仍然有待研究:

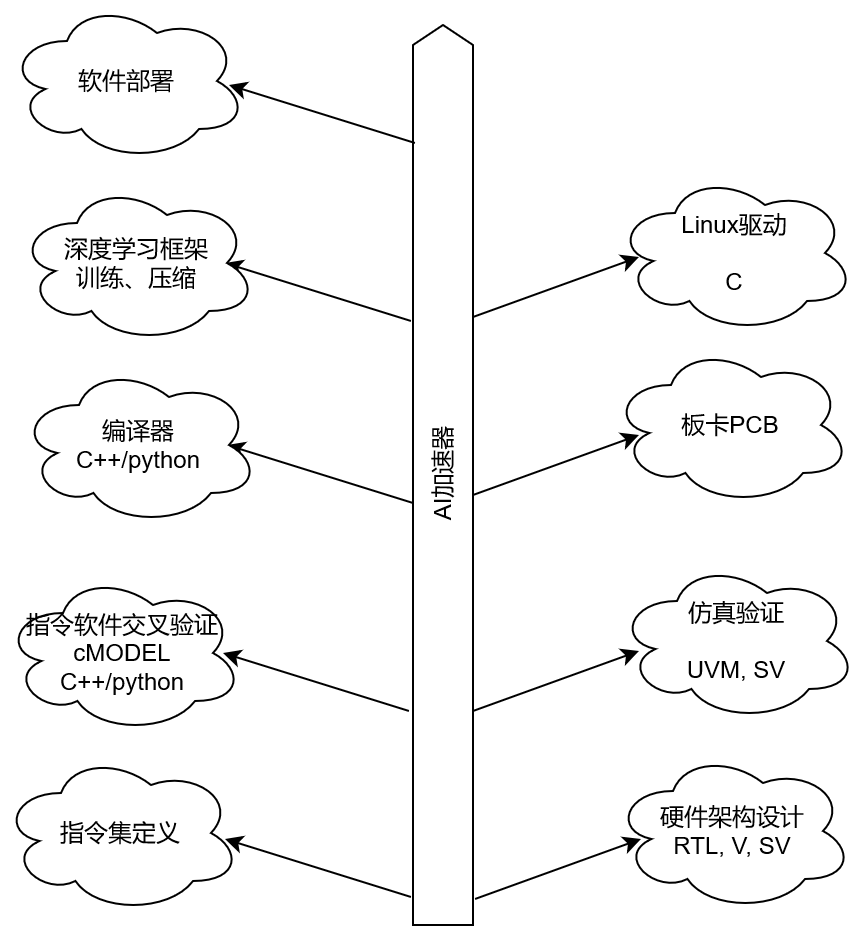

優(yōu)化計(jì)算流程中的其他部分,現(xiàn)在,主流研究聚焦在矩陣運(yùn)算回路,激活函數(shù)的計(jì)算少有人涉及。訪問優(yōu)化。需要進(jìn)一步研究進(jìn)行數(shù)據(jù)訪問的其他優(yōu)化方法。數(shù)據(jù)優(yōu)化。使用能夠自然提升平臺性能的更低位數(shù)據(jù),但大部分的低位數(shù)據(jù)使得權(quán)重和神經(jīng)元的位寬一樣。圖 2 還可以改進(jìn)與非線性映射的位寬差。所以,應(yīng)該探索出更好的平衡態(tài)。頻率優(yōu)化。當(dāng)前,大部分 FPGA 平臺的運(yùn)算頻率在 100-300MHz,但 FPGA 平臺理論上的運(yùn)算頻率可以更高。這一頻率主要受限于片上 SRAM 和 DSP 之間的線程。未來研究需要找到是否有方式避免或者解決該問題。FPGA 融合。據(jù)參考論文 37 中提到的表現(xiàn),如果規(guī)劃和分配問題能夠得到良好解決,多 FPGA 集群可以取得更好的結(jié)果。此外,當(dāng)前此方向沒有太多研究。所以非常值得進(jìn)一步探索。自動配置。為了解決 FPGA 平臺上復(fù)雜的編程問題,如果做出類似英偉達(dá) CUDA 這樣的用戶友好的自動部署框架,應(yīng)用范圍肯定會拓寬。

-

FPGA

+關(guān)注

關(guān)注

1638文章

21883瀏覽量

610751 -

加速器

+關(guān)注

關(guān)注

2文章

819瀏覽量

38692 -

AI

+關(guān)注

關(guān)注

87文章

33200瀏覽量

273458 -

深度學(xué)習(xí)

+關(guān)注

關(guān)注

73文章

5536瀏覽量

122193

原文標(biāo)題:基于FPGA的深度學(xué)習(xí)加速器的挑戰(zhàn)與機(jī)遇

文章出處:【微信號:gh_c472c2199c88,微信公眾號:嵌入式微處理器】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA在做深度學(xué)習(xí)加速時需要的技能

華為FPGA加速云服務(wù)器如何加速讓硬件應(yīng)用高效上云?

機(jī)器學(xué)習(xí)實(shí)戰(zhàn):GNN加速器的FPGA解決方案

一種基于FPGA的圖神經(jīng)網(wǎng)絡(luò)加速器解決方案

英特爾推出深度學(xué)習(xí)加速器和新一代至強(qiáng)芯片抗衡英偉達(dá)

優(yōu)化基于FPGA的深度卷積神經(jīng)網(wǎng)絡(luò)的加速器設(shè)計(jì)

FPGA在深度學(xué)習(xí)領(lǐng)域的應(yīng)用

FPGA做深度學(xué)習(xí)加速的技能總結(jié)

基于深度學(xué)習(xí)的矩陣乘法加速器設(shè)計(jì)方案

基于AdderNet的深度學(xué)習(xí)推理加速器

2022 谷歌出海創(chuàng)業(yè)加速器展示日: 見證入營企業(yè)成長收獲

基于FPGA的深度學(xué)習(xí)CNN加速器設(shè)計(jì)方案

Rapanda流加速器-實(shí)時流式FPGA加速器解決方案

FPGA的深度學(xué)習(xí)加速器有怎樣的挑戰(zhàn)和機(jī)遇

FPGA的深度學(xué)習(xí)加速器有怎樣的挑戰(zhàn)和機(jī)遇

評論