1. 什么是SSI芯片?

SSI是Stacked Silicon Interconnect的縮寫(xiě)。SSI芯片其實(shí)就是我們通常所說(shuō)的多die芯片。其基本結(jié)構(gòu)如下圖所示。可以看到SSI芯片的基本單元是SLR(Super Logic Region),也就是我們所說(shuō)的die。SLR之間通過(guò)Interposer“粘合”在一起。每個(gè)SLR可看做一片小規(guī)模FPGA。

2. 如何從芯片型號(hào)上判斷FPGA是否是多die芯片?

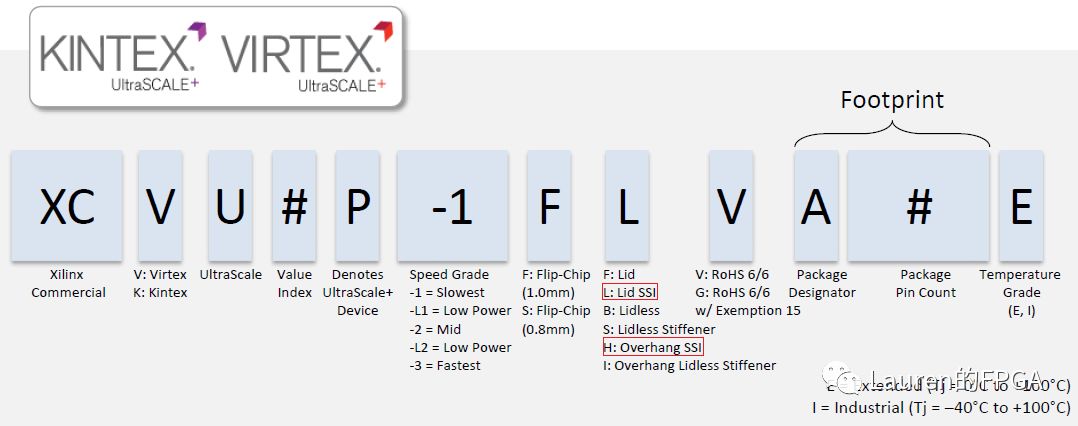

在芯片選型手冊(cè)上,有如下圖所示說(shuō)明,根據(jù)圖中紅色方框標(biāo)記可判斷該芯片是否是SSI芯片。

3. UltraScale和UltraScale+系列有哪些芯片是SSI芯片?

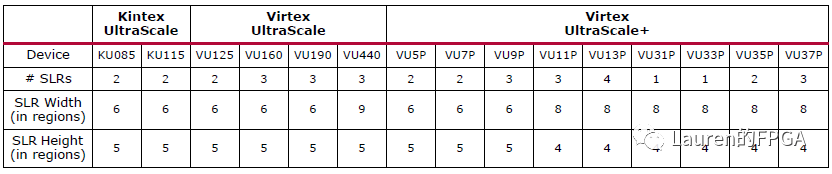

總的來(lái)說(shuō),UltraScale+大部分都是多die芯片,如下圖所示。圖中還可以看到每個(gè)芯片所包含的SLR的個(gè)數(shù)以及每個(gè)SLR的大小。SLR的大小以時(shí)鐘區(qū)域(Clock Region)衡量,例如,VU5P有兩個(gè)SLR,每個(gè)SLR的寬度為6,高度為5,所以共有6x5也就是30個(gè)Clock Region。同時(shí),還可以看到每個(gè)SLR的大小是一致的。

圖片來(lái)源:Table 19,ds890

4. 在Vivado下如何判斷芯片是多die芯片?

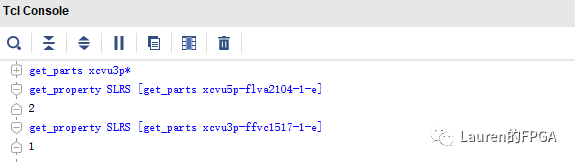

只要獲知芯片的具體型號(hào),在Vivado Tcl Console中執(zhí)行如下圖所示命令即可獲得該芯片所包含的SLR的個(gè)數(shù)。例如,對(duì)于XCVU5P,屬性SLRS的返回值為2,說(shuō)明該芯片有兩個(gè)SLR,故其是多die芯片;而對(duì)于XCVU3P,返回值為1,說(shuō)明該芯片只有一個(gè)SLR,故其是單die芯片。

5. 多die芯片的每個(gè)SLR地位一樣嗎?

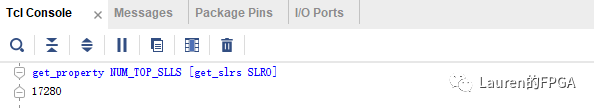

多die芯片的每個(gè)SLR其結(jié)構(gòu)基本是一致的,都包含CLB、Block RAM、DSP和GT等。但這些SLR的地位是不一樣的。這其中只有一個(gè)SLR是Master SLR。通過(guò)如下圖所示的命令可獲取Master SLR(需要在打開(kāi)的工程中或DCP中執(zhí)行該命令)。通常SLR0為Master SLR。用于配置FPGA的電路、DNA_PORT和EFUSE_USER只存在于Master SLR中。

6. SLR之間是如何互連的?

這是多die芯片設(shè)計(jì)中的一個(gè)重要問(wèn)題。SLR之間通過(guò)專用布線資源SLL(Super Long Line)互連。SLL的個(gè)數(shù)是有限的。以XCVU5P為例,可通過(guò)如下命令獲取SLL的個(gè)數(shù)。這在設(shè)計(jì)初期是非常重要的。需要根據(jù)此數(shù)值評(píng)估跨die網(wǎng)線個(gè)數(shù)是否合理。跨die網(wǎng)線過(guò)多很可能造成布線擁塞,進(jìn)而影響時(shí)序收斂。

7. 跨die時(shí)鐘需要特殊處理嗎?

對(duì)于SSI器件,Interposer上分布了專用的全局時(shí)鐘走線,因此,對(duì)于跨die時(shí)鐘并不需要特殊處理,同時(shí)該時(shí)鐘也不會(huì)占用SLL。

8. Block RAM和DSP48能否跨die級(jí)聯(lián)?

以DSP48為例,其有專門(mén)的級(jí)聯(lián)端口,例如PCOUT/PCIN。因此,相鄰的兩個(gè)DSP48級(jí)聯(lián)時(shí),會(huì)使用專用的級(jí)聯(lián)布線資源。但是,這種布線資源僅限于die內(nèi)。類似地,Block RAM、Carry Chain等在die內(nèi)可使用固有的級(jí)聯(lián)布線資源。

9. 對(duì)于多die芯片,如何評(píng)估資源利用率?

器件選型階段需要根據(jù)設(shè)計(jì)規(guī)模選擇合適的芯片。這個(gè)階段,需要根據(jù)整個(gè)設(shè)計(jì)的資源利用率確定芯片規(guī)模。一旦選定SSI器件,就要及早考慮模塊劃分,也就是如何將設(shè)計(jì)分配到每個(gè)die內(nèi),使每個(gè)die的資源利用率盡可能平衡,此時(shí)就要考慮每個(gè)die的資源利用率,避免出現(xiàn)某個(gè)die某一資源利用率過(guò)高以至于出現(xiàn)擁塞,而另一個(gè)die該資源利用率偏低的情形。這一工作要在設(shè)計(jì)初期完成,本質(zhì)上就是要設(shè)計(jì)好合理的數(shù)據(jù)流,從而達(dá)到兩個(gè)目的:每個(gè)die的資源利用率比較均衡;跨die網(wǎng)線個(gè)數(shù)合理。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618472 -

芯片

+關(guān)注

關(guān)注

460文章

52520瀏覽量

440900 -

SSI

+關(guān)注

關(guān)注

0文章

38瀏覽量

19653

原文標(biāo)題:9個(gè)關(guān)于SSI芯片的必知問(wèn)題

文章出處:【微信號(hào):Lauren_FPGA,微信公眾號(hào):FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

HMC347A-Die單刀雙擲(SPDT)

XSR芯片間互連技術(shù)的定義和優(yōu)勢(shì)

如何判斷ADC芯片的類型?

芯片 FT 測(cè)試提速秘籍 ?Setup 優(yōu)化 + 硬件巧選 + 多 site #芯片 #國(guó)產(chǎn)

利用新思科技Multi-Die解決方案加快創(chuàng)新速度

利用Multi-Die設(shè)計(jì)的AI數(shù)據(jù)中心芯片對(duì)40G UCIe IP的需求

一文解析多芯片封裝技術(shù)

Die Bonding 芯片鍵合的主要方法和工藝

如何判斷LMH6703MF芯片引腳?

快速串行接口(FSI)在多芯片互連中的應(yīng)用

在Vivado下如何判斷芯片是多die芯片

在Vivado下如何判斷芯片是多die芯片

評(píng)論