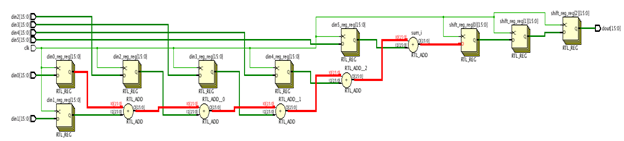

重定時(shí)(Retiming)是一種時(shí)序優(yōu)化技術(shù),用在不影響電路輸入/輸出行為的情況下跨組合邏輯寄存器從而提高設(shè)計(jì)性能。圖1所示的電路是六輸入加法器,其中有一條關(guān)鍵路徑,紅色推出顯示的路徑是限制整個(gè)電路性能的關(guān)鍵路徑。

圖1:六輸入加法器寄存器到寄存器之間的信號(hào)路徑示例

通過(guò)對(duì)加法器輸出路徑上寄存器進(jìn)行重定時(shí)設(shè)計(jì),調(diào)整電路的組合邏輯,可以改變整個(gè)電路的性能。

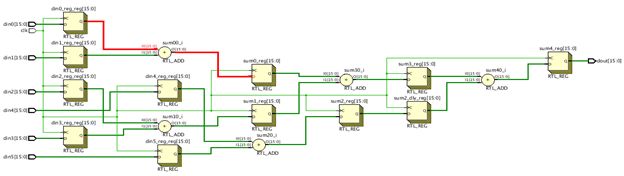

整個(gè)電路的延遲是4,圖2展示的是一種寄存器組合方法可以將邏輯最小化,將輸出寄存器融合到邏輯寄存器中稱為向后重定時(shí)設(shè)計(jì),這一步完成后關(guān)鍵路徑被壓縮為二輸入加法器。

圖2:采用向后重定時(shí)方案二輸入加法器寄存器到寄存器路徑設(shè)計(jì)的一個(gè)示例

關(guān)于上述 示例需要注意的另一點(diǎn)是寄存器數(shù)量的變化。

圖1采用9個(gè)不同寄存器總線,圖2使用了12個(gè)不同寄存器總線,產(chǎn)生這樣結(jié)果的原因是當(dāng)采用向后重定時(shí)設(shè)計(jì)時(shí),當(dāng)寄存器從輸出移動(dòng)到輸入時(shí),邏輯門(mén)的兩個(gè)輸入都必須增加一個(gè)寄存器。

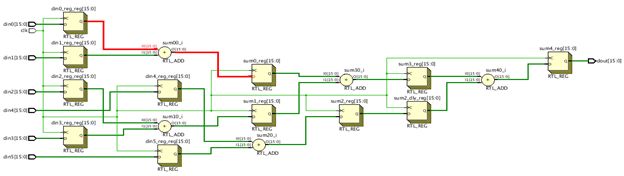

有兩種不同的重定時(shí)方法,向后重定時(shí)和向前重定時(shí)。向后重定時(shí)從門(mén)的輸出中刪除寄存器,并在同一邏輯門(mén)的輸入出創(chuàng)建新的寄存器。向前重定時(shí)的作用正好相反,它從邏輯門(mén)的輸入中刪除寄存器,并在輸出中創(chuàng)建新的寄存器。

若要向后重定時(shí),組合邏輯必須僅用來(lái)驅(qū)動(dòng)寄存器,而不能向其他邏輯寄存器展開(kāi),為了使前向重定時(shí)正常工作,邏輯門(mén)的每個(gè)輸入必須有具有相同控制邏輯的寄存器來(lái)驅(qū)動(dòng)。

圖3:邏輯與門(mén)(AND)采用前向重定時(shí)和后向重定時(shí)的效果

全局重定時(shí)vs 局部重定時(shí)

在Vivado 綜合操作中有兩種方法實(shí)現(xiàn)自動(dòng)重定時(shí):全局重定時(shí)和局部重定時(shí)。

全局重定時(shí)是對(duì)整個(gè)設(shè)計(jì)而言的,基于設(shè)計(jì)時(shí)的時(shí)序要求優(yōu)化大型組合邏輯結(jié)構(gòu)中的寄存器設(shè)計(jì)。

這種方式需要分析設(shè)計(jì)中的所有邏輯,優(yōu)化最壞路徑情況下的寄存器從而使整體設(shè)計(jì)反應(yīng)速度更快。為了實(shí)現(xiàn)這一點(diǎn)設(shè)計(jì)時(shí)必須在.xdc文件中規(guī)定準(zhǔn)確的時(shí)間限制。在synth_design或Vivado GUI綜合設(shè)置下通過(guò)-retiming命令啟用全局重定時(shí),此外該特性還可以與合成中的BLOCK_SYNTH特性一起用于設(shè)計(jì)中的特定模塊。

局部重定時(shí)是指用戶明確告訴工具使用retiming_forward、retiming_bbackward RTL屬性時(shí)需要執(zhí)行的重定時(shí)邏輯。

執(zhí)行局部重定時(shí)操作是應(yīng)該要小心,因?yàn)樗皇怯?jì)時(shí)器驅(qū)動(dòng)的,而是工具將完全按照用戶要求去執(zhí)行。

有關(guān)重定時(shí)使用的更多信息,請(qǐng)參閱(UG901)Vivado設(shè)計(jì)工具用戶指南:Synthesis(綜合)。

分析日志文件中的信息

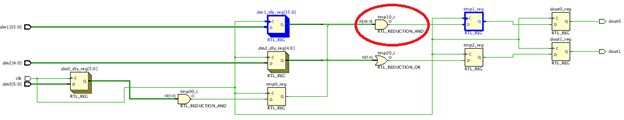

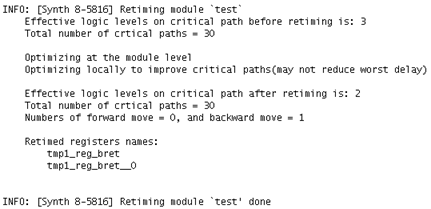

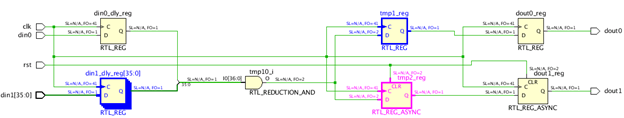

圖4是通過(guò)重定時(shí)提升邏輯水平的一個(gè)例子,該電路結(jié)構(gòu)中有一個(gè)關(guān)鍵的路徑分為三個(gè)邏輯層,組成的是一個(gè)37位的邏輯與門(mén)(AND),源寄存器命名為din1_dly_reg,目標(biāo)寄存器命名為tmp1_reg,在邏輯級(jí)別為0的tmp1_reg后面增加一個(gè)額外的寄存器。

這是一個(gè)理想的重定時(shí)邏輯路徑設(shè)計(jì),因?yàn)槲覀兛梢郧袚Q為三個(gè)邏輯級(jí)別的路徑,由0、1、2三個(gè)局部邏輯電路模塊組成。

圖4:采用后向重定時(shí)設(shè)計(jì)的電路

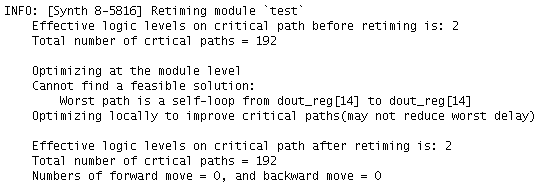

綜合操作日志文件包含的信息大致如下:

從這個(gè)日志文件中你可以看到重定時(shí)操作前后的邏輯門(mén)信息對(duì)比,以及創(chuàng)建的新寄存器名稱,當(dāng)synthesis通過(guò)重定時(shí)創(chuàng)建新寄存器時(shí),它將對(duì)后向重定時(shí)的寄存器使用后綴“bret”,對(duì)前向重定時(shí)寄存器使用后綴“fret”。

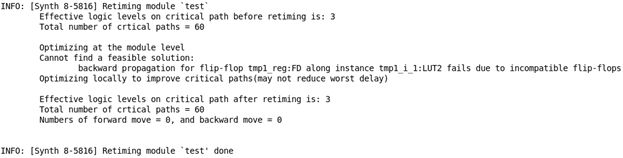

圖5展示的電路中一些不兼容的寄存器將無(wú)法進(jìn)行重定時(shí)操作,這個(gè)結(jié)構(gòu)中同樣有一個(gè)名為din1_dly_reg的源寄存器,它經(jīng)過(guò)37位邏輯與門(mén)生成三級(jí)邏輯電路結(jié)構(gòu),然后在din1_dly_reg寄存器前結(jié)束。此外邏輯與門(mén)還有一路連接到另外一個(gè)寄存器,如下圖粉色高亮顯示的部分。

圖5:不能進(jìn)行重定時(shí)操作電路的示例

這是示例不能進(jìn)行重定時(shí)操作是因?yàn)榉奂t色高亮顯示的部分,這個(gè)寄存器需要一部重置,而tmp1_reg沒(méi)有這個(gè)功能,因?yàn)檫@兩個(gè)寄存器沒(méi)有相同的控制集,所以它們不能向后重定時(shí)到新的邏輯與門(mén)電路中,本例的日志文件信息如下:

這個(gè)日志文件包含的信息是關(guān)于 不兼容的FIFO寄存器的,前后的電路的邏輯層級(jí)不變。

以下情況下不能進(jìn)行重定時(shí)操作:1. 寄存器時(shí)序異常(多循環(huán)路徑、錯(cuò)誤的路徑、最大延遲路徑)2. 寄存器的類型屬性不能改變(DONT_TOUCH, MARK_DEBUG)3. 采用不同控制級(jí)的寄存器

驅(qū)動(dòng)輸出的寄存器或者被輸入驅(qū)動(dòng)的寄存器(除非這部分是與前后電路不相關(guān)的)

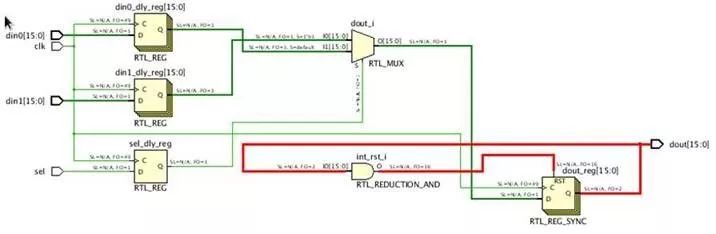

重定時(shí)無(wú)法改善反饋循環(huán)回路中關(guān)鍵路徑的性能的一個(gè)例子:

當(dāng)路徑中具有相同的源寄存器和目標(biāo)寄存器時(shí),重定時(shí)優(yōu)化操作可能無(wú)法改進(jìn)整個(gè)邏輯電路的結(jié)構(gòu)。

舉個(gè)例子:

寄存器“dout_reg”的關(guān)鍵路徑如下圖中紅色所示,要經(jīng)過(guò)一個(gè)邏輯與運(yùn)算,然后連接到同一寄存器的復(fù)位管腳上才算結(jié)束。

根據(jù)數(shù)位寬度(16比特)邏輯與門(mén)電路要占用兩個(gè)邏輯操作。

下面的屏幕截圖顯示了綜合操作如何描述關(guān)鍵路徑的

其中還提到了關(guān)鍵路徑中一部分模塊或寄存器的名字。

-

寄存器

+關(guān)注

關(guān)注

31文章

5424瀏覽量

123509 -

總線

+關(guān)注

關(guān)注

10文章

2953瀏覽量

89404 -

Vivado

+關(guān)注

關(guān)注

19文章

831瀏覽量

68309

原文標(biāo)題:Vivado綜合操作中的重定時(shí)(Retiming)

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開(kāi)發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Vivado 高層次綜合

探索Vivado HLS設(shè)計(jì)流,Vivado HLS高層次綜合設(shè)計(jì)

vivado 2015.3 綜合報(bào)錯(cuò)

Vivado 2015.4許可證與Windows 10操作系統(tǒng)工作出現(xiàn)綜合錯(cuò)誤

Vivado綜合操作中的重定時(shí)(Retiming)

運(yùn)行綜合時(shí)Vivado崩潰

在vivado中綜合Soc設(shè)計(jì)時(shí)發(fā)現(xiàn)的錯(cuò)誤,請(qǐng)問(wèn)如何解決?

如何為管道設(shè)計(jì)插入寄存器并進(jìn)行重定時(shí)?

Vivado 全局重定時(shí)vs 局部重定時(shí)

使用Vivado高層次綜合 (HLS)進(jìn)行FPGA設(shè)計(jì)的簡(jiǎn)介

Vivado綜合引擎的增量綜合流程

Vivado綜合參數(shù)設(shè)置

Vivado綜合階段什么約束生效?

Vivado Design Suite用戶指南:綜合

如何運(yùn)用Retiming優(yōu)化Block RAM的使用

Vivado綜合操作中的重定時(shí)(Retiming)

Vivado綜合操作中的重定時(shí)(Retiming)

評(píng)論