Q值。我需要數據轉換器以適應狹小的空間,我懷疑串行接口會有所幫助。選擇和使用一個我需要知道什么?

A。讓我們首先看一下串行接口的工作方式,然后將其與并行接口進行比較。在此過程中,我們將消除有關串行數據轉換器的一些神話。

該圖顯示了連接到串行端口的AD7890 8通道多路復用12位串行A / D轉換器(ADC)。 ADSP-2105數字信號處理器(DSP)。還顯示了DSP用于與ADC通信的時序。構成轉換結果的12位作為串行數據流通過單線傳輸。數據流還包括三個附加位,用于標識AD7890多路復用器當前選擇的輸入通道。為了區分串行數據流的位,必須通常由DSP提供時鐘信號(SCLK);但是,有時ADC會將此時鐘作為輸出提供。 DSP通常(但不總是)提供額外的成幀脈沖,該通信脈沖在通信開始時的一個周期內有效,或者如圖所示(TFS / RFS),在發送期間有效。

在本例中,DSP的串行端口用于編程ADC中的內部5位寄存器。寄存器的位控制諸如選擇要轉換的通道,將器件置于掉電模式以及開始轉換等功能。顯然,在這種情況下,串行接口必須是雙向的。

另一方面,并行ADC直接(或可能通過緩沖器)連接到與其連接的處理器的數據總線。該圖顯示AD7892與ADSP-2101接口。轉換完成后,AD7892會中斷DSP,通過單次讀取ADC的解碼存儲器地址來響應。

串行和并行數據轉換器之間的關鍵區別在于數量需要的接口線。從節省空間的角度來看,由于減少了器件引腳數,串行轉換器具有明顯的優勢。這使得可以將12位串行ADC或DAC封裝在8引腳DIP或SO封裝中。更重要的是,節省了電路板空間,因為串行接口連接需要更少的PCB軌道。

Q.我的數模轉換器必須遠離中央處理器并彼此遠離。處理此問題的最佳方法是什么?

A.最初,您必須決定是使用串行DAC還是并行DAC。使用并行DAC,您可以將每個DAC映射到內存映射的I / O位置,如圖所示。然后,您只需對相應的I / O位置執行寫入命令即可對每個DAC進行編程。然而,這種配置具有明顯的缺點。它需要并行數據總線以及一些控制信號到所有遠程位置。顯然,一個串行接口,可以只有兩根電線,更經濟。

串行轉換器通常不能映射到處理器的內存中。但是許多串行DAC可以連接到處理器的串行I / O端口。然后,處理器上的其他端口可用于生成片選信號,以單獨啟用DAC。片選信號需要從每個器件到接口的線路。但是處理器上可以配置為發送芯片選擇信號的線路數量可能會有限制。

解決此問題的一種方法是使用可以菊花鏈式連接在一起的串行DAC 。該圖顯示了如何將多個DAC連接到單個I / O端口。每個DAC都有一個串行數據輸出(SDO)引腳,該引腳連接到鏈中下一個DAC的串行數據輸入(SDI)引腳。 LDAC和SCLK并行饋送到鏈中的所有DAC。由于時鐘輸入SDI的數據最終出現在SDO(N個時鐘周期之后),因此單個I / O端口可以尋址多個DAC。但是,端口必須輸出長數據流(每個DAC的N位乘以鏈中的設備數)。這種配置的最大優點是不需要設備解碼。所有設備都有效地位于相同的I / O位置。菊花鏈的主要缺點是可訪問性(或延遲)。要更改單個DAC的狀態,處理器仍必須從I / O端口輸出完整的數據流。

Q.如果串行數據轉換器節省了太多的空間和線路,為什么不在每個對空間敏感的應用中使用它們?

A。串行接口的主要缺點是空間速度的權衡。例如,要對并行DAC進行編程,只需將數據置于數據總線上,然后通過單脈沖將其計入DAC。但是,當寫入串行DAC時,這些位必須按順序計時(N位轉換器為N個時鐘脈沖),然后是加載脈沖。處理器的I / O端口花費相當多的時間與串行轉換器通信。因此,吞吐率高于500 ksps的串行轉換器并不常見。

Q值。我的8位處理器沒有串行端口。有沒有辦法將AD7893等串行12位ADC連接到處理器的并行總線?

A。它當然可以使用外部移位寄存器來完成,該寄存器是串行(并且異步)加載,然后輸入處理器的并行端口。但是,如果問題的意義是“沒有外部邏輯”,則可以將串行ADC接口,就好像它是1位并行ADC一樣。將轉換器的SDATA引腳連接到處理器的數據總線之一(它連接到圖中的D0)。使用一些解碼邏輯,轉換器可以映射到處理器的一個存儲器位置,以便可以使用12個連續的讀取命令讀取轉換結果。然后,附加軟件命令將讀取的12個字節的LSB集成到一個12位并行字中。

這種技術有時被稱為“位沖擊”,非常從軟件角度來看效率低下。但在處理器運行速度比轉換器快得多的應用中可能是可以接受的。

Q.在最后一個示例中,處理器寫入信號的門控版本用于啟動AD7893上的轉換。這種方法有問題嗎?

A。我很高興你發現了這一點。在此示例中,可以通過對AD7893的映射存儲器位置進行虛擬寫操作來啟動轉換。沒有數據交換,但處理器提供開始轉換所需的寫脈沖。從硬件角度來看,這種配置非常簡單,因為它避免了生成轉換信號的需要。但是,在交流數據采集應用中不推薦使用該技術,其中必須定期對信號進行采樣。即使處理器被編程為對ADC進行周期性寫入,寫入脈沖上的相位抖動也會嚴重降低可達到的信噪比(SNR)。選通過程可能使寫信號抖動更加嚴重。例如,采樣時鐘相位抖動電平僅為1 ns,會使理想的100 kHz正弦波的SNR降低到約60 dB(小于10個有效位分辨率)。還存在一個額外的危險,即采樣信號上的過沖和噪聲會進一步降低模數轉換的完整性。

Q.我應該選擇具有異步串行接口的轉換器嗎?

A。異步鏈接允許設備相互交換非時鐘數據。必須首先將設備編程為使用相同的數據格式。這涉及設置特定數據速率(通常以波特或每秒位數表示)。定義如何啟動和結束傳輸的約定也是必要的。我們使用名為 start 和 stop 位的可識別數據序列來執行此操作。傳輸還可以包括便于錯誤檢測的奇偶校驗位。

該圖顯示了AD1B60數字化信號調理器如何與PC的異步COM端口連接。這是一個3線雙向接口(為清晰起見,省略了地線)。請注意,接收和傳輸線路在線路的另一端交換角色。

異步數據鏈接在設備偶爾進行通信的應用程序中很有用。由于每次傳輸都包含啟動和停止位,因此設備可以通過簡單地輸出其數據隨時啟動通信。由于不再需要時鐘和控制信號,因此減少了設備之間的連接數量。

Q.我正在考慮的ADC數據表建議在串行接口上使用非連續時鐘。為什么?

A。規范可能要求在轉換過程中時鐘保持不活動狀態。有些ADC需要這樣做,因為連續的數據時鐘可以通過器件的模擬部分,并對轉換的完整性產生不利影響。如果I / O端口具有成幀脈沖,則在轉換期間可以中斷連續時鐘信號;它被用作門控信號,僅在數據傳輸期間啟用串行時鐘到轉換器。

Q.什么使器件SPI或MICROWIRE兼容?

A。SPI(串行外設接口)和MICROWIRE分別是Motorola和National Semiconductor開發的串行接口標準。大多數同步串行轉換器可以輕松連接到這些端口;但在某些情況下,可能需要額外的“粘合”邏輯。

Q.好。我決定放棄偏見,在我目前的設計中使用串行ADC。我剛剛按照數據表的規定連接了它。當我的micro讀取轉換結果時,ADC似乎總是輸出FFFHEX。發生了什么事?

A。也許您遇到了通訊問題。我們需要查看ADC和處理器之間的連接以及如何設置時序和控制信號。我們還需要查看中斷結構。下一部分將回到此問題,討論設計串行接口時遇到的問題。

-

轉換器

+關注

關注

27文章

8970瀏覽量

150889 -

串行

+關注

關注

0文章

237瀏覽量

34351

發布評論請先 登錄

怎么實現串行到并行轉換器

12位串行I/O轉換器的應用

用于串行IO 8位AD轉換器連接到微處理器的INS8072系列的技術的描述

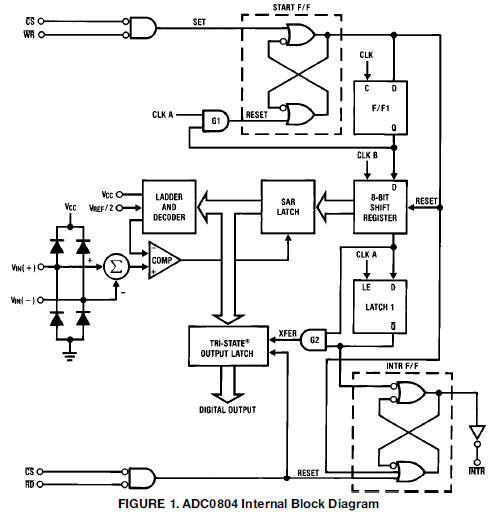

ADC0833和ADC0804系列IOAD轉換器連接到微處理器的ISN8048的技術概述

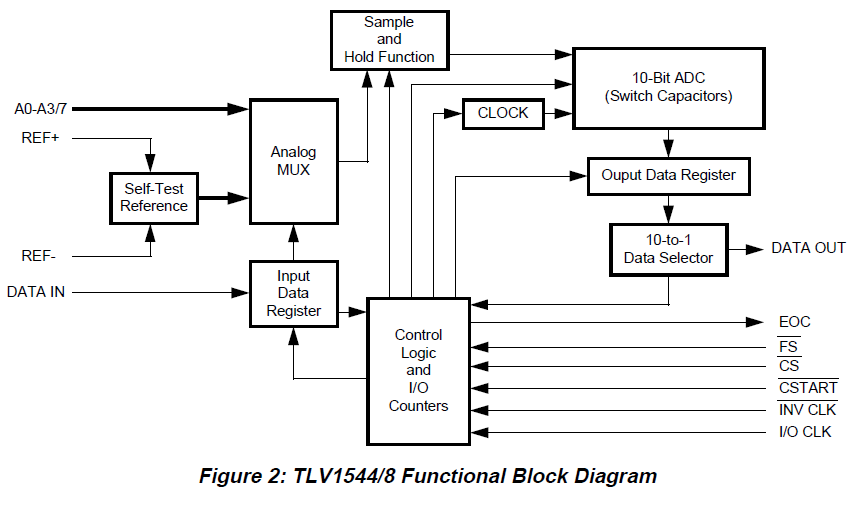

如何將MSOP8EVM與模數轉換器的EVM接口連接到MSP430系列處理器的方法

如何將ADS8361模數轉換器連接到TMS470處理器端口的方法詳細概述

將AD轉換器連接到DSP和MCU的軟硬件要求詳細概述

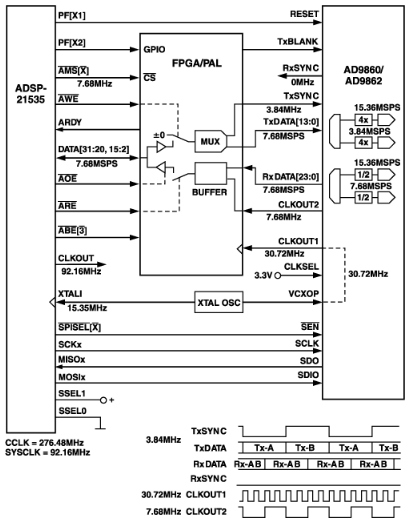

EE-162:通過外部存儲器總線將ADSP-BF535 Blackfin處理器連接到高速轉換器(如AD9860/2上的轉換器)

PC串行端口驅動器12位A/D轉換器

將Blackfin DSP連接到無線應用的高速轉換器

了解連接到串行轉換器-I的原理

了解連接到串行轉換器-I的原理

評論