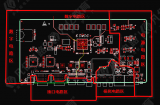

一、pcb布局

1 一般布局PCB,我們會遵循“先大后小,先難后易”的布置原則,也就是說我們一般先去布局重要單元電路,以及核心器件,比如MCU最小系統、高頻高速模塊電路,這些都可以理解為重要單元電路;

2 布局中需要參考原理圖框圖,可以先把原理圖中各個單元電路先布局好,到時候整體在進行拼湊,當然拼抽的時候,要考慮電路信號的主提走向;

3 布局應盡量滿足以下要求:總的連線盡可能短,關鍵信號線最短;高電壓、大電流信號與小電流,低電壓的弱信號完全分開;模擬信號與數字信號分開;高頻信號與低頻信號分開;高頻元器件的間隔要充分。

4 去耦電容的布局要盡可能靠近IC的電源管腳,并且保證電源與地之間形成的回路最短,當然為了達到去耦最佳效果,電源與地需經過去耦電容兩端,然后再連接到IC電源和地兩端;

5 對于一些需要過靜電測試的產品,其器件放置盡量離板邊緣距離大于3.5mm;如果板子空間有限,可以在離板邊緣大于0.45mm出打過孔到地;

6 在完成板子性能的基礎下,布局中就需要考慮美觀,對于相同結構的電路部分,盡可能采用“對稱式“布局,總體布局可以按照”均勻分布,重心平衡,版面美觀“的標準;

7 對于發熱器件,比如MOS管,可以采取加散熱片的形式,給予散熱;

二、pcb布線

1 地走線線徑》電源走線線徑》信號走線線徑,對于1盎司銅厚的板子,我們會預計1mm走線寬度能走1A電流

2 對于信號線走線,我們一般會優先走模擬小信號、高速信號、高頻信號、時鐘信號;其次再走數字信號;

3 晶振周圍盡量禁空,尤其其底部禁止走線;且應遠離板上的電源部分,以防止電源和時鐘相互干擾;

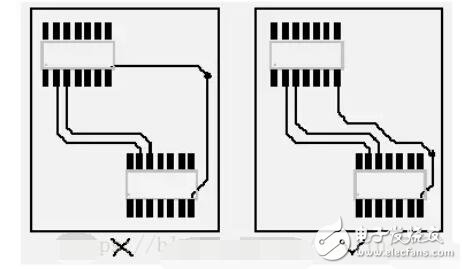

4 避免直角走線 、銳角走線,因為直角、銳角走線會使得傳輸線的線寬產生變化,造成其阻抗的不連續。如果進行直角走線其拐角可以等效為傳輸線上的容性負載,減緩上升時間,在高速、高頻中就變得尤為明顯,而且其造成的阻抗不連續,還會增加信號的反射;其直角尖端還為產生EMI;

5 對于模擬信號和數字信號應盡量分塊布線,不宜交叉或混在一起,對于其模擬地和數字地也應用磁珠或者0R電阻進行隔離;

6 地線回路環路保持最小,即信號線與其回路構成的環面積要盡可能小,環面積越小,對外的輻射越少,接收外界的干擾也越小。 對于top層和bottom層敷地的時候,需要仔細查看,有些信號地是否被信號線分割,造成地回路過遠,此時應該在分割處打過孔,保證其地回路盡可能小;

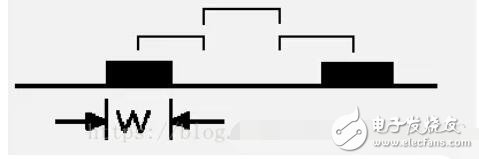

7 為了減少線間串擾,應保證線間距足夠大,當線中心間距不少于3倍線寬時,則可保持70%的電場不互相干擾,稱為3W規則。如要達到98%的電場不互相干擾,可使用10W的間距 ;

8 信號線的長度避免為所關心頻率的四分之一波長的整數倍,否則此信號線會產生諧振,諧振時信號線會產生較強的輻射干擾;

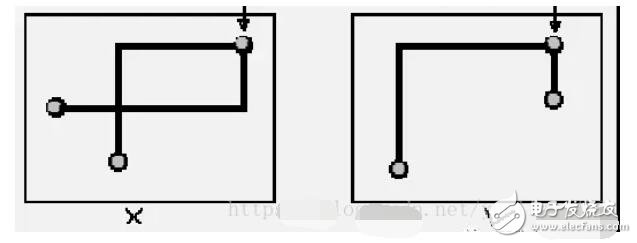

9 信號走線禁止走成環形,其環形容易形成環形天線,產生較強的輻射干擾;

10 對于天線ANT端走線應盡量短而直,其阻抗也應通過 si9000 去計算,保證其線阻為50歐姆(一般天線端口走線為50歐姆);

11 敷銅時,對其焊盤引腳應采用十字焊盤,不宜采用實心焊盤敷銅,這樣在生產時候,器件容易立碑。

-

pcb

+關注

關注

4362文章

23464瀏覽量

408669 -

布線

+關注

關注

9文章

797瀏覽量

85042

發布評論請先 登錄

時源芯微 PCB 布線規則詳解

高層數層疊結構PCB的布線策略

Altium Designer中PCB設計規則設置

12條PCB設計規則

pcb規則及布線

pcb規則及布線

評論