FPGA 的基本結構包括可編程輸入輸出單元,可配置邏輯塊,數字時鐘管理模塊,嵌入式塊RAM,布線資源,內嵌專用硬核,底層內嵌功能單元。由于FPGA具有布線資源豐富,可重復編程和集成度高,投資較低的特點,在數字電路設計領域得到了廣泛的應用。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21985瀏覽量

615087 -

cpu

+關注

關注

68文章

11051瀏覽量

216239 -

通信

+關注

關注

18文章

6184瀏覽量

137467

發布評論請先 登錄

相關推薦

熱點推薦

史上最全:主板上常見的接口信號定義與分類詳解

cpu與外部設備、存儲器的連接和數據交換都需要通過接口設備來實現,前者被稱為I/O接口,而后者則被稱為存儲器

發表于 11-01 18:44

?2.3w次閱讀

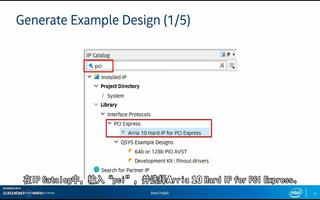

CPU數字通信接口和FPGA進行數據通信設計實現

,主要用在南橋和EC之間通信(想想當年設計的筆記本還是挺虐的~),EC控制的矩陣鍵盤等通過LPC發送給南橋。目前我應用的比較多的是和FT CPU之間進行通信,這方面用的比較少就不過多介

發表于 08-19 16:32

基于串行接口信號調制/解調的通信方案研究

串行接口是單片機與外部設備的主要通信接口之一,串行通信在數據傳輸中占有重要的地位。針對單片機串行接口信號的楨格式,設計并

發表于 09-05 10:26

?22次下載

異步串行通信接口電路的VHDL語言設計

摘要:提出了1種基于CPLD、EPLD或FPGA等可編程邏輯器件的異步串行通信接口電路的設計方法。該方法簡單快捷。易于實現。而且可以作為

發表于 04-30 09:58

?46次下載

Camera Link接口的異步FIFO設計與實現

介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到

發表于 07-28 16:08

?32次下載

異步收發通信端口(UART)的FPGA實現

文章介紹了一種在現場可編程門陣列(FPGA)上實現UART 的方法。首先闡述了UART 異步串行通信原理,然后介紹了實現UART

發表于 08-06 16:24

?55次下載

異步FIFO在FPGA與DSP通信中的應用解析

摘要 利用異步FIFO實現FPGA與DSP進行數據通信的方案。FPGA在寫時鐘的控制下將數據寫入FIFO,再與DSP進行握手后,DSP

發表于 10-30 11:48

?2次下載

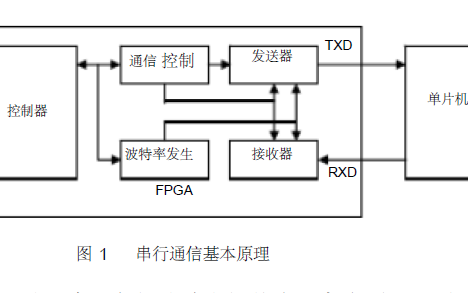

單片機與FPGA異步串行通信的實現方法

介紹了單片機與FPGA 異步串行通信的實現方法,給出了系統結構原理框圖及其部分VHDL 程序,并定義了發送器和接收器的端口信號。

發表于 09-29 16:20

?8次下載

FPGA與單片機實現串行通信的資料詳細說明

介紹了單片機與FPGA 異步串行通信的實現方法,給出了系統結構原理框圖及其部分VHDL 程序,并定義了發送器和接收器的端口信號。

發表于 03-02 13:52

?15次下載

龍迅HDMI接口信號轉換的應用案例

Lontium龍迅MIPI/LVDS接口信號轉換器有著多種接口格式,芯片功能包括Transmitter、Receiver、Switch、Splitter、Repeater、Matrix/Crosspoint、Converter

CPU與FPGA通過異步接口信號實現通信

CPU與FPGA通過異步接口信號實現通信

評論