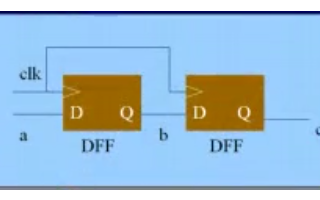

阻塞賦值即賦值沒完成,后邊的語句將無法執(zhí)行,非阻塞剛好與其相反,即賦值完不完成并不阻礙后續(xù)程序的執(zhí)行,所以我們常說非阻塞賦值的對象并未立馬得到新值,如果從時序來看,被賦值對象會比賦值對象差一個時鐘周期。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614616 -

時序

+關注

關注

5文章

397瀏覽量

37806

發(fā)布評論請先 登錄

相關推薦

熱點推薦

Verilog語言中阻塞和非阻塞賦值的不同

來源:《Verilog數(shù)字系統(tǒng)設計(夏宇聞)》 阻塞和非阻塞賦值的語言結構是Verilog 語言中最難理解概念之一。甚至有些很有經(jīng)驗的Verilog 設計工程師也不能完全正確地理解:何

在testbench中如何使用阻塞賦值和非阻塞賦值

本文詳細闡述了在一個testbench中,應該如何使用阻塞賦值與非阻塞賦值。首先說結論,建議在testbench中,對時鐘信號(包括分頻時鐘)使用阻塞賦值,對其他同步信號使用

Verilog阻塞和非阻塞原理分析

Verilog阻塞和非阻塞原理分析在Verilog語言最難弄明白的結構中“非阻塞賦值”要算一個。甚至是一些很有經(jīng)驗的工程師也不完全明白“

發(fā)表于 11-23 12:02

Java非阻塞通信研究

本文針對Java NIO 的特性做出分析與闡述,對網(wǎng)絡應用中阻塞通信與非阻塞通信、NIO的非阻塞工作機制以及網(wǎng)絡通信中非

發(fā)表于 08-10 10:15

?18次下載

verilog中阻塞賦值和非阻塞賦值

阻塞和非阻塞語句作為verilog HDL語言的最大難點之一,一直困擾著FPGA設計者,即使是一個頗富經(jīng)驗的設計工程師,也很容易在這個點上犯下一些不必要的錯誤。

發(fā)表于 03-15 10:57

?7085次閱讀

FPGA學習系列:5.阻塞賦值與非阻塞賦值

設計背景: 阻塞 (=)和非阻塞(=)一直是在我們FPGA中討論的問題,資深的學者都是討論的是賦值應該發(fā)生在上升下降沿還是在哪里,我們在仿真中看的可能是上升下降是準確的,但是在時間電路

FPGA的視頻教程之Verilog中阻塞與非阻塞的詳細資料說明

本文檔的主要內容詳細介紹的是FPGA的視頻教程之Verilog中阻塞與非阻塞的詳細資料說明。

發(fā)表于 03-26 17:16

?2次下載

簡述Verilog HDL中阻塞語句和非阻塞語句的區(qū)別

? 在Verilog中有兩種類型的賦值語句:阻塞賦值語句(“=”)和非阻塞賦值語句(“=”)。正確地使用這兩種賦值語句對于Verilog的設計和仿真非常重要。 Verilog語言中講的阻塞

阻塞與非阻塞通信的區(qū)別 阻塞和非阻塞應用場景

阻塞通信(Blocking Communication):當進行阻塞通信時,調用者在發(fā)起一個I/O操作后會被阻塞,直到該操作完成返回才能繼續(xù)執(zhí)行后續(xù)代碼。

數(shù)字設計FPGA應用:阻塞與非阻塞

數(shù)字設計FPGA應用:阻塞與非阻塞

評論