PLD與一般數(shù)字芯片不同的是:PLD內(nèi)部的數(shù)字電路可以在出廠后才規(guī)劃決定,有些類型的PLD也允許在規(guī)劃決定后再次進(jìn)行變更、改變,而一般數(shù)字芯片在出廠前就已經(jīng)決定其內(nèi)部電路,無(wú)法在出廠后再次改變,事實(shí)上一般的模擬芯片、混訊芯片也都一樣,都是在出廠后就無(wú)法再對(duì)其內(nèi)部電路進(jìn)行調(diào)修。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21982瀏覽量

614562 -

PLD

+關(guān)注

關(guān)注

6文章

230瀏覽量

60030 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1637瀏覽量

81638

發(fā)布評(píng)論請(qǐng)先 登錄

基于可編程邏輯器件和VHDL語(yǔ)言實(shí)現(xiàn)算術(shù)邏輯單元的設(shè)計(jì)

Xilinx可編程邏輯器件的高級(jí)應(yīng)用與設(shè)計(jì)技巧絕版教程

可編程邏輯器件

可編程邏輯器件發(fā)展歷史

PLD可編程邏輯器件

什么是PLD(可編程邏輯器件)

可編程邏輯器件FPGA/CPLD結(jié)構(gòu)與應(yīng)用

基于FPGA進(jìn)行可編程邏輯設(shè)計(jì)

現(xiàn)場(chǎng)可編程邏輯門(mén)陣列器件 FPGA原理及應(yīng)用設(shè)計(jì)

可編程邏輯器件與FPGA的發(fā)展(1)

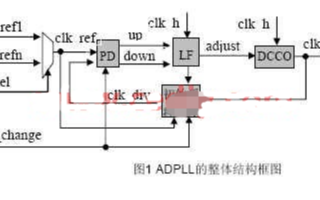

基于可編輯邏輯器件實(shí)現(xiàn)ADPLL的應(yīng)用設(shè)計(jì)

FPGA CPLD可編程邏輯器件的在系統(tǒng)配置方法

FPGA教程:可編輯邏輯器件基礎(chǔ)

FPGA教程:可編輯邏輯器件基礎(chǔ)

評(píng)論