傳統(tǒng)的模擬鎖相環(huán)(APLL)有較短的鎖定時(shí)間,可以保證參考時(shí)鐘源和輸出時(shí)鐘的穩(wěn)態(tài)相差。但其中心頻點(diǎn)受VCO的限制而范圍較小,環(huán)路帶寬較寬;當(dāng)參考源出現(xiàn)瞬斷或者參考時(shí)鐘源切換時(shí),VCO輸出時(shí)鐘頻率會(huì)出現(xiàn)較大的相位瞬變。

隨著數(shù)字電路技術(shù)的發(fā)展,特別FPGA技術(shù)的普遍應(yīng)用,采用FPGA實(shí)現(xiàn)全數(shù)字鎖相環(huán)(ADPLL)的應(yīng)用越來越多。ADPLL設(shè)計(jì)簡(jiǎn)單、應(yīng)用方便。本文介紹一種采用FPGA實(shí)現(xiàn)的ADPLL,該ADPLL用于產(chǎn)生SDH設(shè)備的外同步輸出時(shí)鐘。該鎖相環(huán)具備傳統(tǒng)的APLL的俘獲時(shí)間短、有穩(wěn)定的相差的優(yōu)點(diǎn),同時(shí)也具備DPLL的中心頻點(diǎn)可編程調(diào)整、能夠?qū)崿F(xiàn)平滑源切換的優(yōu)點(diǎn)。

1、體結(jié)構(gòu)及基本工作原理

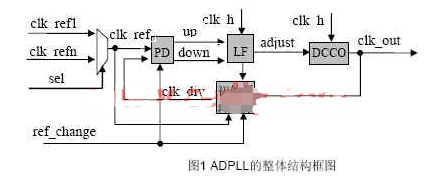

外同步輸出時(shí)鐘產(chǎn)生的整體結(jié)構(gòu)框圖如下圖1所示:

圖1 ADPLL的整體結(jié)構(gòu)框圖

方案的主體部分為一個(gè)ADPLL。ADPLL和傳統(tǒng)的PLL一樣,環(huán)路主要由鑒相器(PD)、濾波器(LF)、數(shù)字控制時(shí)鐘輸出(DCCO)3部分組成。PD將參考時(shí)鐘clk_ref和clk_div(由clk_out進(jìn)行N分頻得到,環(huán)路鎖定后頻率和clk_ref一致)進(jìn)行相差鑒別,輸出up或者down信號(hào)指示時(shí)鐘相位的超前、滯后關(guān)系。LF模塊將up和down,用高速時(shí)鐘clk_h進(jìn)行相差計(jì)數(shù),并采用數(shù)字濾波算法,給出相位調(diào)整指示adjust。DCCO模塊,由高速時(shí)鐘clk_h在相位調(diào)整指示adjust的作用下進(jìn)行受控分頻得到。環(huán)路通過負(fù)反饋調(diào)整,實(shí)現(xiàn)輸出時(shí)鐘clk_out和clk_ref的同步。

ADPLL工作的高速時(shí)鐘(即圖1中的clk_h)采用SDH設(shè)備的系統(tǒng)時(shí)鐘155.52MHz,輸出的外同步時(shí)鐘clk_out頻率為2.048MHz,DCCO模塊采用受控小數(shù)分頻設(shè)計(jì)。外同步時(shí)鐘根據(jù)用戶需要可以從多路參考源中任選1路,由參考源選擇模塊實(shí)現(xiàn)。設(shè)計(jì)中,所有參考源的時(shí)鐘頻率都分頻到100Hz進(jìn)行鑒相,即clk_ref和clk_div的頻率都為100Hz。

2、 全數(shù)字鎖相環(huán)路的詳細(xì)設(shè)計(jì)實(shí)現(xiàn)

輸入的各路參考源的相差是不確定的,當(dāng)參考源切換時(shí),選擇后的信號(hào)clk_ref必然會(huì)出現(xiàn)相位的突變;這種相位的突變最大可能達(dá)半個(gè)clk_ref周期,即源切換后瞬間,clk_ref和clk_div的相差最大可能達(dá)±5ms。源切換產(chǎn)生的相位跳變,在APLL中會(huì)導(dǎo)致壓控電壓突變,導(dǎo)致輸出時(shí)鐘的頻率突變,無法實(shí)現(xiàn)平滑源切換。而在DPLL中,可以通過調(diào)整濾波算法,逐步改變壓控電壓,保證輸出時(shí)鐘頻率的緩慢變化。

這里設(shè)計(jì)的ADPLL,我們通過2個(gè)方面來保證平滑源切換環(huán)路:1、負(fù)反饋時(shí)鐘采用初始受控分頻設(shè)計(jì),當(dāng)參考源切換時(shí),通過受控分頻保證了clk_ref和clk_div的初始相差小于半個(gè)clk_out時(shí)鐘周期。2、通過環(huán)路濾波算法,逐步改變adjust的調(diào)整頻率,保證源切換時(shí)輸出時(shí)鐘頻率平滑變化。

2.1 初始受控分頻設(shè)計(jì)

當(dāng)源切換時(shí),輸出至少1個(gè)clk_div時(shí)鐘周期的1電平信號(hào)ref_change,指示當(dāng)前參考源進(jìn)行了源切換。當(dāng)ref_change為1時(shí),clk_div信號(hào)重新由clk_out在clk_ref的受控下分頻得到;同時(shí),屏蔽掉該鑒相周期的up和down輸出,避免adjust出現(xiàn)誤調(diào)整。

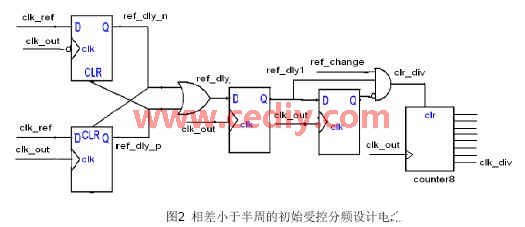

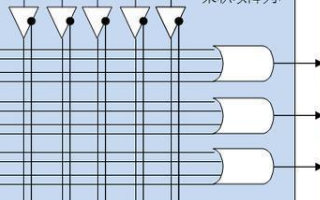

采用如下圖2的電路邏輯設(shè)計(jì)初始受控分頻,可以保證初始分頻后,clk_div和clk_ref的相差小于半個(gè)clk_out時(shí)鐘周期,即小于244ns。清零信號(hào)clr_div只在ref_change為1時(shí)使能;鎖相環(huán)正常跟蹤情況下,clk_div為自由分頻得到。

圖2 相差小于半周的初始受控分頻設(shè)計(jì)電路

在參考源切換后,clk_out與clk_ref的初始相位關(guān)系有2種可能:clk_out超前或者滯后。當(dāng)clk_out相位超前時(shí),則上圖中ref_dly_n將clk_ref的沿踩中;當(dāng)clk_out相位滯后時(shí),則上圖中ref_dly_p將clk_ref的沿踩中;2種情況,最后都在下同一個(gè)clk_out周期取clk_ref的上沿,然后進(jìn)行受控分頻。按此設(shè)計(jì)的受控分頻設(shè)計(jì),可以保證初始受控分頻后,產(chǎn)生的clk_div和clk_ref的相差總在半個(gè)clk_out周期以內(nèi)。

2.2 環(huán)路濾波設(shè)計(jì)

這里,我們完全采用數(shù)字電路邏輯實(shí)現(xiàn)環(huán)路濾波算法。環(huán)路濾波設(shè)計(jì)中,相位調(diào)整指示adjust由頻率調(diào)整控制adjust_f和相位調(diào)整控制adjust_p兩部分共同組成。

頻率調(diào)整控制adjust_f的產(chǎn)生:

1)、鎖相環(huán)開始工作時(shí)的初始值adjust_f[0]=0。

2)、根據(jù)當(dāng)前鑒相周期鑒出的相差phase[n](用155M時(shí)鐘對(duì)up和down進(jìn)行計(jì)數(shù)綜合得到),和上一個(gè)鑒相周期鑒出的相差phase[n-1]進(jìn)行比較:

當(dāng)(phase[n]-phase[n-1]) 》 1,則adjust_f[n]=adjust_f[n-1] – 1;

當(dāng)(phase[n]-phase[n-1]) 《 -1,則adjust_f[n]=adjust_f[n-1] + 1;

其他情況,adjust_f[n]=adjust_f[n-1],保持不變。

3)、adjust_f[n]的范圍控制在±127以內(nèi)。

4)、當(dāng)|phase[n]-phase[n-1]|大于1000,即相差突跳了6.4us時(shí),說明參考源可能出現(xiàn)突跳,此時(shí)輸出源抖動(dòng)指示,重新進(jìn)行初始受控分頻。

頻率調(diào)整控制,保證了輸出時(shí)鐘頻率和參考源頻率的一致。該濾波設(shè)計(jì),保證了adjust_f的緩慢變化;參考源切換后,adjust[n]的調(diào)整也是在之前基礎(chǔ)上逐步變化,這可靠的保證了輸出時(shí)鐘頻率的平滑。

相位調(diào)整控制adjust_p的產(chǎn)生:

1)、根據(jù)當(dāng)前鑒相周期鑒出的相差phase[n]來給出相位調(diào)整控制:

phase[n] 》 0,則adjust_p[n] = -1;

phase[n] 《 0,則adjust_p[n] = 1;

其他情況,則adjust_p[n] = 0;

相位調(diào)整控制的作用下,可靠的保證了鎖定情況下的穩(wěn)態(tài)相差小于1個(gè)clk_h時(shí)鐘周期。

adjust[n] = adjust_f[n] + adjust_p[n]。在環(huán)路正常跟蹤或者源切換的過程中,|adjust[n] - adjust[n-1]|總是會(huì)小于2,即輸出時(shí)鐘的頻率突變小,保證了輸出時(shí)鐘clk_out的頻率穩(wěn)定。

adjust》0時(shí),DCCO需要進(jìn)行相位正調(diào)整;而當(dāng)adjust 《 0時(shí),DCCO需要進(jìn)行相位負(fù)調(diào)整。需要調(diào)整的adjust,在下個(gè)鑒相周期(100Hz)中平均分配。由于adjust調(diào)整值最大不超過128,所以adjust的調(diào)整頻率最大為12.8KHz。

2.3 DCCO的設(shè)計(jì)實(shí)現(xiàn)

155.52M為2.048M的75.9375倍,為非整數(shù)倍;同時(shí)DCCO受adjust的調(diào)整控制。即clk_out需要由clk_h進(jìn)行小數(shù)受控分頻得到。

注意到2.048M的76倍頻為155.648M,和155.52M相差128K。所以2.048M可以這樣產(chǎn)生:155.52M時(shí)鐘在76分頻的過程中,每128K時(shí)鐘周期固定進(jìn)行相位負(fù)調(diào)整1次。顯然,固定相位調(diào)整頻度遠(yuǎn)大于 adjust相位調(diào)整頻度。

小數(shù)分頻的固定相位調(diào)整設(shè)計(jì)和adjust的相位調(diào)整控制可以綜合起來考慮:1、每128K頻率的固定相位負(fù)調(diào)整,和adjust的正調(diào)整控制信號(hào)都在128K時(shí)鐘信號(hào)的上沿位置進(jìn)行。當(dāng)需要進(jìn)行一次正相位調(diào)整時(shí),直接去掉1次固定負(fù)調(diào)整即可達(dá)到目的。2、而adjust的負(fù)調(diào)整在128K時(shí)鐘信號(hào)的下沿位置進(jìn)行,和固定負(fù)調(diào)整錯(cuò)開,避免某一個(gè)clk_out周期進(jìn)行了2次負(fù)調(diào)整。

經(jīng)過這種綜合調(diào)整控制后,任意一個(gè)clk_out時(shí)鐘周期,可能為clk_h的76分頻、或者75分頻。這樣,產(chǎn)生的clk_out時(shí)鐘的cycle-cycle固有抖動(dòng)為1個(gè)clk_h周期(p-p峰峰值),即6.4ns。

3、 實(shí)際應(yīng)用及鎖相環(huán)特性測(cè)試

3.1 設(shè)計(jì)實(shí)例

由于該ADPLL同時(shí)具有平滑源切換及穩(wěn)態(tài)相差的優(yōu)點(diǎn),我們?cè)陂_發(fā)SDH設(shè)備的時(shí)鐘板時(shí),直接采用該方案設(shè)計(jì)實(shí)現(xiàn)2.048M外同步輸出時(shí)鐘。該設(shè)計(jì)中,F(xiàn)PGA芯片采用了Altera公司提供的EP1C4F400芯片,該ADPLL部分總邏輯資源占用約300個(gè)LE(1個(gè)LE包括1個(gè)4輸入的查找表和1個(gè)D觸發(fā)器)。

3.2 環(huán)路特性分析及實(shí)際測(cè)試結(jié)論

1)、頻率俘獲帶

也稱為牽引范圍。即clk_h和clk_ref頻率偏差到環(huán)路無法鎖定時(shí)的最大值。

根據(jù)環(huán)路濾波設(shè)計(jì),每100Hz最大調(diào)整128個(gè)clk_h周期,即鎖相環(huán)路最大可調(diào)整的頻率為100Hz×128×6.4ns= 81.92ppm。即環(huán)路的牽引范圍為±81.92ppm。

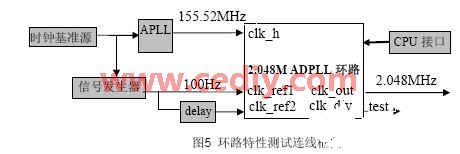

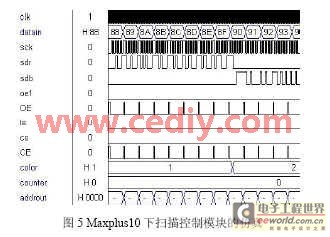

采用如下圖5所示的方法進(jìn)行牽引范圍的測(cè)試:

SDH設(shè)備的系統(tǒng)155.52M時(shí)鐘,通過一路APLL和時(shí)鐘基準(zhǔn)源保持同步。環(huán)路的100Hz時(shí)鐘由信號(hào)發(fā)生器產(chǎn)生。用示波器測(cè)量鎖相環(huán)路的clk_ref1和clk_out的鎖定情況;通過信號(hào)發(fā)生器逐步改變參考時(shí)鐘clk_ref1的頻偏, 觀察能夠鎖定的最大頻偏。測(cè)試得到的牽引范圍為±80ppm左右。

2)、穩(wěn)態(tài)相差

多次復(fù)位鎖相環(huán)路后,用示波器測(cè)量環(huán)路鎖定情況下圖5中的clk_ref1和clk_out時(shí)鐘相差,均在±12ns以內(nèi)。

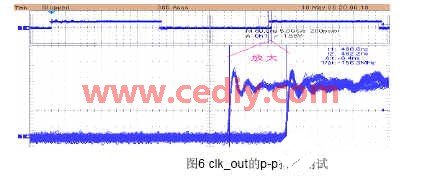

3)、輸出時(shí)鐘的cycle-cycle抖動(dòng)

根據(jù)2.3節(jié)的分析,輸出時(shí)鐘抖動(dòng)的p-p為6.4ns。采用示波器測(cè)試2.048MHz輸出時(shí)鐘,如下圖6所示,抖動(dòng)的峰-峰值就是6.4ns,和分析一致。

圖6 clk_out的p-p抖動(dòng)測(cè)試

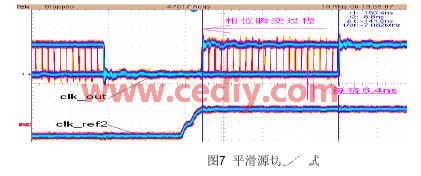

4)、平滑源切換

按圖5,給鎖相環(huán)路提供2路同頻不同相的參考源clk_ref1和clk_ref2。用clk_ref2作觸發(fā)源,示波器設(shè)置為長(zhǎng)余輝和快俘的模式;通過CPU接口將環(huán)路的參考源由clk_ref1更改為clk_ref2。通過示波器可以看到參考源切換過程中clk_out的相位瞬變?nèi)缦聢D7所示:

從圖7中可以看到,源切換過程中相位瞬變的幅度小于半個(gè)2.048M周期,這里為140ns。瞬變過程中,輸出時(shí)鐘和參考源的相差按6.4ns的粒度,逐步調(diào)整,直到最后鎖定。

從上述測(cè)試結(jié)果來看,輸出時(shí)鐘的穩(wěn)態(tài)相差較小,Cycle-cycle抖動(dòng)較小,有較寬的牽引范圍,能夠?qū)崿F(xiàn)平滑源切換,完全滿足SDH設(shè)備外同步輸出時(shí)鐘的要求。

4、 總結(jié)

本文設(shè)計(jì)的全數(shù)字鎖相環(huán)獨(dú)到之處在于:該鎖相環(huán)具備數(shù)字鎖相環(huán)的平滑源切換、牽引范圍可調(diào)等優(yōu)點(diǎn),同時(shí)還具備模擬鎖相環(huán)的快速俘獲和有穩(wěn)態(tài)相差等優(yōu)點(diǎn)。通過實(shí)踐驗(yàn)證,利用該鎖相環(huán)產(chǎn)生的SDH設(shè)備外同步輸出時(shí)鐘,可以很好的實(shí)現(xiàn)平滑源切換,俘獲時(shí)間快,同時(shí)保證了環(huán)路的穩(wěn)態(tài)相差,各項(xiàng)時(shí)鐘指標(biāo)良好。

責(zé)任編輯:gt

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論