簡述FPGA在microsoft azure的應(yīng)用

隨著5G通信技術(shù)的發(fā)展,云計算和邊緣計算業(yè)務(wù)也將快速增長。由于云計算多樣性和邊緣環(huán)境復(fù)雜性的特點,將....

解析IIC專題原理及應(yīng)用篇(一)

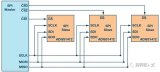

一、操作 1.1、系統(tǒng)的概述 I2C系統(tǒng)使用串行數(shù)據(jù)線(SDA)和串行時鐘線(SCL)進行數(shù)據(jù)傳輸。....

基于RISC-V 架構(gòu)設(shè)計 GD32V 上運行 RT-Thread

GD32VF103 開發(fā)板去年九月份的時候 RT-Thread 的 Andy Chen 組織定做了一....

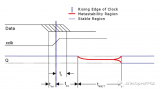

詳解亞穩(wěn)態(tài)的理論以及使用建議

一、介紹 在同步系統(tǒng)中,數(shù)據(jù)始終相對于時鐘具有固定的關(guān)系 當(dāng)該關(guān)系滿足設(shè)備的建立和保持要求時,輸出將....

深度解讀Vivado之Synthesis

在FPGA設(shè)計里,設(shè)計仿真完成RTL代碼設(shè)計后便是交給設(shè)計套件進行綜合及布局布線。在綜合過程里,Vi....

淺談ZYNQ-AXI總線的信號接口要求以及時序關(guān)系

學(xué)習(xí)內(nèi)容 學(xué)習(xí)關(guān)于AXI總線的信號接口的具體要求(包括不同通道之間的關(guān)系,握手機制說明等)和AXI4....

基于SRAM技術(shù)的Xilinx FPGA具有較高的邏輯密度

基于SRAM技術(shù)的Xilinx FPGA具有較高的邏輯密度,消耗較高功率; 基于閃存技術(shù)的Xilin....

圖解說明什么是Flash, SAR, Sigma-Delta型ADC

模數(shù)轉(zhuǎn)換模塊ADC是連接現(xiàn)實世界模擬量和數(shù)字量之間的橋梁,它的轉(zhuǎn)換精度經(jīng)常可以決定一個產(chǎn)品的品質(zhì)。現(xiàn)....

分享一個超級實用的源碼閱讀小技巧

工欲善其事必先利其器; 我發(fā)現(xiàn)函數(shù)調(diào)用圖可以讓我們更加直觀地了解到源碼函數(shù)直接的調(diào)用和層次關(guān)系,提高....

Xilinx全新UltraScale架構(gòu)介紹

1 介紹 Xilinx 全新 16 納米及 20 納米 UltraScale 系列基于首款架構(gòu),不僅....

UART的發(fā)送數(shù)據(jù)模塊及Verilog代碼

代碼注釋有些匆忙,如有錯誤注釋還請批評,僅作參考 UART Uart比較簡單,所以僅對tx作比較詳細....

2020DAC- SDC冠軍作品分享,充分結(jié)合FPGA數(shù)據(jù)流架構(gòu)的優(yōu)勢

如果說上期SkrSkr隊伍的設(shè)計像是德智體美勞全面發(fā)展的“五好學(xué)生”,那么冠軍隊伍的設(shè)計則更像是“不....

結(jié)合STM32單片來講講結(jié)構(gòu)體的運用

摘要:聽說還有好多學(xué)單片機的小伙伴不會用結(jié)構(gòu)體?指針和結(jié)構(gòu)體是學(xué)單片機必須要掌握的,如果你C語言掌握....

教你們一些提高C編程能力的妙招

前言 目前C語言被應(yīng)用得最多的估計就是嵌入式了,在學(xué)校學(xué)習(xí)完C語言,考完等級考試之后,可能就會覺得自....

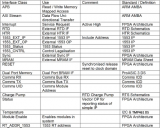

XADC內(nèi)嵌在PS端允許CPU或其他主機連接而不用使用PL端

XADC內(nèi)嵌在PS端,允許CPU或其他主機連接XADC,而不用使用PL端。XADC最大采樣率為1MS....

如何為FPGA編寫可綜合的代碼?

一、Verilog 編碼風(fēng)格 (本文的語法高亮因為瀏覽器的緣故,所以不準(zhǔn)確) 1.1 使用“`inc....

搭建鏈路實現(xiàn)FPGA到PC的數(shù)據(jù)傳輸使用以太網(wǎng)實現(xiàn)信息傳輸

問題情景:為了得到連續(xù)時間內(nèi)ADC采集的數(shù)據(jù),并在PC上對數(shù)據(jù)進行分析,需要搭建鏈路實現(xiàn)FPGA到P....