Verilog狀態(tài)機(jī)+設(shè)計實例

Verilog狀態(tài)機(jī)+設(shè)計實例

在verilog中狀態(tài)機(jī)的一種很常用的邏輯結(jié)構(gòu),學(xué)習(xí)和理解狀態(tài)機(jī)的運行規(guī)律能夠幫助我們更好地書寫代碼....

verilog中函數(shù)和任務(wù)對比

verilog中函數(shù)和任務(wù)對比

在verilog中,函數(shù)和任務(wù)均用來描述共同的代碼段,并且在模式內(nèi)任意位置被調(diào)用,提高代碼效率,讓代....

數(shù)字電路常見邏輯符號

1、與門 (AND) 有兩路輸入信號一路輸出信號,當(dāng)且僅當(dāng)兩個輸入信號均為高電平時,輸出信號為高電平....

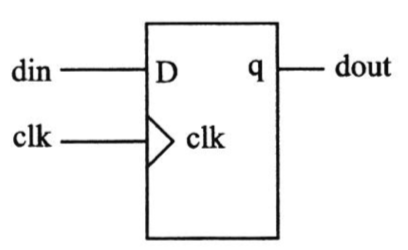

verilog的數(shù)據(jù)類型

verilog的數(shù)據(jù)類型

1、常量 整數(shù) :整數(shù)可以用二進(jìn)制數(shù)b或B,八進(jìn)制o或O,十進(jìn)制d或D,十六進(jìn)制h或H表示,例如:8....

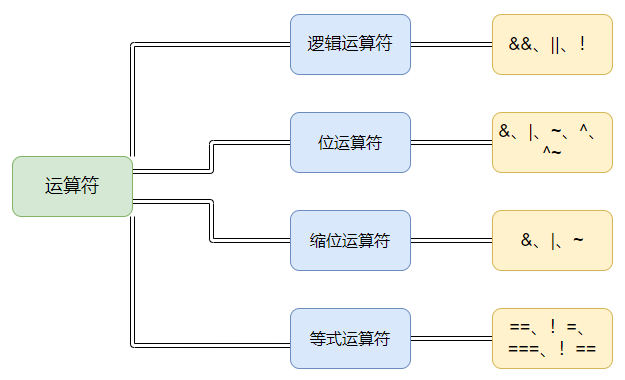

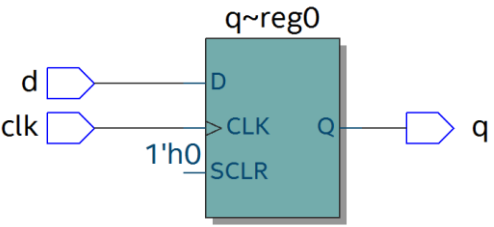

verilog可綜合的語法子集

verilog可綜合的語法子集

可綜合的語法是指硬件能夠?qū)崿F(xiàn)的一些語法,這些語法能夠被EDA工具支持,能夠通過編譯最終生成用于燒錄到....

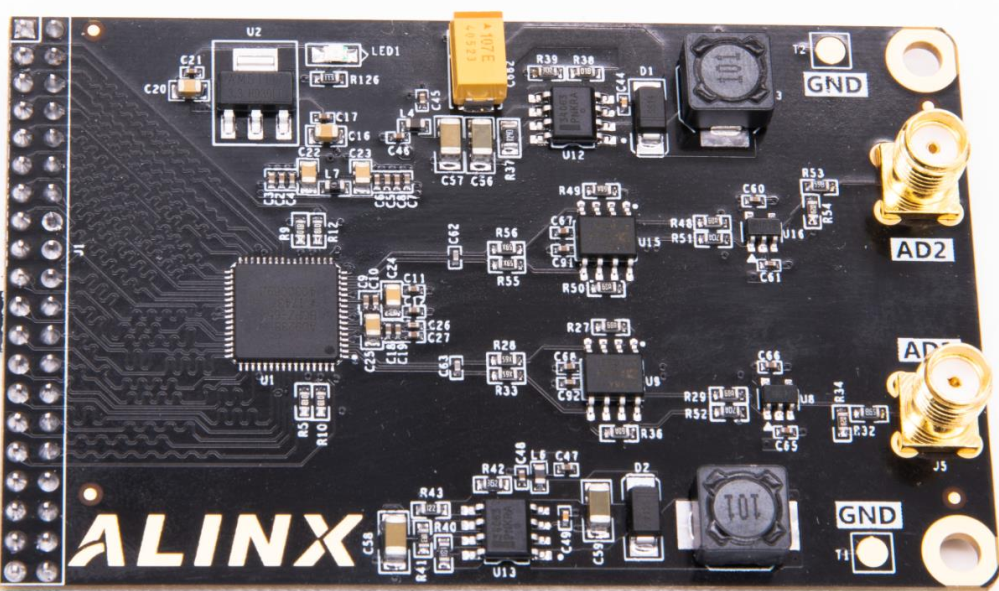

FPGA核心電路

FPGA核心電路

常見的FPGA核心電路可以歸納為五個部分:電源電路、時鐘電路、復(fù)位電路、配置電路和外設(shè)電路。下面將對....

三極管四種工作狀態(tài)對比

三極管四種工作狀態(tài)對比

三極管根據(jù)發(fā)射結(jié)和集電結(jié)的偏置狀態(tài)可以將工作區(qū)域分為四個,分別為截止區(qū)、放大區(qū)、飽和區(qū)、反向放大區(qū)。....