7490是二-五-十進(jìn)制異步計(jì)數(shù)器,你要做八進(jìn)制的就先把7490接成十進(jìn)制的(CP1與Q0接,以CP0做輸入,Q3做輸出就是十進(jìn)制的),然后用異步置數(shù)跳過(guò)一個(gè)狀態(tài)達(dá)到八進(jìn)制計(jì)數(shù).

以從000計(jì)到111為例.先接成加法計(jì)數(shù)狀態(tài),在輸出為1000時(shí)(既Q4為高電平時(shí))把Q4輸出接到R01和R02腳上(即異步置0),此時(shí)當(dāng)計(jì)數(shù)到1000時(shí)則立刻置0,從新從0開(kāi)始計(jì)數(shù).1000的狀態(tài)為瞬態(tài).

狀態(tài)轉(zhuǎn)化圖中是0000到0111是有效狀態(tài),1000是瞬態(tài),跳轉(zhuǎn)從這個(gè)狀態(tài)跳回到0000狀態(tài).

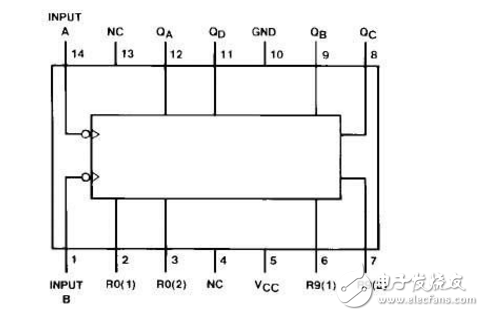

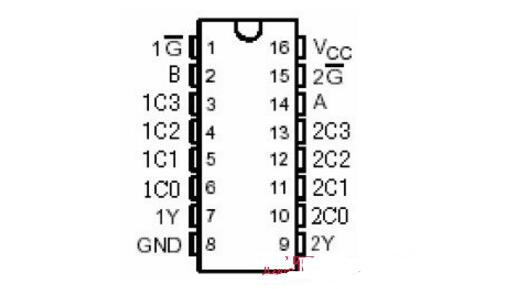

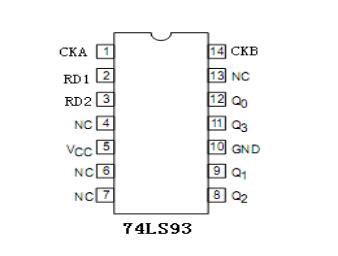

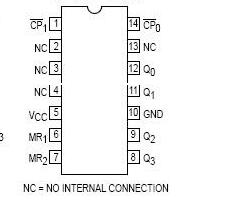

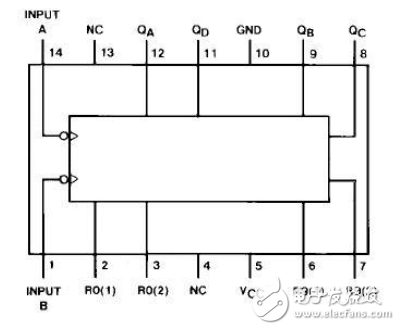

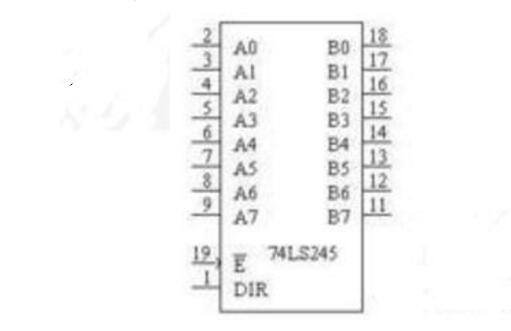

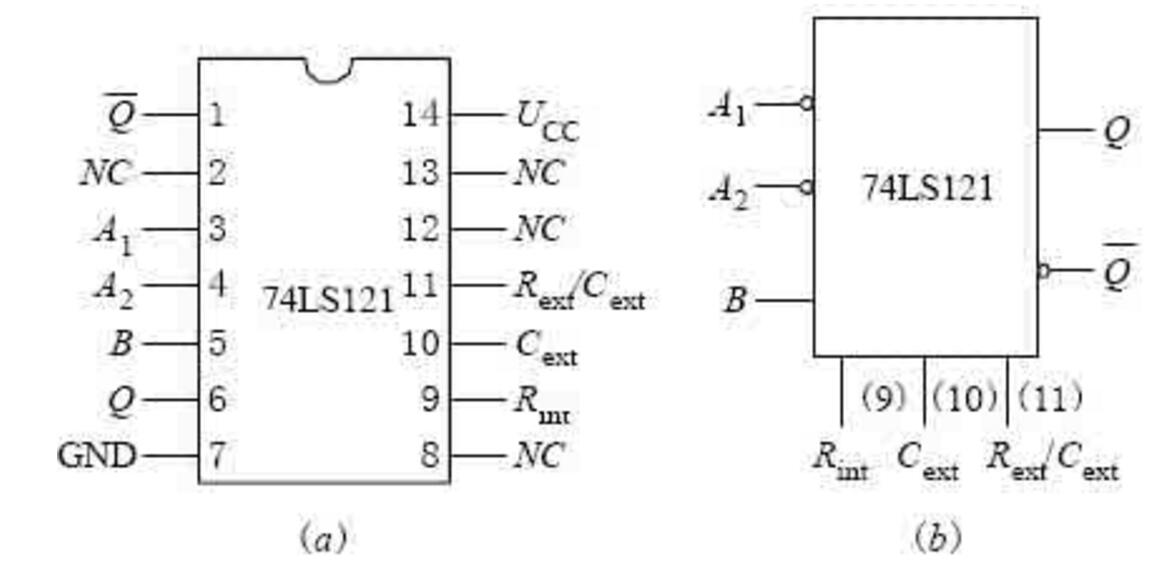

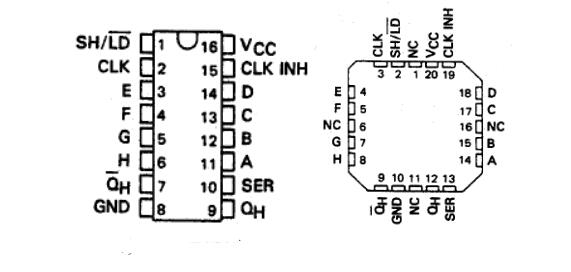

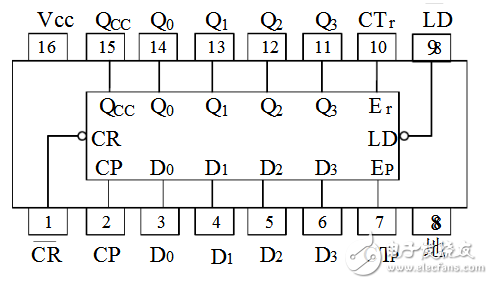

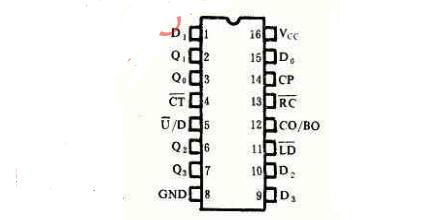

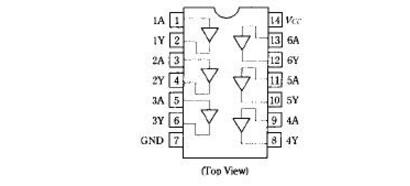

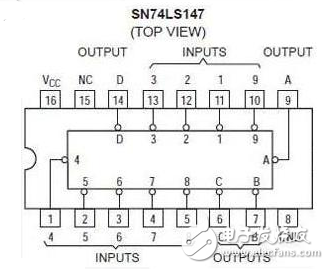

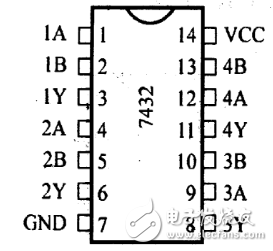

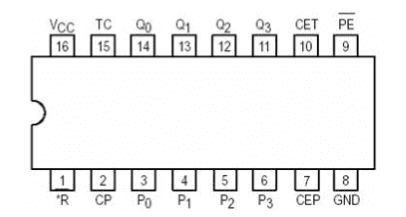

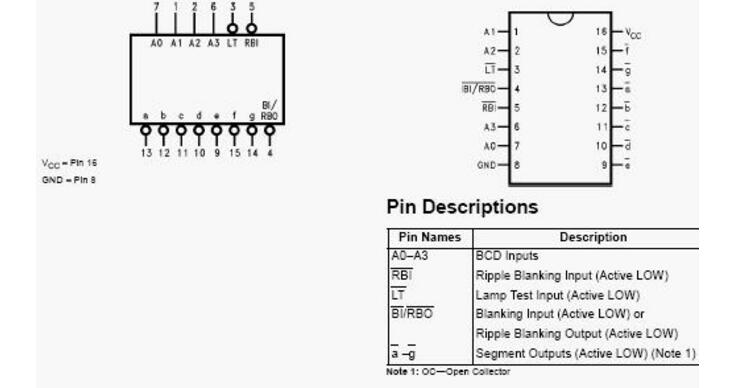

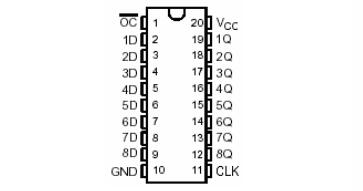

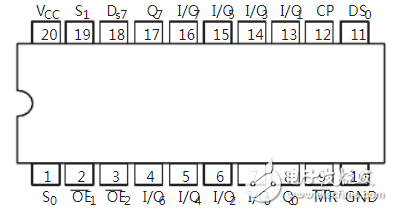

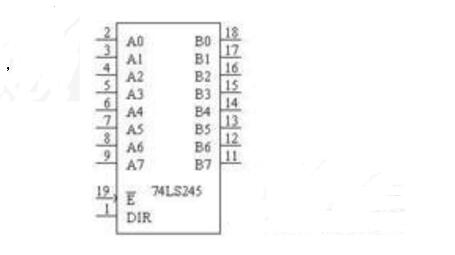

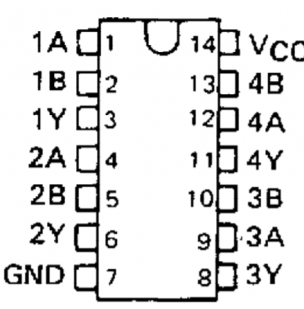

74LS90引腳圖及引腳功能

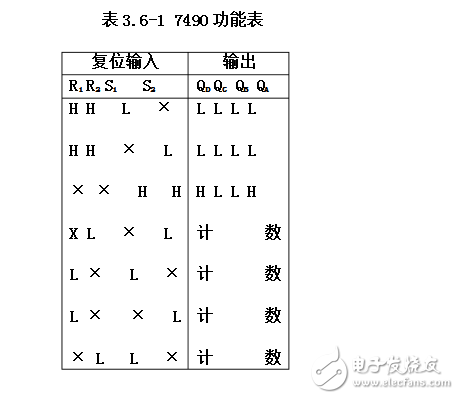

74LS90計(jì)數(shù)器是一種中規(guī)模二一五進(jìn)制計(jì)數(shù)器,管腳引線如圖3.6-1,功能表如表3.6-1所示。

74LS90引腳圖

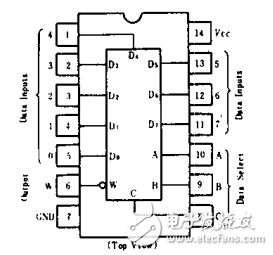

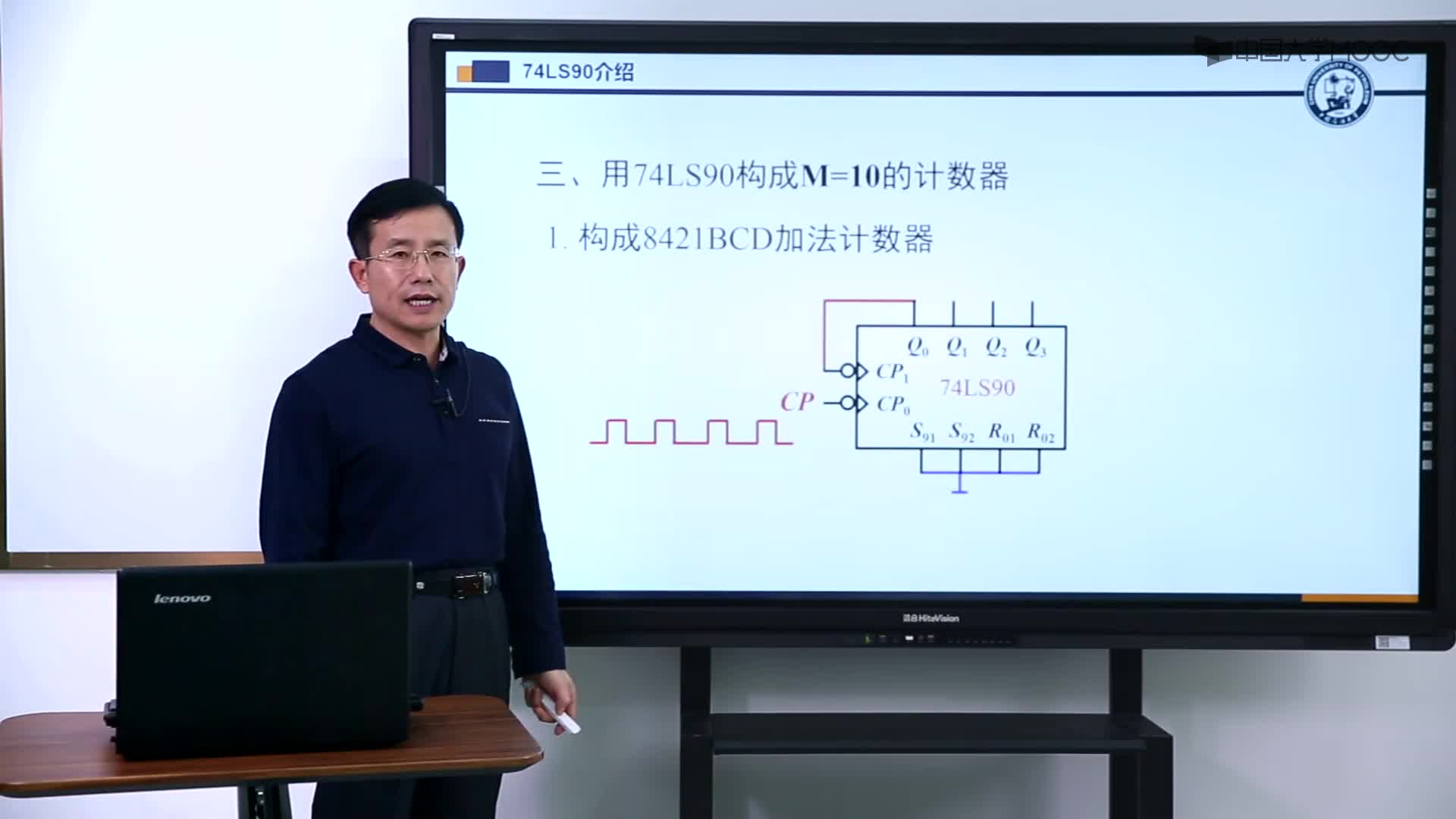

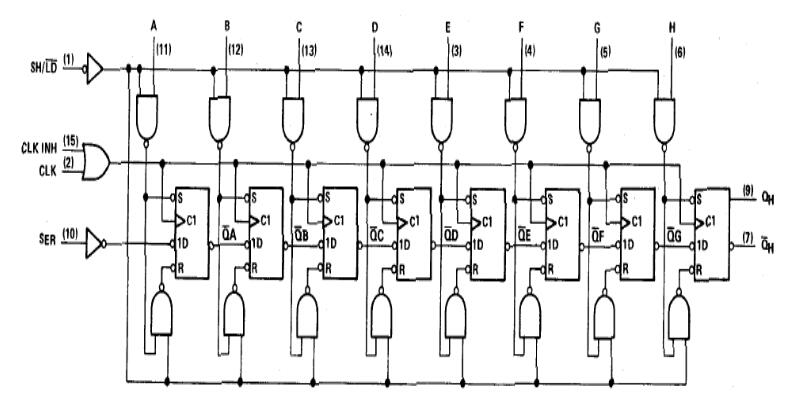

A. 將輸出QA與輸入B相接,構(gòu)成8421BCD碼計(jì)數(shù)器;

B. 將輸出QD與輸入A相接,構(gòu)成5421BCD碼計(jì)數(shù)器;

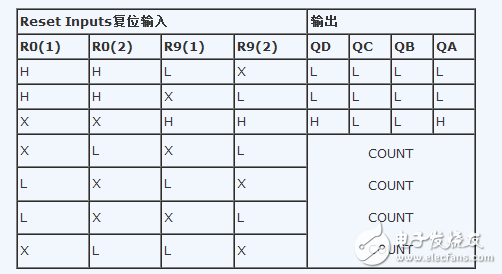

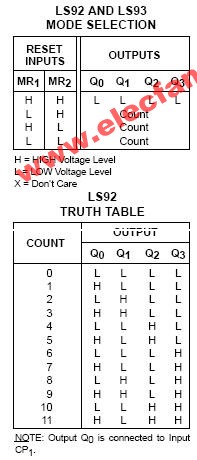

C. 表中H為高電平、L為低電平、×為不定狀態(tài)。

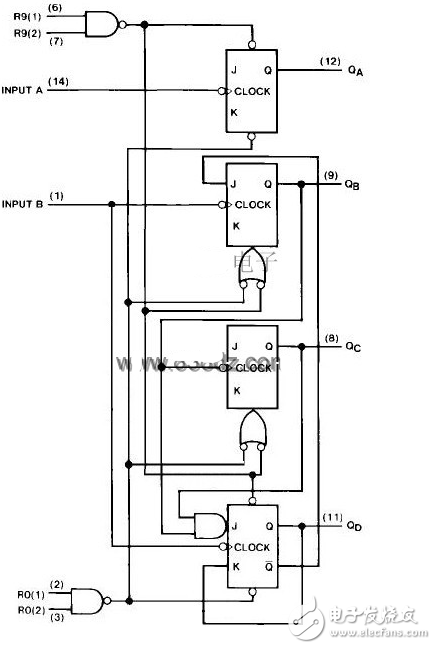

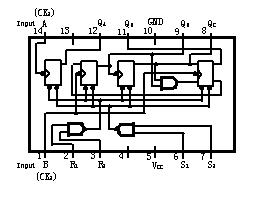

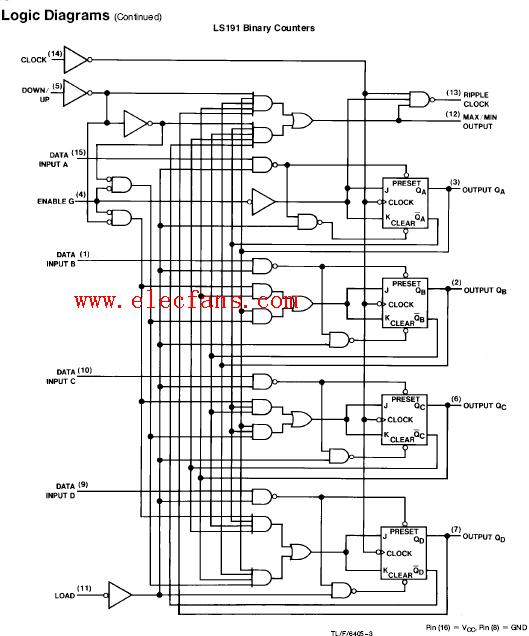

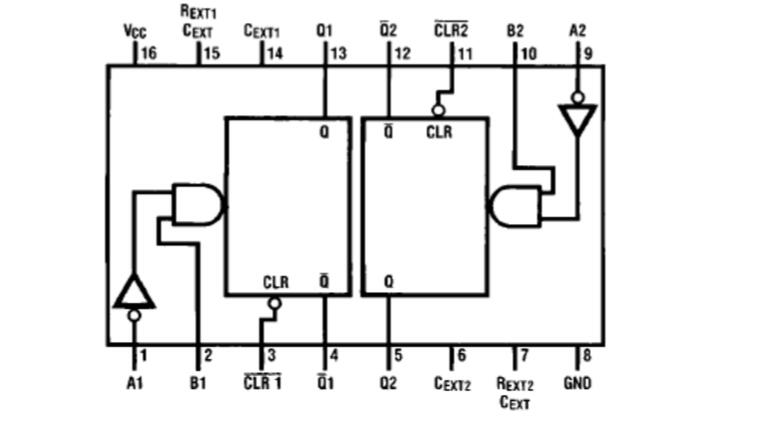

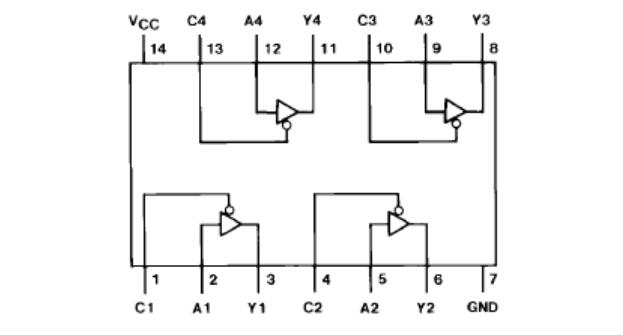

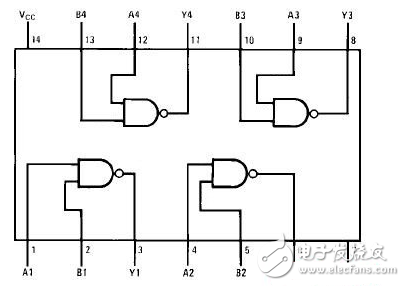

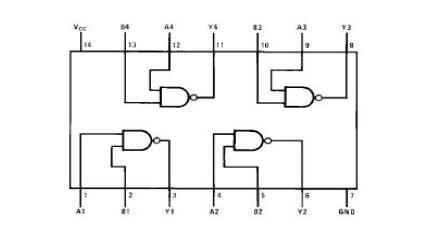

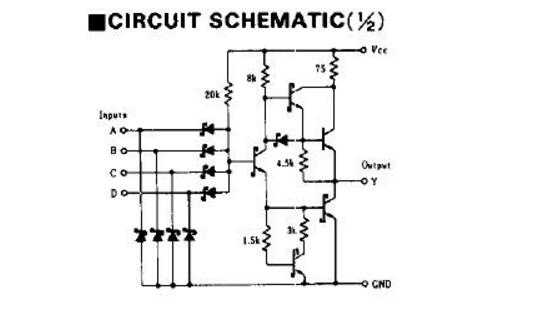

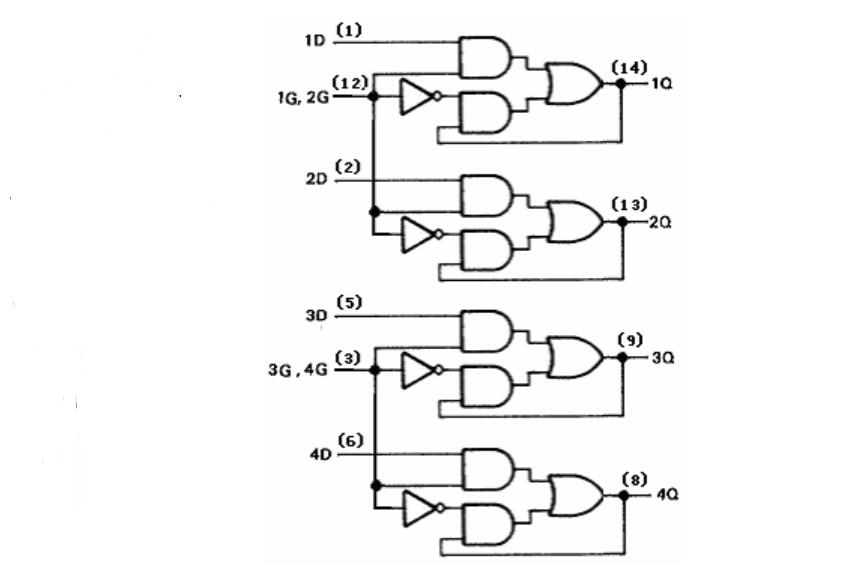

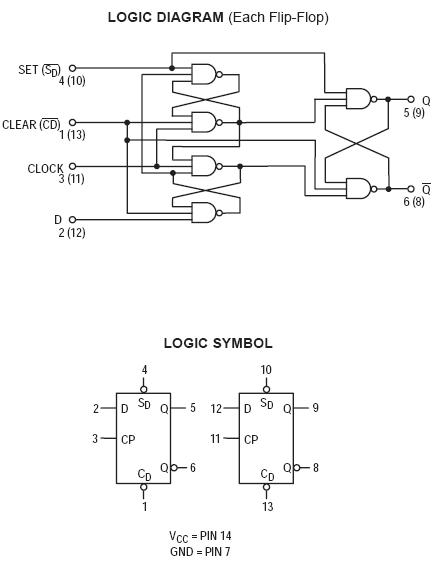

74LS90邏輯電路圖如圖3.6-1所示,它由四個(gè)主從JK觸發(fā)器和一些附加門電路組成,整個(gè)電路可分兩部分,其中FA觸發(fā)器構(gòu)成一位二進(jìn)制計(jì)數(shù)器;FD、FC、FB構(gòu)成異步五進(jìn)制計(jì)數(shù)器,在74LS90計(jì)數(shù)器電路中,設(shè)有專用置“0”端R1、R2和置位(置“9”)端S1、S2。

原理說(shuō)明:本電路是由4 個(gè)主從觸發(fā)器和用作除2 計(jì)數(shù)器及計(jì)數(shù)周期長(zhǎng)度為除5 的3 位2 進(jìn)制計(jì)數(shù)器所用的附加選通所組成。有選通的零復(fù)位和置9 輸入。

為了利用本計(jì)數(shù)器的最大計(jì)數(shù)長(zhǎng)度(十進(jìn)制),可將B 輸入同QA 輸出連接,輸入計(jì)數(shù)脈沖可加到輸入A 上,此時(shí)輸出就如相應(yīng)的功能表上所要求的那樣。

LS90 可以獲得對(duì)稱的十分頻計(jì)數(shù),辦法是將QD 輸出接到A 輸入端,并把輸入計(jì)數(shù)脈沖加到B 輸入端,在QA 輸出端處產(chǎn)生對(duì)稱的十分頻方波。

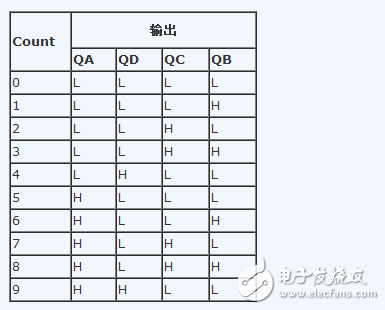

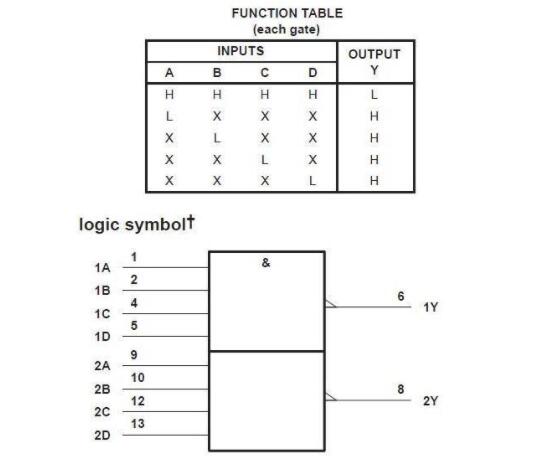

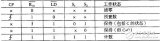

真值表:

H=高電平 L=低電平 ×=不定

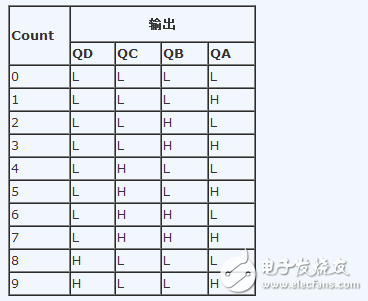

BCD 計(jì)數(shù)順序(注1)

5-2 進(jìn)制計(jì)數(shù)順序(注2)

注1:對(duì)于BCD(十進(jìn))計(jì)數(shù),輸出QA 連到輸入B 計(jì)數(shù)

注2:對(duì)于5-2 進(jìn)制計(jì)數(shù),輸出QD 連到輸入A 計(jì)數(shù)

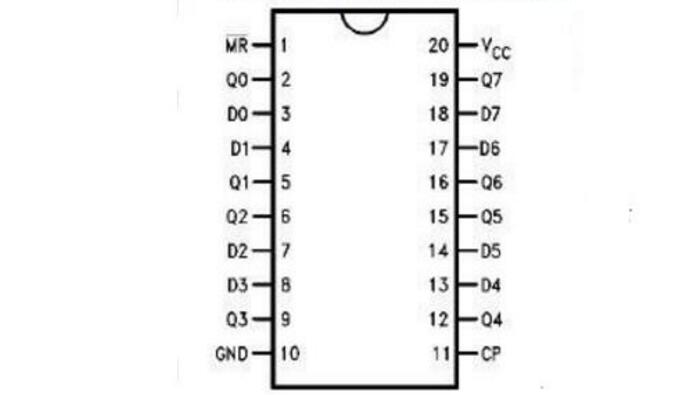

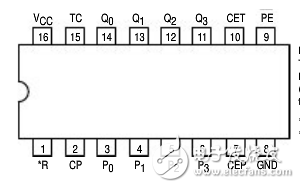

74LS90具有如下的五種基本工作方式:

(1)五分頻:即由FD、FC、和FB組成的異步五進(jìn)制計(jì)數(shù)器工作方式。

(2)十分頻(8421碼):將QA與CK2聯(lián)接,可構(gòu)成8421碼十分頻電路。

(3)六分頻:在十分頻(8421碼)的基礎(chǔ)上,將QB端接R1,QC端接R2。其計(jì)數(shù)順序?yàn)?00~101,當(dāng)?shù)诹鶄€(gè)脈沖作用后,出現(xiàn)狀態(tài)QCQBQA=110,利用QBQC=11反饋到R1和R2的方式使電路置“0”。

(4) 九分頻:QA→R1、QD→R2,構(gòu)成原理同六分頻。

(5)十分頻(5421碼):將五進(jìn)制計(jì)數(shù)器的輸出端QD接二進(jìn)制計(jì)數(shù)器的脈沖輸入端CK1,即可構(gòu)成5421碼十分頻工作方式。

此外,據(jù)功能表可知,構(gòu)成上述五種工作方式時(shí),S1、S2端最少應(yīng)有一端接地;構(gòu)成五分頻和十分頻時(shí),R1、R2端亦必須有一端接地。

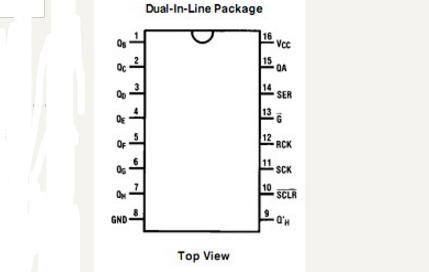

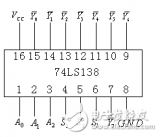

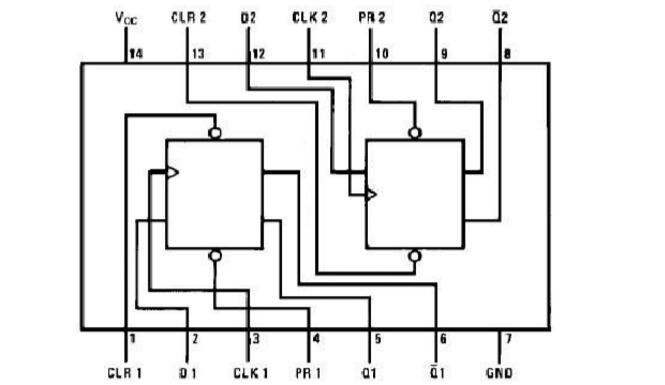

74LS90內(nèi)部邏輯圖

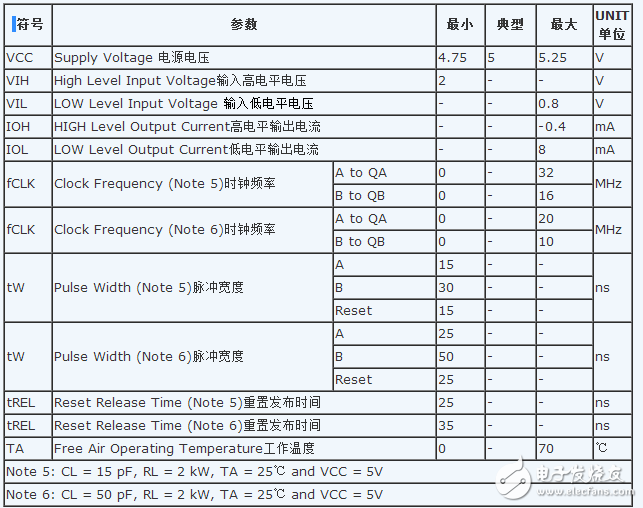

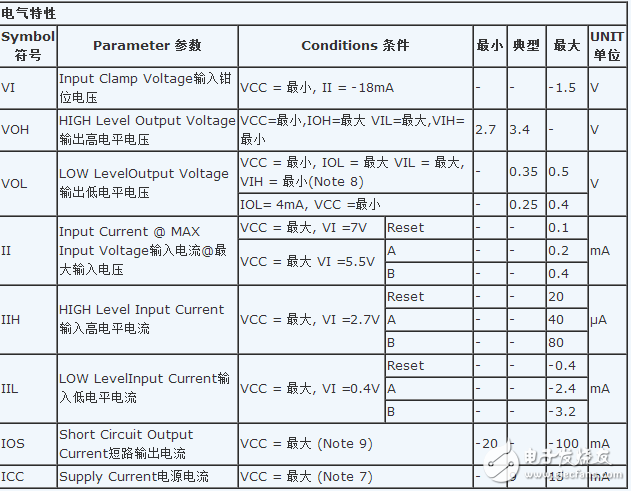

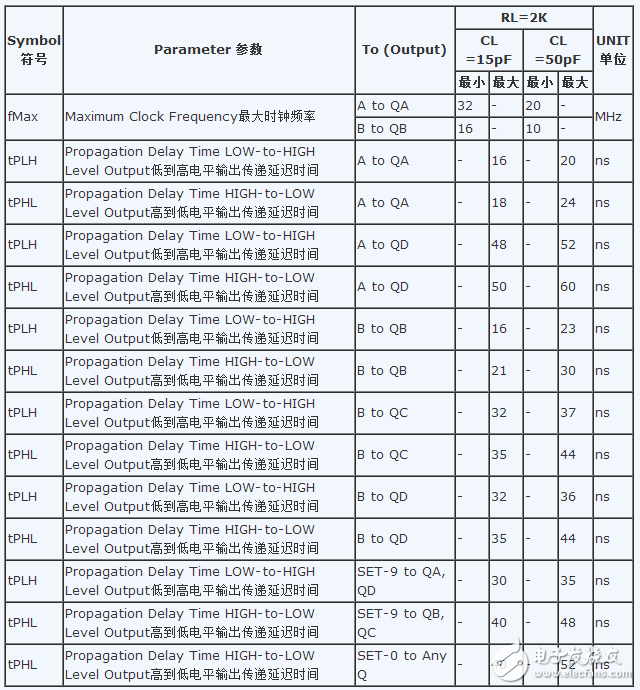

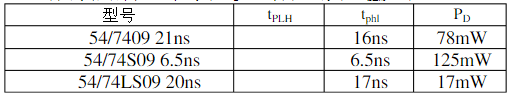

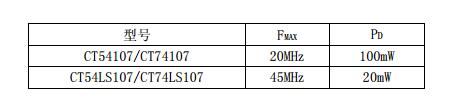

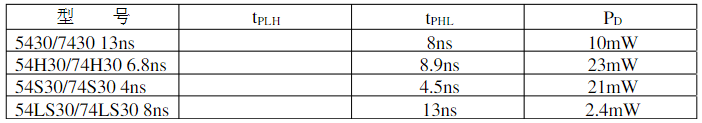

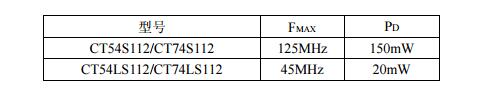

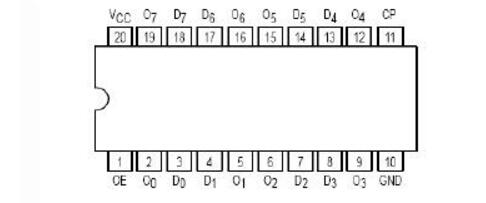

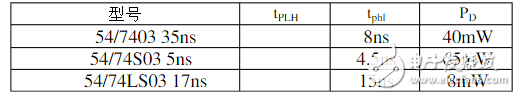

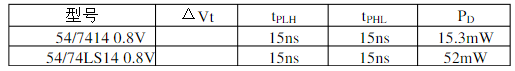

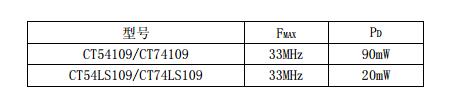

74ls90電性參數(shù)表

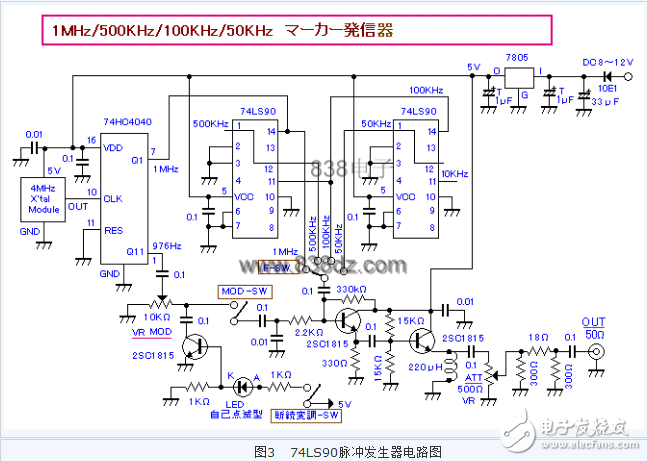

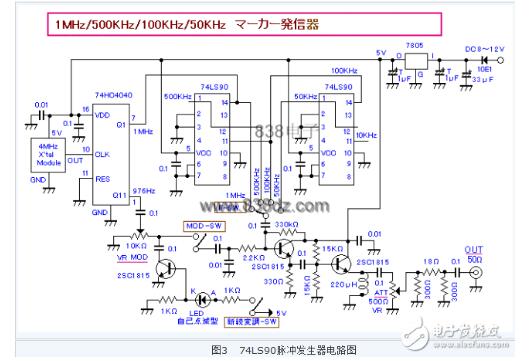

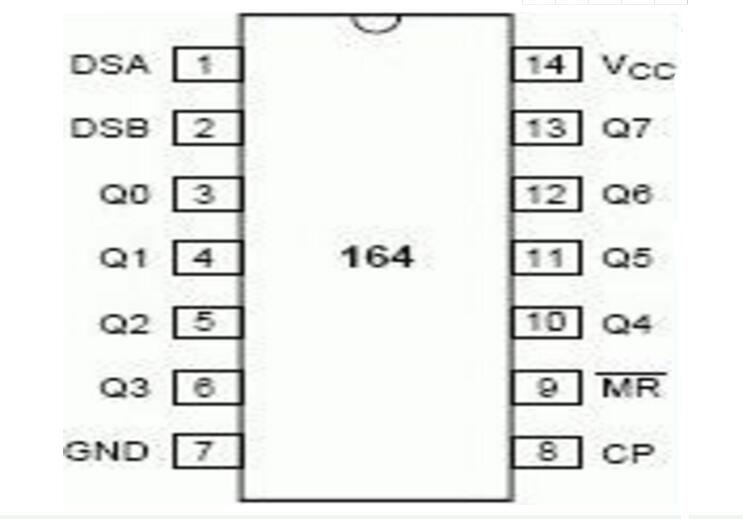

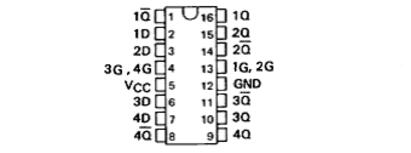

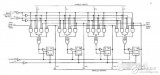

74ls90應(yīng)用電路

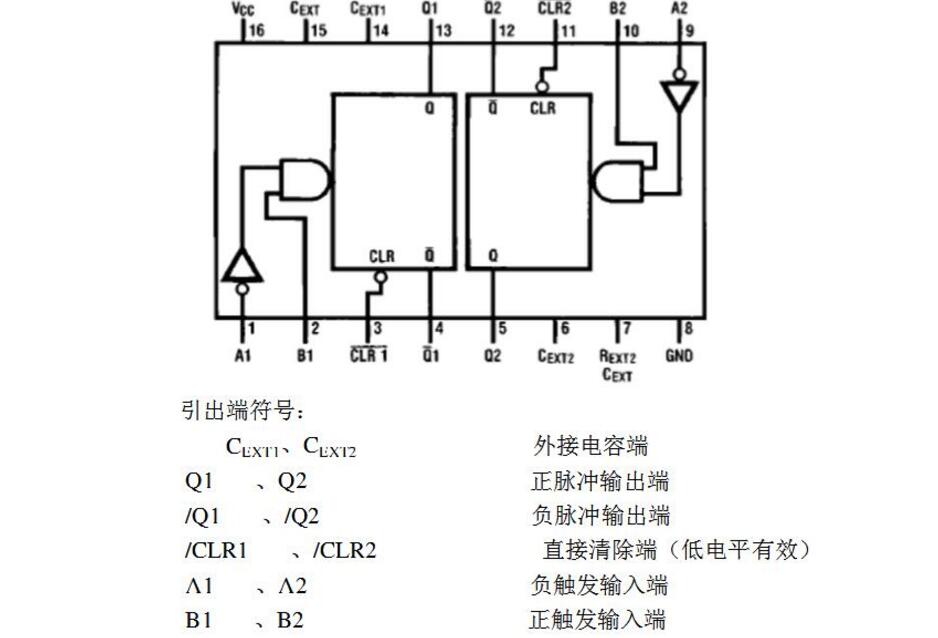

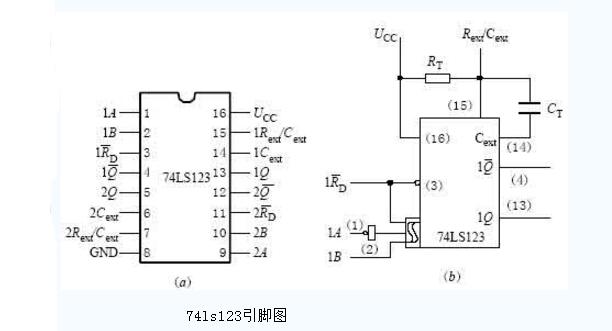

74ls90脈沖發(fā)生器電路

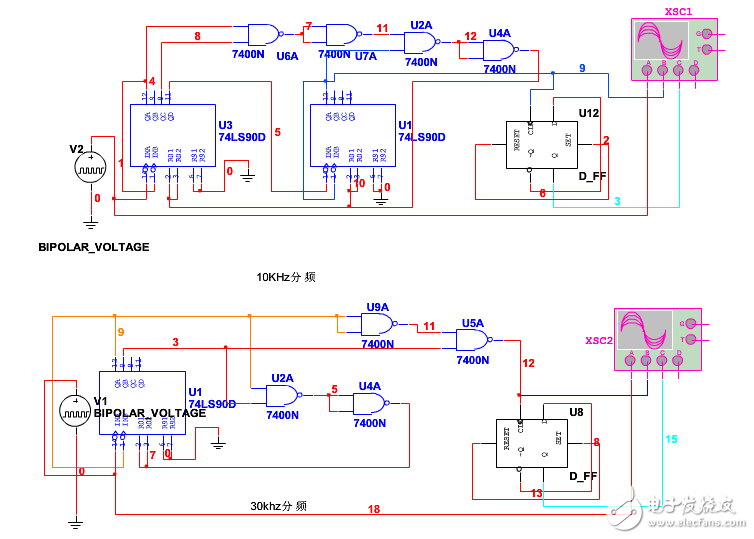

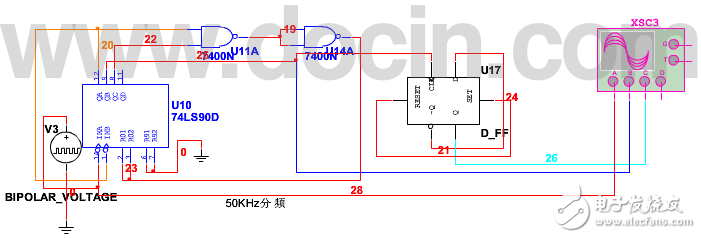

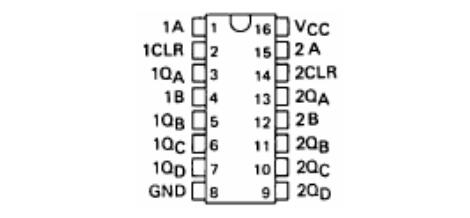

74ls90實(shí)現(xiàn)電路的分頻

輸入信號(hào)為300KHZ 的方波信號(hào)或i 弦波信號(hào),仿真軟件為Multisim10.0.

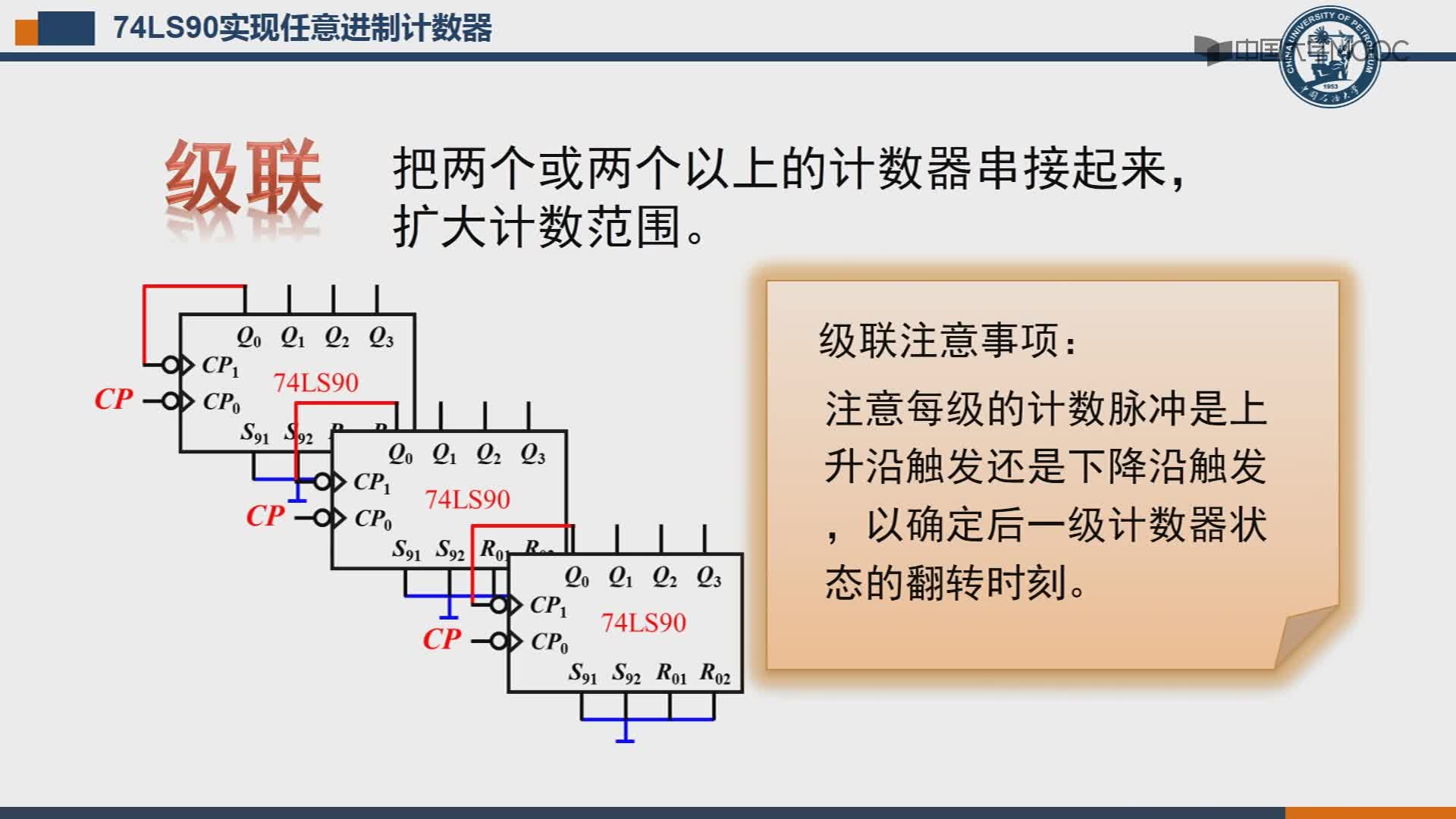

運(yùn)用計(jì)數(shù)器實(shí)現(xiàn)分頻的關(guān)鍵在于明白計(jì)數(shù)后產(chǎn)生的上升沿觸發(fā)信號(hào),觸發(fā)下一個(gè)芯片。R01,R02 為復(fù)位端,由計(jì)數(shù)端控制。R91,R92 始終接地。在送復(fù)位信號(hào)時(shí)要注意信號(hào)同時(shí)到達(dá)兩個(gè)復(fù)位端,復(fù)位信號(hào)傳輸中與、非等門電路都會(huì)延遲信號(hào)到達(dá),所以在這個(gè)過(guò)程中門電路最好一樣。當(dāng)計(jì)數(shù)很大時(shí),可以用多個(gè)741S90 分別計(jì)各個(gè)位的數(shù)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論