一、設計思路

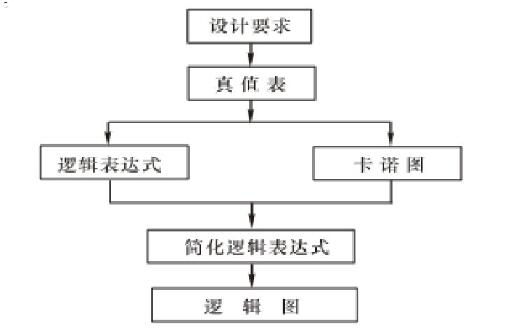

1.使用中、小規模集成電路來設計組合電路是最常見的邏輯電路設計方法。設計組合電路的一般步驟如圖所示。

2.組合邏輯電路的設計

步驟:①根據對邏輯功能要求,列真值表

②由真值表寫出邏輯表達式

③根據要求化簡和變換邏輯函數表達式

④根據要求畫出邏輯圖

⑤芯片選擇,接成實物

⑥分析并比較設計的優劣

設計目標:電路簡單,所用器件最少,可靠性好等

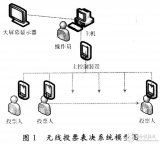

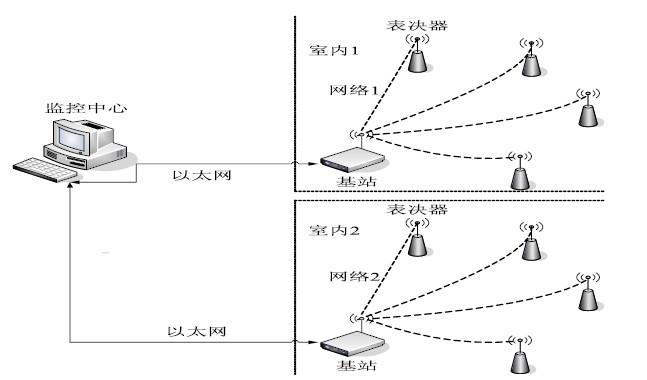

二、三人表決電路設計

要求:設計一個三人表決電路,結果按“少數服從多數”的原則決定。

方法:

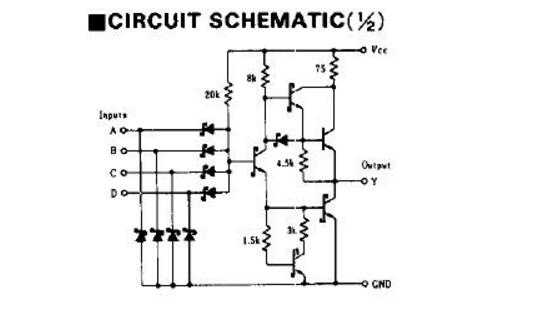

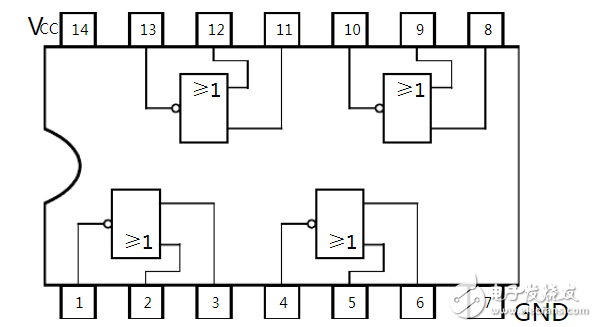

(1):只用74LS00,74LS20實現。

(SSI設計)

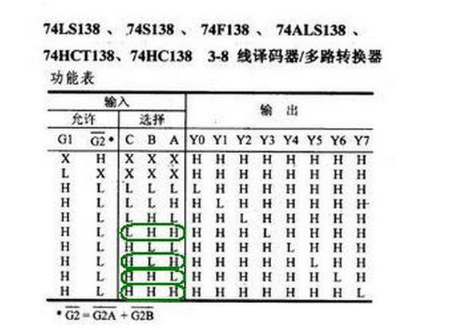

(2):用74LS138和74LS20實現。

(MSI設計)

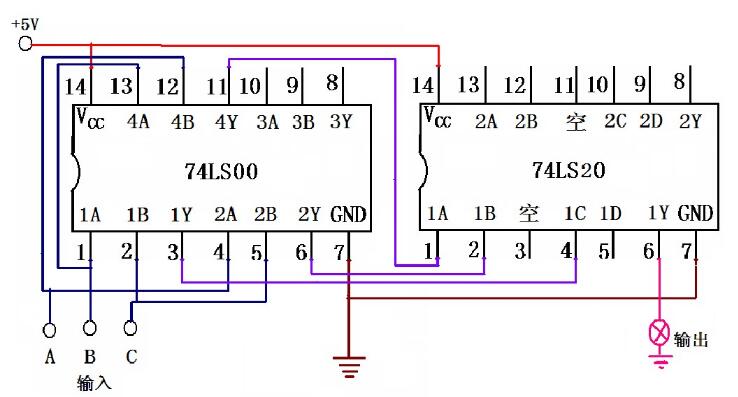

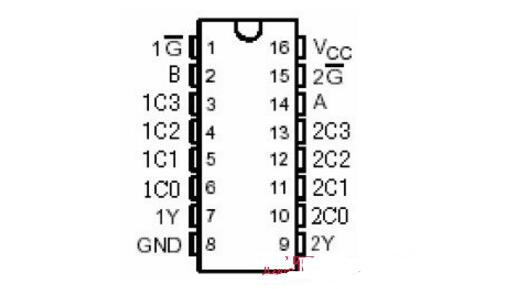

(3):用74LS151或LS153實現。

(MSI設計)

方法一:用SSI設計(用74LS00,74LS20)實現三人表決電路

分析:

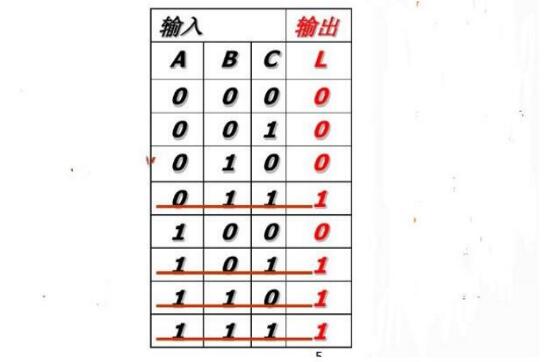

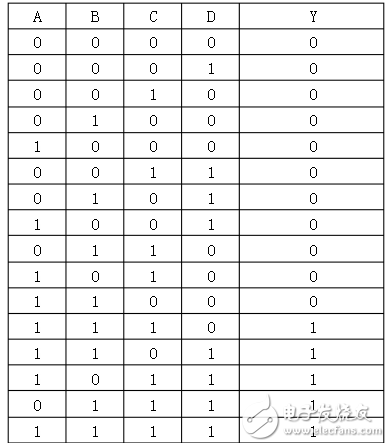

①設A、B、C:三人的意見。

同意為邏輯“1”;不同意為邏輯“0”

L:表決結果。

事件通過為邏輯“1”;沒通過為邏輯“0”

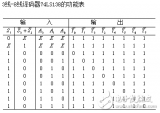

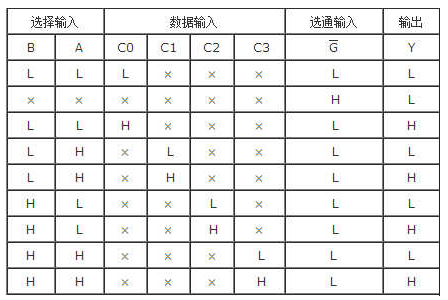

列出真值表如右表所示。

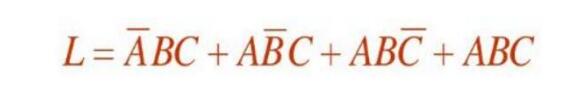

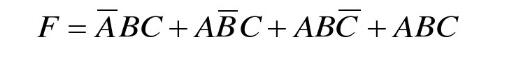

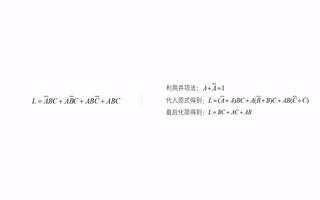

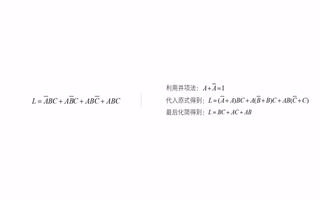

②由真值表寫出邏輯表達式:

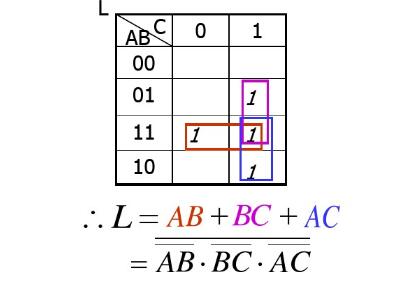

③用卡諾圖進行化簡。

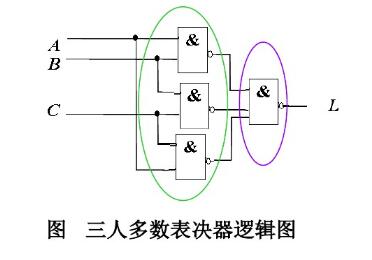

④畫出邏輯圖。

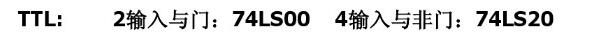

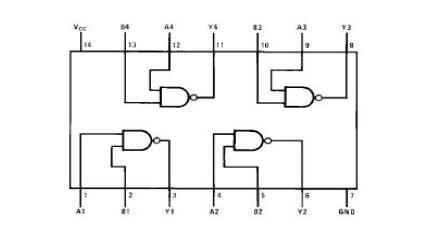

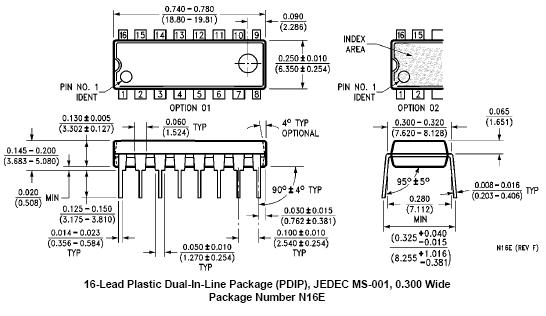

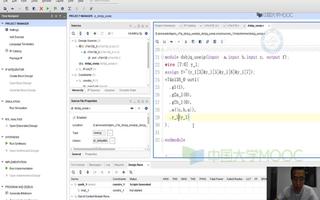

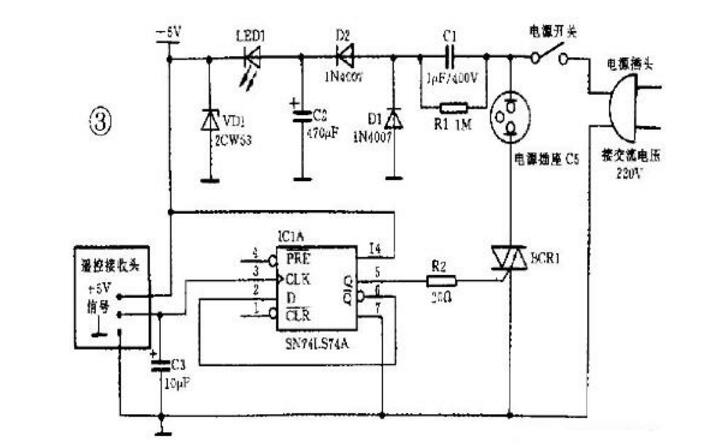

⑤選擇芯片并連接。

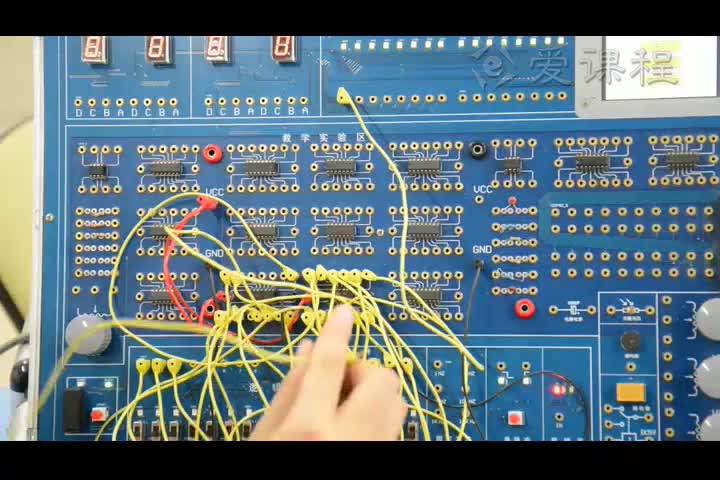

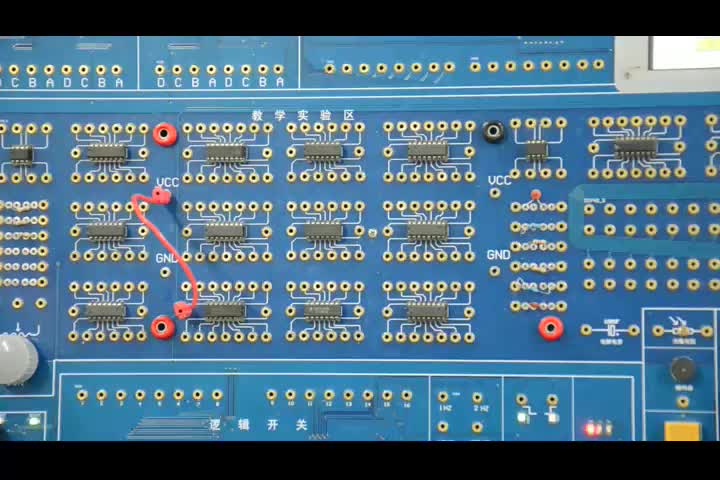

用74LS00和74LS20實物接線如下:

電子發燒友App

電子發燒友App

評論