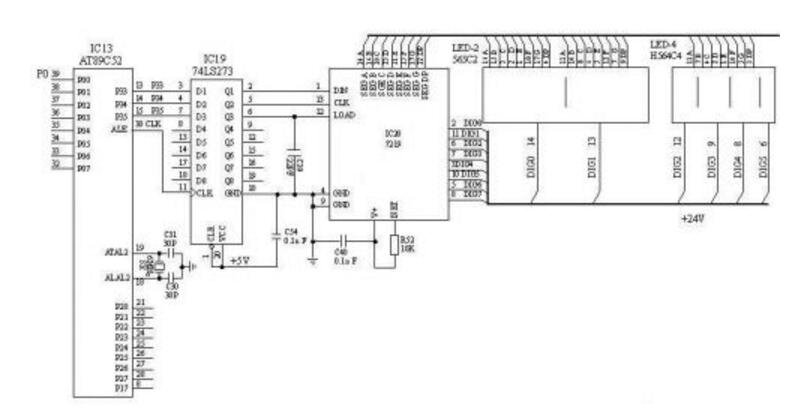

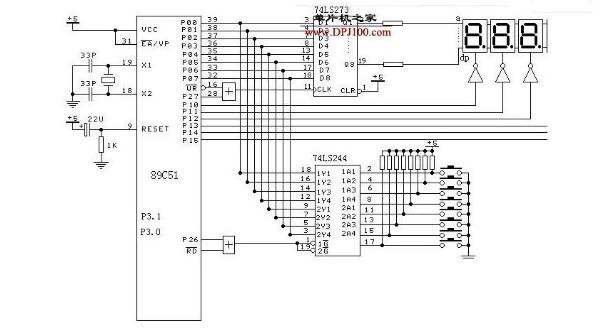

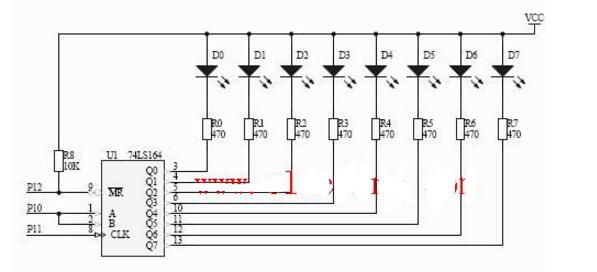

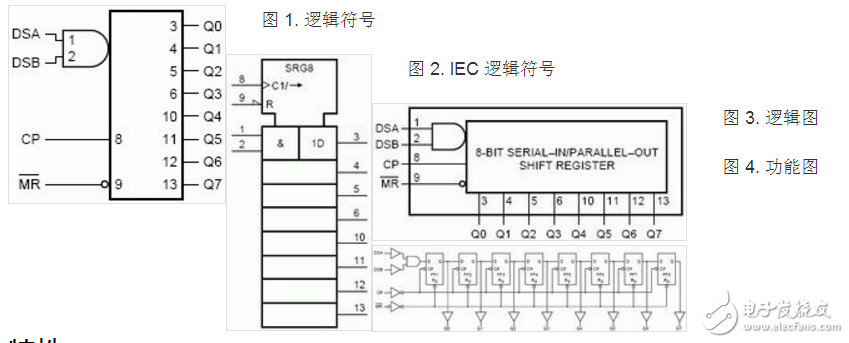

74ls273應(yīng)用電路圖一:串行顯示電路

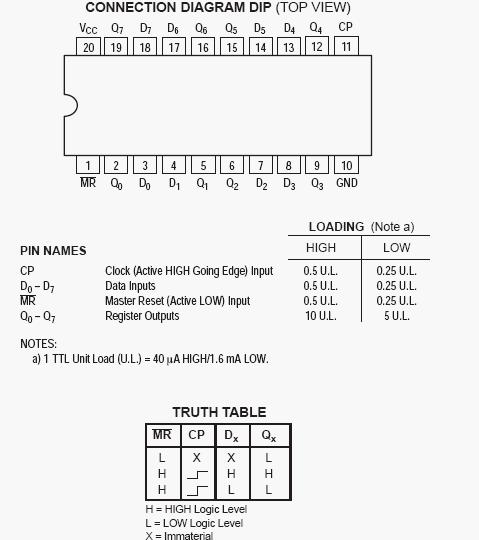

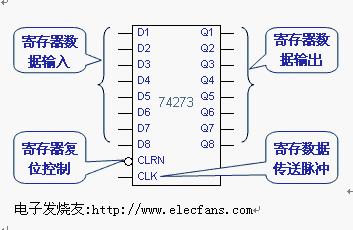

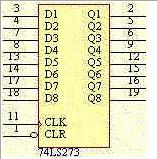

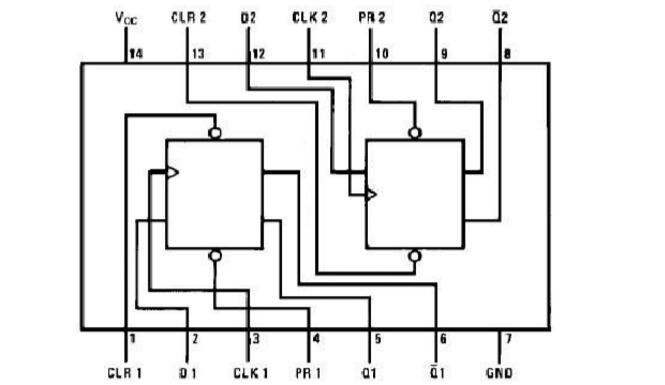

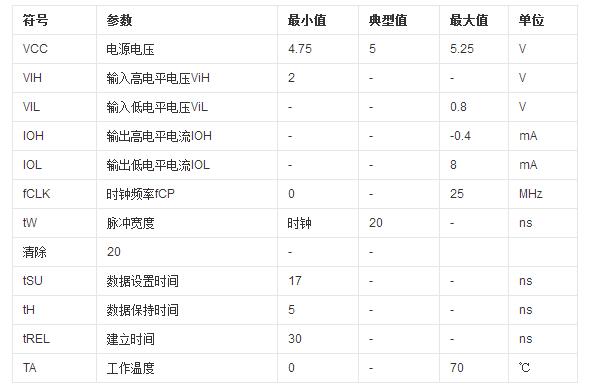

74LS273是八D觸發(fā)器。8個(gè)單邊輸出的觸發(fā)器,緩沖時(shí)鐘和直接清除輸入,數(shù)據(jù)獨(dú)立輸入到各觸發(fā)器。

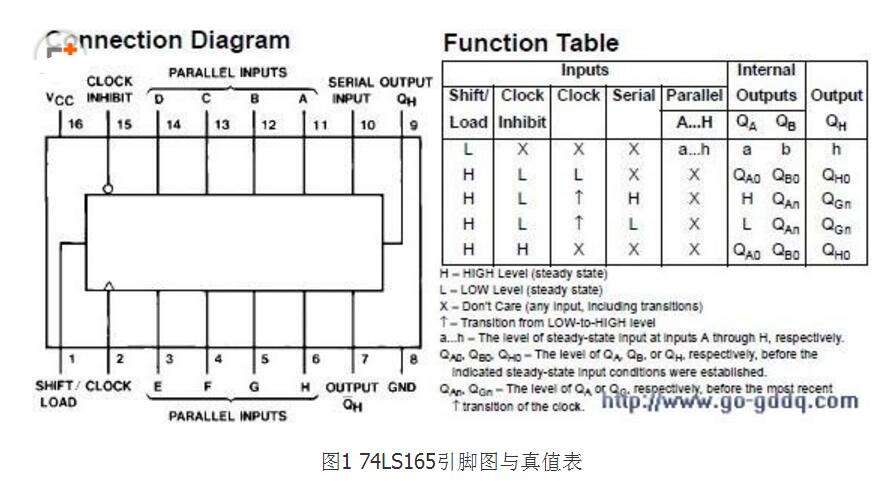

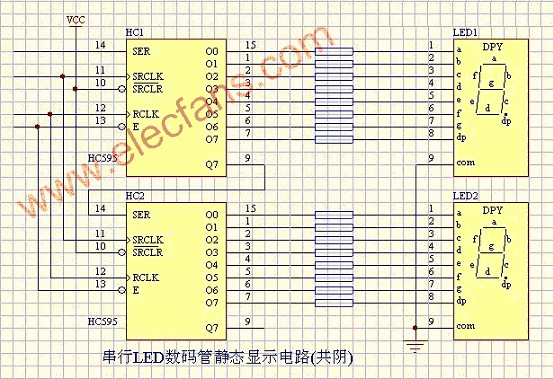

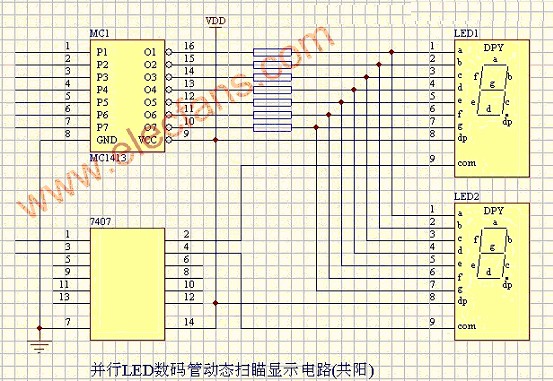

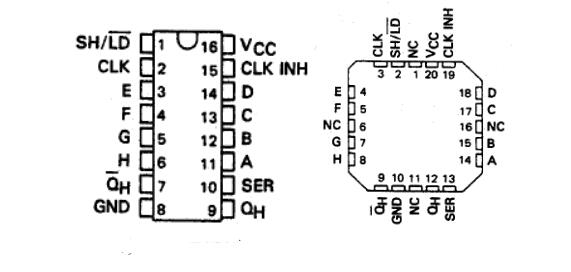

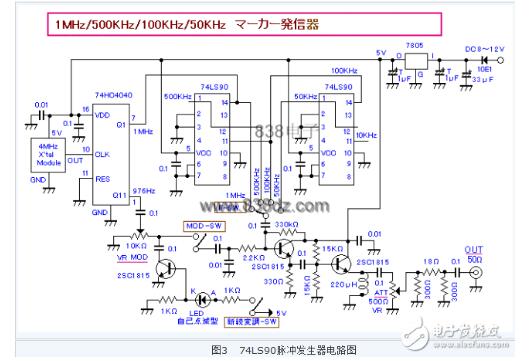

多位LED顯示時(shí),常將所有位的段選線并聯(lián)在一起,由一個(gè)8位I/O口控制,也可采用并行擴(kuò)展口構(gòu)成顯示電路,通常,需要擴(kuò)展器件管腳的較多,價(jià)格較高。在本測(cè)量?jī)x中,為了節(jié)約I/O口資源,采用了由Max7219芯片構(gòu)成的串行顯示方式。Max7219是串行輸入,輸出共陰極顯示驅(qū)動(dòng)電路,可直接與單片機(jī)的3條I/O線接口,特別適用于I/O口線少的系統(tǒng),并且可以程序控制數(shù)碼管的亮度。在本設(shè)計(jì)中,采用P3.3~P3.4三條線經(jīng)74LS273鎖存后與Max7219相連接,P3.3、P3.4鎖存后分別作為7219串行數(shù)據(jù)輸入信號(hào)DIN和時(shí)鐘信號(hào) CLK,P3.5輸出口鎖存作為L(zhǎng)OAD信號(hào)。具體硬件線路圖見圖。

主要硬件連接圖

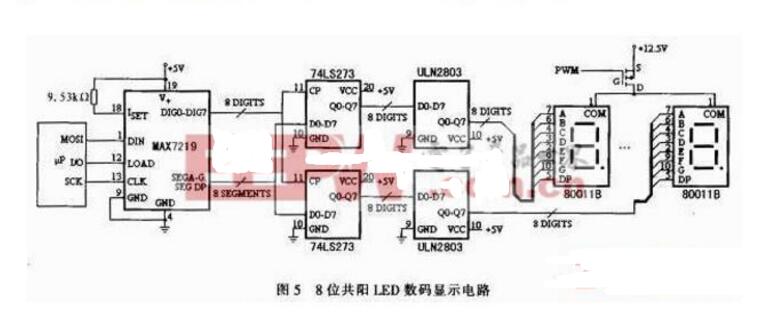

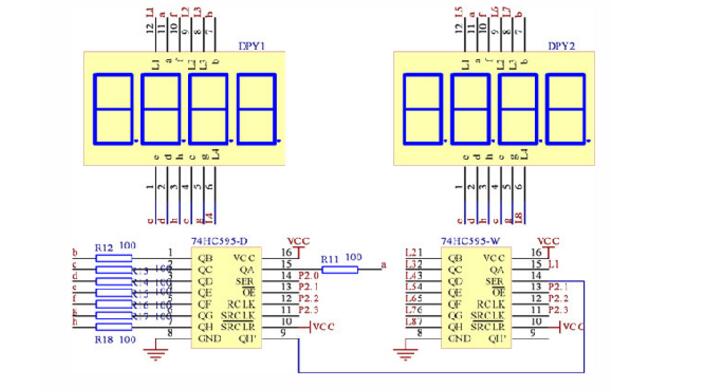

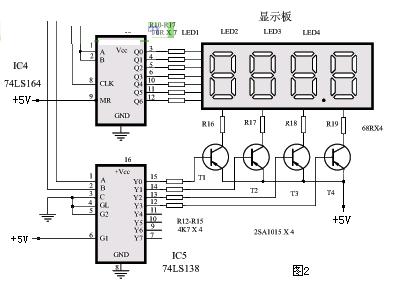

74ls273應(yīng)用電路圖二:8位共陽(yáng)LED數(shù)碼顯示電路

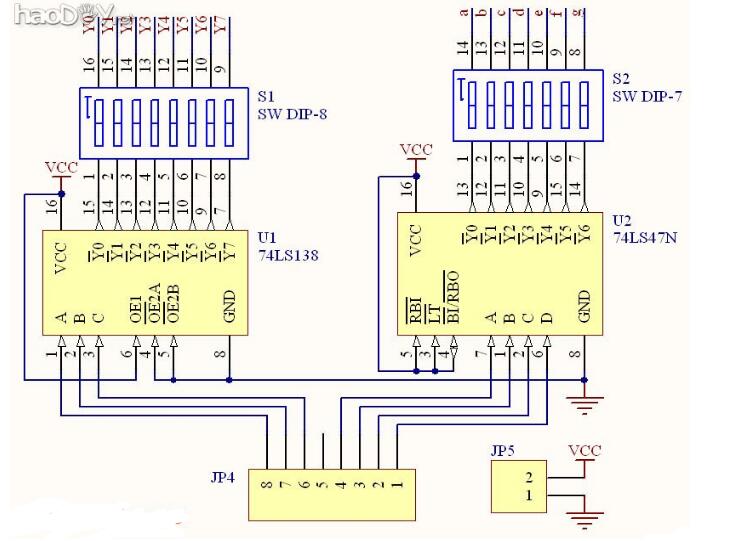

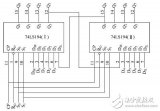

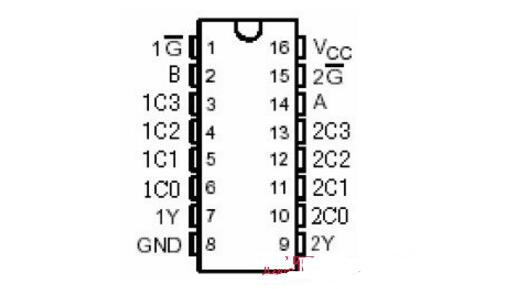

圖5為8位共陽(yáng)LED數(shù)碼顯示電路,圖中例叭義7219引腳DIGO一DIG7位碼線分別接8片74LS273鎖存器11(C的腳鎖存控制端,相當(dāng)于片選信號(hào);段碼線5EGA一SEGG和SEGOp以數(shù)據(jù)總線形式接在8片74LS273觸發(fā)器器的00一07輸入端;當(dāng)DIGO一OIG7片選信號(hào)某一位是低電平時(shí),數(shù)據(jù)總線00一07為對(duì)應(yīng)的段碼數(shù)據(jù);當(dāng)片選信號(hào)11(C喲腳有一個(gè)上升沿,立即鎖存輸入腳的電平狀態(tài),并立即呈現(xiàn)在輸出腳QO一Q7上鎖存:DIGO一OIG7片選低電平信號(hào)循環(huán)掃描,將要顯示的數(shù)據(jù)段碼,分別送入對(duì)應(yīng)的觸發(fā)器鎖存。

ULN2803接收74LS273鎖存器輸出信號(hào),實(shí)現(xiàn)對(duì)數(shù)碼管的驅(qū)習(xí)顯示。ULN28O3集電極開路輸出口上掛共陽(yáng)數(shù)碼管的段碼弓}腳,共陽(yáng)數(shù)碼管公共弓}腳接電源正極。當(dāng)74LS273鎖存器輸出高電平時(shí),ULN2803驅(qū)動(dòng)數(shù)碼管對(duì)應(yīng)段碼亮,反之滅。

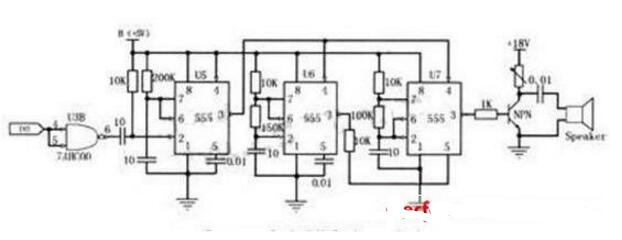

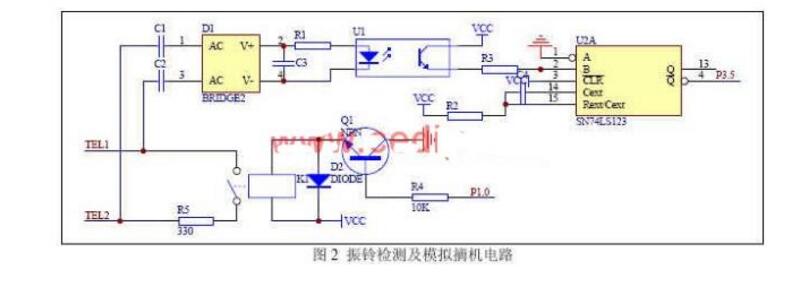

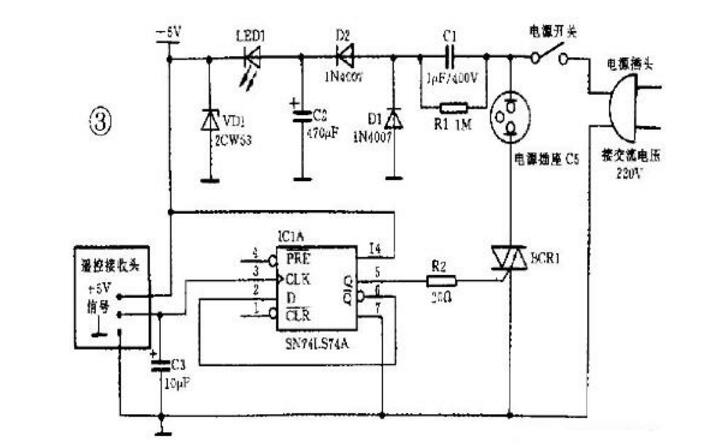

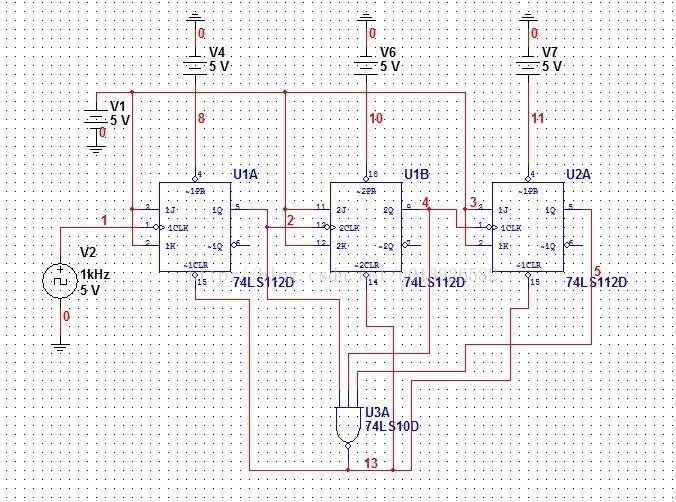

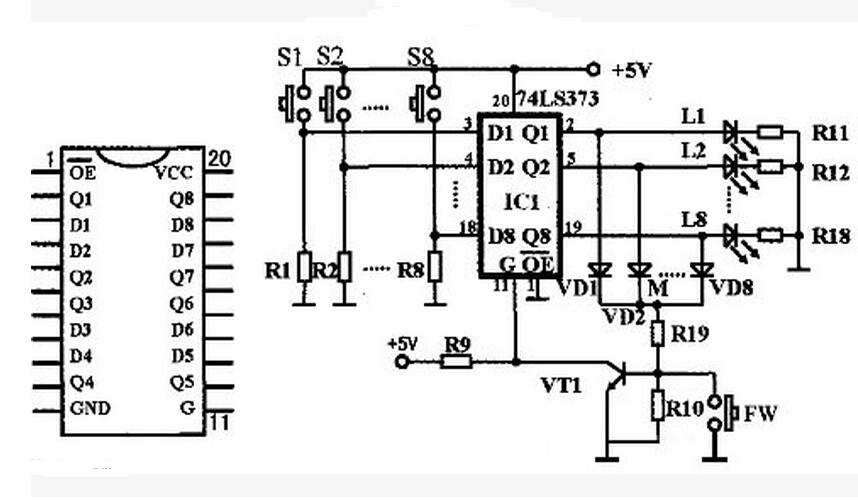

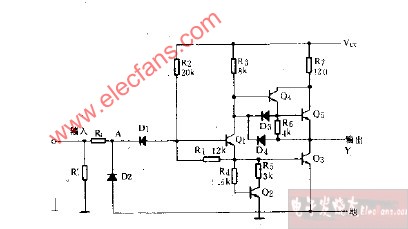

74ls273應(yīng)用電路圖三:遙控?fù)尨鹌髦麟娐?/strong>

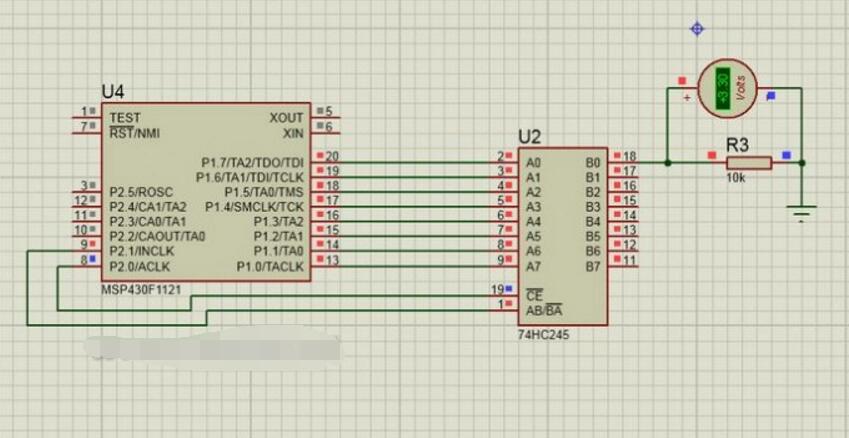

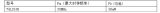

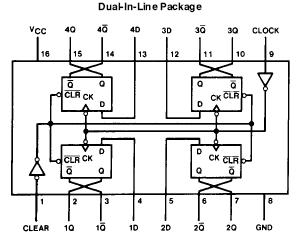

下圖為遙控?fù)尨鹌髦麟娐贰.?dāng)接收器接收到遙控發(fā)射器的信號(hào)后,將相應(yīng)的編碼數(shù)據(jù)輸入到D觸發(fā)器74LS273(1)的輸入端,與此同時(shí),74LS273(2)的CP端利用接收器輸出的VI信號(hào)上升沿將Do端的高電平輸出到Qo端,Qo由低電平轉(zhuǎn)換為高電平,將Qo信號(hào)的跳變作為74LS273(1)的時(shí)鐘信號(hào)使接收器輸出的編碼數(shù)據(jù)輸出至74LS273(1)的輸出端,并保持鎖定狀態(tài),譯碼器將BCD碼數(shù)據(jù)信號(hào)譯碼后在LED上顯示。

若要再次搶答,則需清零和消鎖。用遙控方式清零,方法很簡(jiǎn)單,將接收器的C、D信號(hào)通過(guò)與非門作為控制信號(hào),接到兩觸發(fā)器的CR端,當(dāng)主持人使用復(fù)位遙控器時(shí),接收器輸出“1100”,兩觸發(fā)器清零,觸發(fā)器74LS273(1)的CP端恢復(fù)低電平,鎖定狀態(tài)解除,下一次搶答準(zhǔn)備就緒。

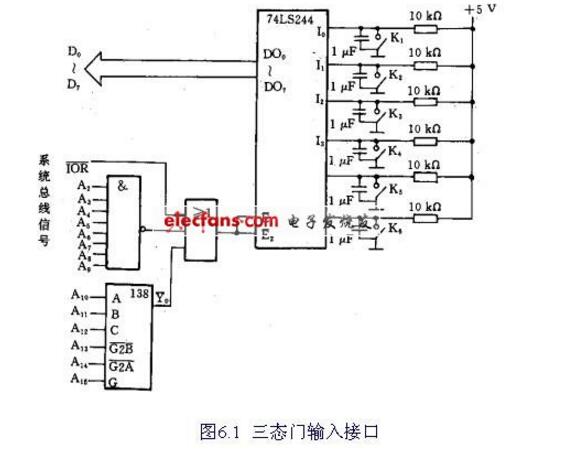

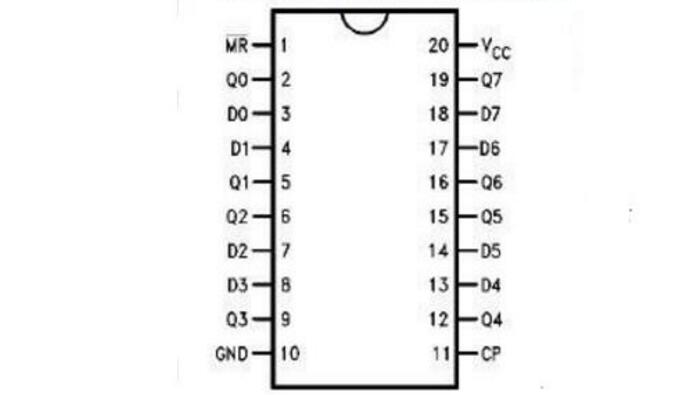

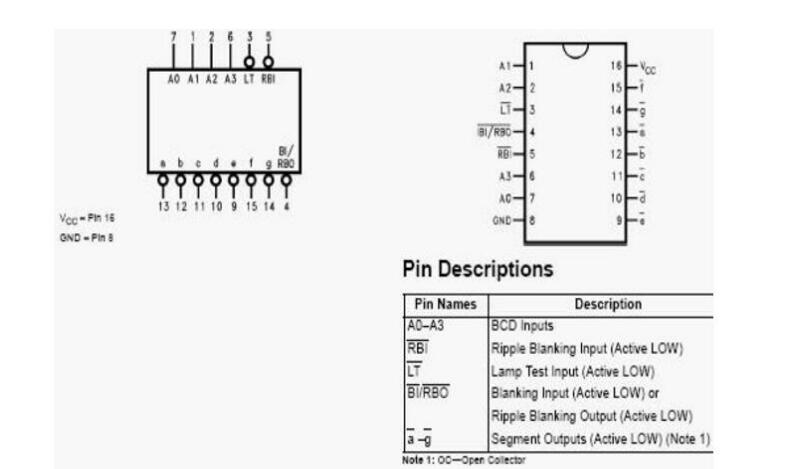

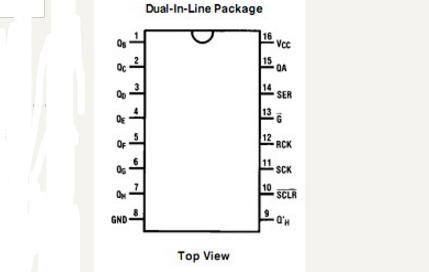

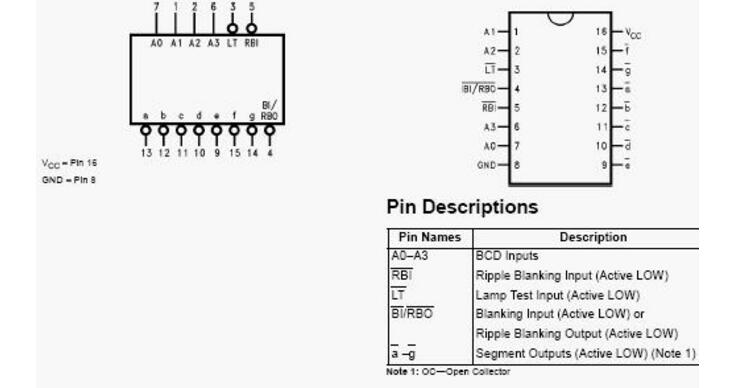

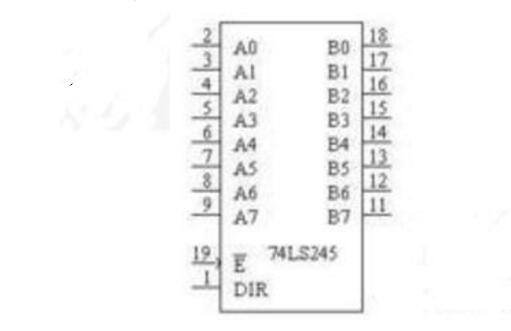

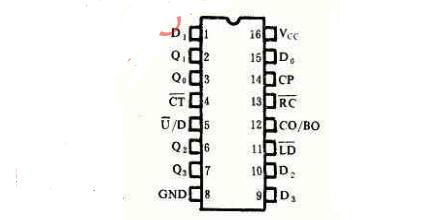

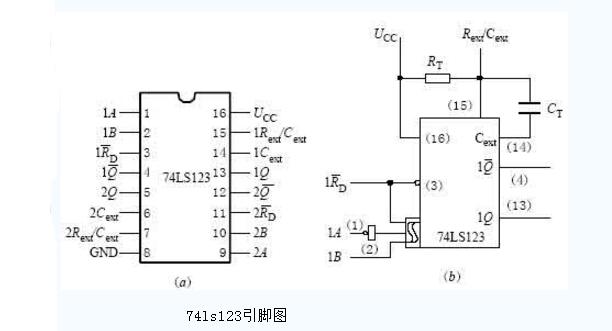

74ls273應(yīng)用電路圖四:三態(tài)門接口芯片

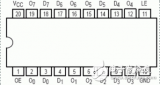

一個(gè)典型的三態(tài)門接口芯片(74LS244)如圖所示。從圖中不難看出該芯片由8個(gè)三態(tài)門構(gòu)成,其中每4個(gè)三態(tài)門由一個(gè)控制端來(lái)控制。當(dāng)控制端有效時(shí)(低電平),三態(tài)門導(dǎo)通;當(dāng)它們?yōu)楦唠娖綍r(shí),相應(yīng)的三態(tài)門呈現(xiàn)高阻狀態(tài)。在圖6.1中,三態(tài)門74LS244采用部分地址譯碼——地址線A1和A0未參加譯碼,故它所占的地址為83FCH~83FFH。我們可以用其中任何一個(gè)地址,而其他重疊的3個(gè)地址空著不用。

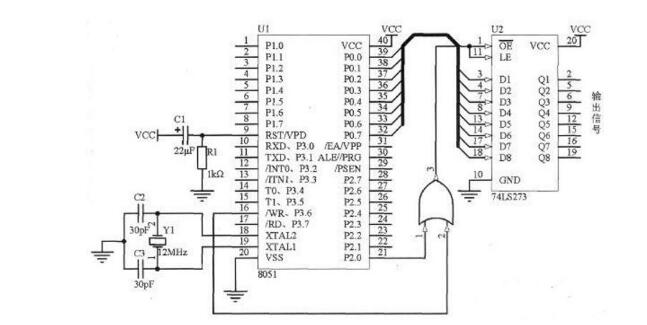

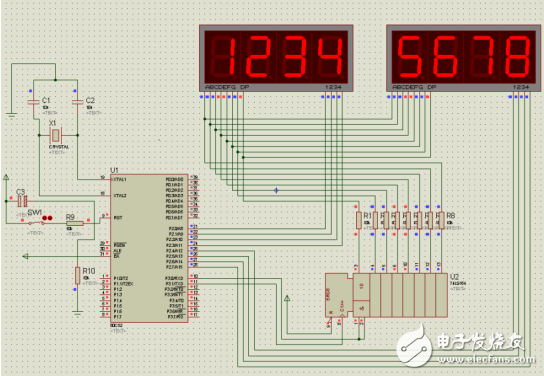

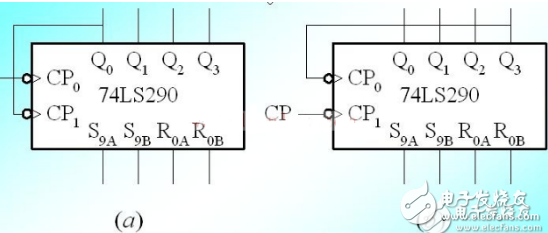

74ls273應(yīng)用電路圖五:?jiǎn)纹瑱C(jī)系統(tǒng)功能實(shí)現(xiàn)

89C51及74LS273、74LS244組成的單片機(jī)系統(tǒng)功能實(shí)現(xiàn)。

(1)編寫顯示程序,顯示“123456”。

(2)編寫主程序,功能為:當(dāng)有鍵按下(0~7號(hào))時(shí),都顯示鍵號(hào); 無(wú)鍵按下,保持原有顯示狀態(tài)。

74ls273應(yīng)用電路圖六:74LS273實(shí)現(xiàn)端口擴(kuò)展

下圖采用74LS273實(shí)現(xiàn)端口擴(kuò)展,P2.1與WR信號(hào)組成鎖存信號(hào),具體電路連接如圖所示。

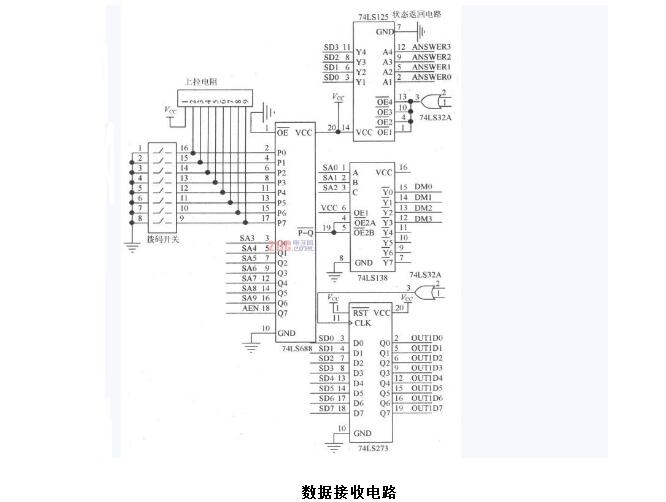

74ls273應(yīng)用電路圖七:數(shù)據(jù)接收電路

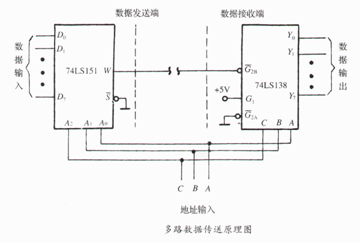

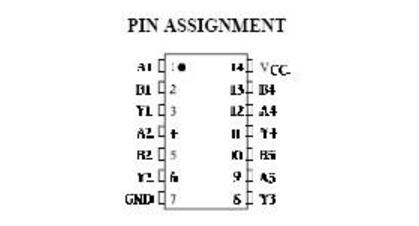

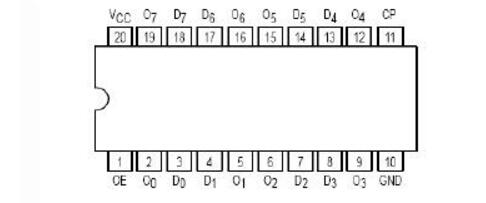

數(shù)據(jù)接收電路就是要在正確的時(shí)序上將所需的數(shù)據(jù)進(jìn)行提取,還要實(shí)現(xiàn)將電路工作狀態(tài)傳送回總線,以便總線決定是否發(fā)送下組數(shù)據(jù)的功能。由于PC104總線最高支持約8MHz的時(shí)鐘頻率,而受控設(shè)備所需的2FSK信號(hào)頻率為幾千赫茲,因此這里只用8位數(shù)據(jù)總線就完全能夠滿足要求。

總線接收電路如圖所示。其中SD0~SD9,SA0~SA9是從總線發(fā)來(lái)的數(shù)據(jù)、地址信號(hào),SELO~SEL3為分路選擇信號(hào),ANSWER0~ANSWER3為FPGA的狀態(tài)返回信號(hào),由于總線速度要比2FSK輸出速度高得多,因此,總線要對(duì)FPGA數(shù)據(jù)緩存器是否為空進(jìn)行查詢,當(dāng)FPGA沒有完成數(shù)據(jù)轉(zhuǎn)換時(shí),總線要等下個(gè)周期,直到狀態(tài)返回信號(hào)顯示FPGA內(nèi)部為空時(shí),總線才可以發(fā)送下組數(shù)據(jù)到FPGA。74LS273負(fù)責(zé)將每路的數(shù)據(jù)分別進(jìn)行鎖存,4路數(shù)據(jù)共使用4個(gè)。OUT1D0~D7為第一路8位數(shù)據(jù)輸出,LOCK0為其控制信號(hào),表示數(shù)據(jù)的更新。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論