以雙極型半導體管為基本元件,集成在一塊硅片上,并具有一定的邏輯功能的電路稱為雙極型邏輯集成電路,簡稱TTL邏輯門電路。

下面首先討論基本的BJT反相器的開關速度不高的原因 ,再討論改進的TTL反相器和TTL邏輯門電路。

BJT開關速度受到限制的原因主要是由于BJT基區內存儲電荷的影響,電荷的存入和消散需要一定的時間。

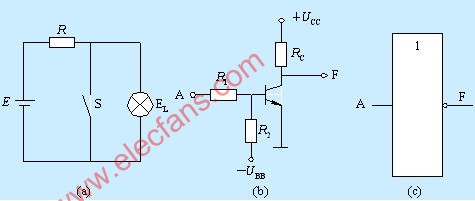

考慮到負載電容CL的影響后基本反相器將成為如下圖所示的電路

。圖中CL包含了門電路之間的接線電容以及門電路的輸入電容。

當反相器輸出電壓vO由低向高過渡時 ,電路由VCC通過Rc對CL充電。

當vO由高向低過渡時,CL又將通過BJT放電。

這樣,CL的充、放電過程均需經歷一定的時間,這必然會增加輸出電壓vO波形的上升時間和下降時間。特別是CL充電回路的時間常數RcCL較大時,vO上升較慢,即增加了上升時間。

基于器件內部和負載電容的影響 ,導致基本BJT反相器的開關速度不高。

尋求更為實用的TTL電路結構,是下面所要討論的問題。

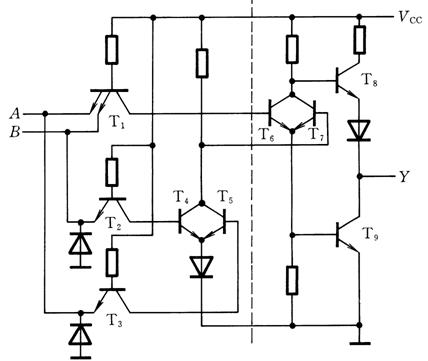

由前面的分析已知,帶電阻負載的BJT反相器 ,其動態性能不理想。在保持邏輯功能不變的前提下,可以另外增加若干元器以改善其動態性能 ,如減少由于BJT基區電荷存儲效應和負載電容所引起的時延。這需改變反相器輸入電路和輸出電路的結構 ,以形成TTL反相器的基本電路。下圖就是一個TTL反相器的基本電路。

該電路由三部分組成:

由三極管T1組成電路的輸入級;

由T3、T4和二極管D組成輸出級;

由T2組成的中間級作為輸出級的驅動電路,將T2的單端輸入信號vI2轉換為互補的雙端輸出信號vI3和vI4,以驅動T3 和T4。

1.TTL反相器的工作原理

這里主要分析TTL反相器的邏輯關系,并估算電路中有關各點的電壓,以得到簡單的定量概念。

(1)當輸入為高電平,如vI=3.6V時,電源VCC通過Rbl和T1的集電結向T2、T3提供基極電流,使T2、T3飽和,輸出為低電平,如 vO=0.2V。此時 VB1=VBC1+VBE2+VBE3=(0.7+0.7+0.7)V=2.1V

T1的發射結處于反向偏置 ,而集電結處于正向偏置。所以T1處于發射結和集電結倒置使用的放大狀態。由于T2和T3飽和,輸出 VC3 =0.2V,同時可估算出VC2的值:VC2=VCE2+VB3=(0.2+0.7)V=0.9V

此時,VB4=VC2=0.9V。作用于T4的發射結和二極管D的串聯支路的電壓為VC2-Vo=(0.9-0.2)V=0.7V,顯然,T4和D均截止,實現了反相器的邏輯關系:輸入為高電平時,輸出為低電平。

(2)當輸入為低電平且電壓為0.2V時,T1的發射結導通,其基極電壓等于輸入低電壓加上發射結正向壓降,即:VB1=(0.2+0.7)V=0.9V

此時VB1作用于T1的集電結和T2、T3的發射結上,所以T2、T3都截止,輸出為高電平。

由于T2截止,VCC通過RC2向T4提供基極電流,致使T4和D導通,其電流流入負載。

輸出電壓為vO=Vcc-VBE4-VD=(5-0.7-0.7)V=3.6V

同樣也實現了反相器的邏輯關系:輸入為低電平時,輸出為高電平。

2.采用輸入級以提高工作速度

當TTL反相器輸入電壓由高(3.6V)變低(0.2V)的瞬間,VB1 =(0.2+0.7)V=0.9V。但由于T2、T3原來是飽和的 ,它們的基區存儲電荷還來不及消散,在此瞬間,T2、T3的發射結仍處于正向偏置,T1的集電極電壓為Vc1 =VBE2+VBE3=(0.7+0.7)V=1.4V。

此時T1的集電結為反向偏置[集電結電壓=VB1-VC1=(1-1.4)V=-0.4V],因輸入為低電平(0.2V)時,T1的發射結為正向偏置,于是T1工作在放大區。這時產生基極電流iB1,其射極電流 流入低電平的輸入端。集電極電流

流入低電平的輸入端。集電極電流 的方向是從T2的基極流向T1的

的方向是從T2的基極流向T1的

集電極,它很快地從T2的基區抽走多余的存儲電荷,使T2迅速地脫離飽和而進人截止狀態。T2的迅速截止導致T4立刻導通,相當于T3的負載是個很小的電阻,使T3的集電極電流加大,多余的存儲電荷迅速從集電極消散而達到截止,從而加速了狀態轉換。

3.采用推拉式輸出級以提高開關速度和帶負載能力

由T3、T4和二極管D組成推拉式輸出級。其中T4組成電壓跟隨器,而T3為共射極電路,作為T4的射極負載。這種輸出級的優點是,既能提高開關速度,又能提高帶負載能力。根據所接負載的不同,輸出級的工作情況可歸納如下:

(1)輸出為低電平時,T3處于深度飽和狀態 ,反相器的輸出電阻就是T3的飽和電阻,這時可驅動較大的電流負載。而且由于T4截止

,所以負載電流就是T3的集電極電流,也就是說T3的集電極電流可以全部用來驅動負載。

(2)輸出為高電平時,T3截止 ,T4組成的電壓跟隨器的輸出電阻很小,所以輸出高電平穩定,帶負載能力也較強。

(3)輸出端接有負載電容CL時 ,當輸出由低電平跳變到高電平的瞬間,T2和T3由飽和轉為截止,由于T3的基極電流是經T2放大的電流,所以T2比T3更早脫離飽和,于是T2的集電極電壓vC2比T3的集電極電壓vC3上升更快。同時由于電容CL兩端的電壓不能突變,使c2和c3之間的電位差增加,因而使T4在此瞬間基極電流很大,T4集電極與發射極之間呈現低電阻 ,故電源VCC經RC4和T4的飽和電阻對電容CL迅速充電,其時間常數很小,使輸出波形上升沿陡直。而當輸出電壓由高變低后,輸出管T3深度飽和,也呈現很低的電阻,已充電的CL通過它很快放電,迅速達到低電平,因而使輸出電壓波形的上升沿和下降沿都很好。

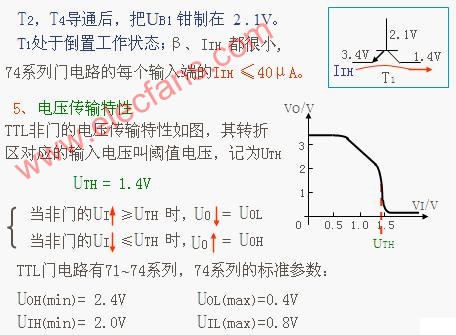

現在來分析TTL反相器的傳輸特性。下圖為用折線近似的TTL反相器的傳輸特性曲線。由圖可見 ,傳輸特性由4條線段AB、BC、CD和DE所組成。

AB段:此時輸入電壓vI很低,T1的發射結為正向偏置。在穩態情況下,T1飽和致使T2和T3截止,同時T4導通。輸出vo=3.6V為高電平。

當vI增加直至B點 ,T1的發射結仍維持正向偏置并處于飽和狀態

。但vB2=vc1增大導致T2的發射結正向偏置 。當T1仍維持在飽和狀態時,vB2的值可表示為 vB2=vI+VCES

為求得B點所對應的vI,可以考慮vB2剛好使T2的發射結正向偏置并開始導電。此時vB2應等于T2、發射結的正向電壓VF≈0.6V。但iE2≈0在忽略vRe2。的情況下,于是由上式得:

BC段:當vI的值大于B點的值時,由T1的集電極供給T2的基極電流

,但T1仍保持為飽和狀態 ,這就需要使T1的發射結和集電結均為正向偏置。

在BC段內,T2對vI的增量作線性放大,其電壓增益可表示為

電壓增量上 通過T4的電壓跟隨作用而引至輸出端形成輸出電壓的增量

通過T4的電壓跟隨作用而引至輸出端形成輸出電壓的增量 ,且在一定范圍內,有

,且在一定范圍內,有 ,所以傳輸特性BC段的斜率為

,所以傳輸特性BC段的斜率為 。必須注意到在BC段內,Re2上所產生的電壓降還不足以使T3的發射結正向偏置,T3仍維持截止狀態。

。必須注意到在BC段內,Re2上所產生的電壓降還不足以使T3的發射結正向偏置,T3仍維持截止狀態。

當Re2上的電壓vRe2達到一定的值,能使T3的發射結正偏,并有vBE3=VF=0.7V時,則有

或

或

式中VF=0.7V,表示T3已導通。由于 ,C點處的輸出電壓變為

,C點處的輸出電壓變為

根據線段BC的斜率為-1.6,對應于C點的vI值可由下述關系求得:

由此得

CD段:當vI的值繼續增加并超越C點,使T3飽和導通,輸出電壓迅速下降至v0≈0.2V。D點處的vI(D)值,可以根據T2、T3兩發射結電壓VF≈0.7V來估算。因此有

DE段:當vI的值從D點再繼續增加時,T1將進人倒置放大狀態,保持vO=0.2V。至此,得到了TTL反相器的ABCDE折線型傳輸特性。

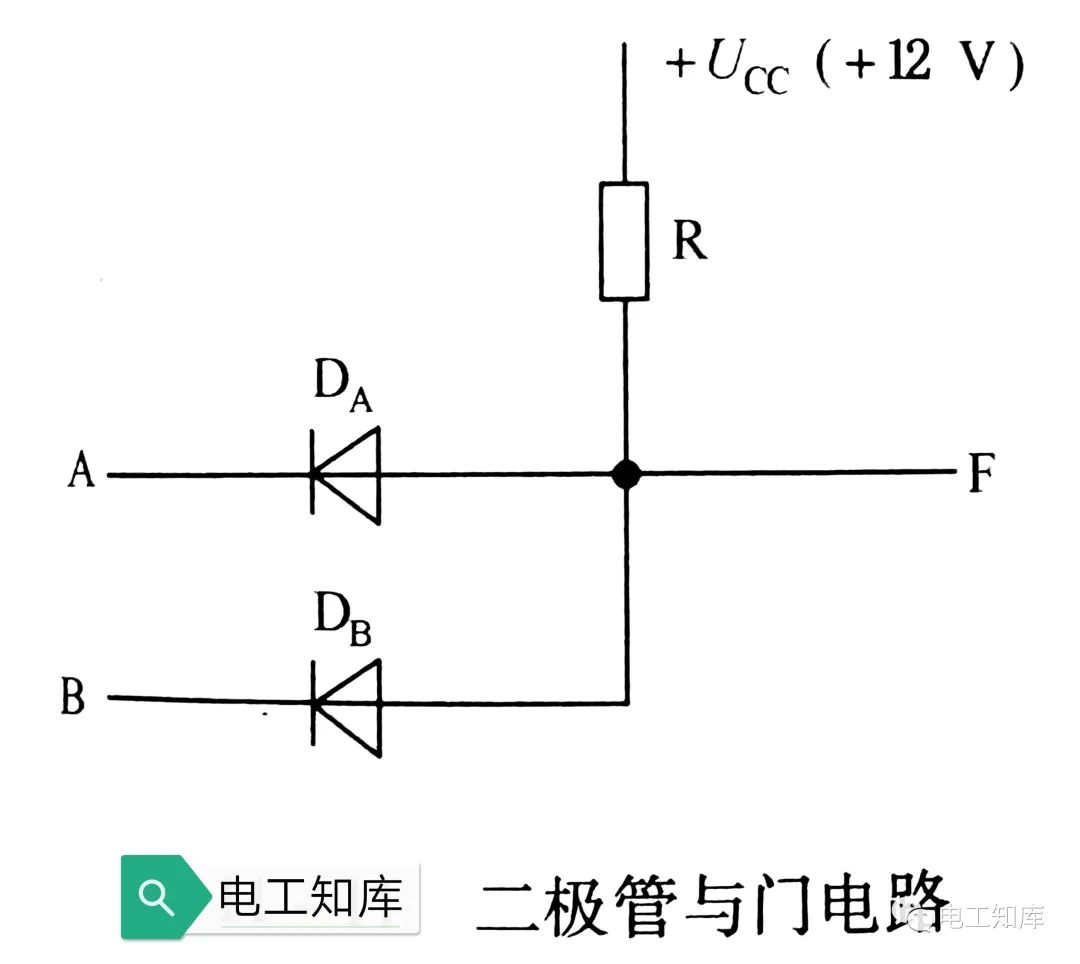

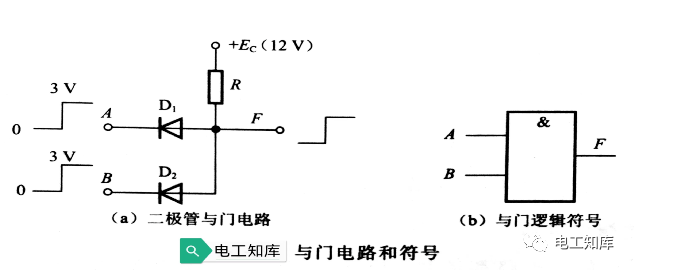

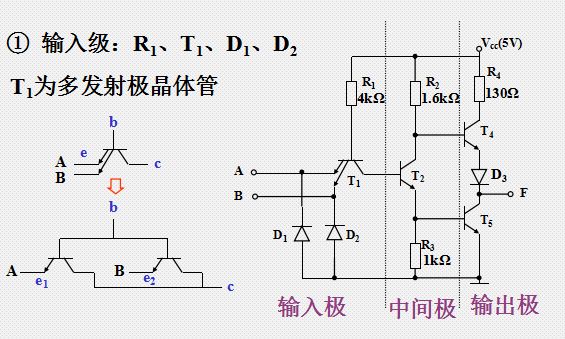

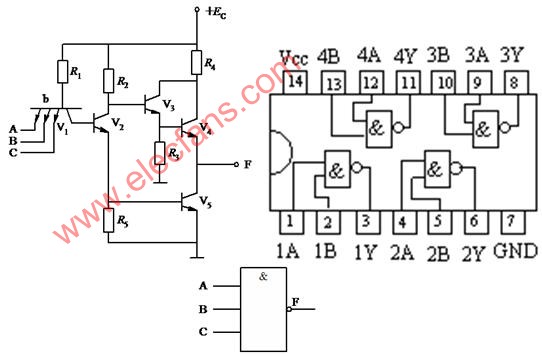

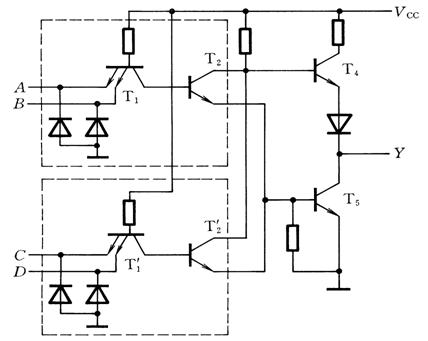

基本TTL反相器不難改變成為多輸入端的與非門 。它的主要特點是在電路的輸入端采用了多發射極的BJT ,如下圖所示。器件中的每一個發射極能各自獨立地形成正向偏置的發射結 ,并可促使BJT進人放大或飽和區。兩個或多個發射極可以并聯地構成一大面積的組合發射極。

下圖是采用多發射極BJT用作3輸入端TTL與非門的輸入器件的一個實例。當任一輸入端為低電平時,T1的發射結將正向偏置而導通,T2將截止。結果將導致輸出為高電平。只有當全部輸入端為高電平時

,T1將轉入倒置放大狀態,T2和T3均飽和,輸出為低電平。

1.傳輸特性

各種類型的TTL門電路,其傳輸特性大同小異,正如前面已經討論過的,這里不再討論。

2.輸入和輸出的高、低電壓

3.噪聲容限

噪聲容限表示門電路的抗干擾能力。

二值數字邏輯電路的優點在于它的輸入信號允許一定的容差。

高電平噪聲容限:VNH=VOH-VIH=2.4V-2V=0.4V

低電平噪聲容限:VNL=VIL-VOL=0.8V-0.4V=0.4V

4.扇入與扇出數

扇出數--門電路所能帶負載個數,與非門輸出端最多能接幾個同類的與非門。

扇出數No取決于負載類型

灌電流負載:負載電流從外電路流入與非門

拉電流負載:負載電流從與非門流向外電路

①灌電流工作情況

下圖表示TTL與非門的灌電流負載的情況。圖中左邊為驅動門,右邊為負載門,當驅動門的輸出端為邏輯0(低電壓VOL)時,負載門由電源VCC通過Rb1、T1的發射結和輸入端有電流IIL灌人驅動門T3的集電極,這就是灌電流負載的由來。不難理解,當負載門的個數增加時,總的灌電流IIL將增加,同時也將引起輸出低電壓VOL的升高。前已述

及TTL門電路的標準輸出低電壓VOL=0.4V,這就限制了負載門的個數

。在輸出為低電平的情況下,所能驅動的同類門的個數由下式決定:

②拉電流工作情況

當驅動門的輸出為高電平時 ,將有電流IIH。從驅動門拉出而流至負載門。當負載門的個數增多時,必將引起輸出高電壓的降低,但不得低于標準高電壓的低限值VIH=2V。這樣,輸出為高電平時的扇出數可表示如下:

通常基本的TTL門電路,其扇出數約為10 ,而性能更好的門電路的扇出數最高可達30~50。

一般TTL器件的數據手冊中,并不給出出數 ,而須用計算或用實驗的方法求得,并注意在設計時留有余地,以保證數字電路或系統能正常地運行

通常,輸出低電平電流IOL大于輸出高電平電流IOH,NOL不等于NOH

,因而在實際工程設計中,常取二者中的最小值。

例:試計算基本的TTL與非門7410帶同類門時的扇出數。

解:

(1)從TTL數據手冊可查到7410的參數如下:

IOL=16mA,IIL=-1.6mA

IOH=16mA,IIH=-1.6mA

數據前的負號表示電流的流向,對于灌電流取負號,計算時只取絕對值。

(2)根據式(2.4.14)可計算低電平輸出時的扇出數

(3)根據式(2.4.I5)可計算高電平輸出時的扇出數

可見這時NOL=NOH。如前所述,若NOL=NOH。則取較小的作為電路的扇出數。

扇入數NI取決于TTL門電路的輸入端個數。

5.傳輸延遲時間

這是一個表征門電路開關速度的參數,意味著門電路在輸入脈沖波形的作用下,其輸出波形相對于輸入波形延遲了多長時間。

假設在門電路的輸入端加入一脈沖波形、其幅度為0~VCC(單位為V)。相應的的輸出波形如下圖所示。通常門電路輸出由低電平轉換高電平或者由高電平轉換到低電平所經歷的時間分別用tPLH和tPHL表示,有時也采用平均傳輸延遲時間這一參數,即tPd=(tPLH+tPHL)/2。

6.功耗

功耗是門電路重要參數之一。

功耗有靜態和動態之分。

所謂靜態功耗指的是當電路沒有狀態轉換時的功耗,即與非門空載時電源總電流ICC與電源電壓VCC的乘積。

當輸出為低電平時的功耗稱為空載導通功耗PON;

當輸出為高電平時的功耗稱為截止功耗POFF;

PON總比POFF大。

至于動態功耗,只發生在狀態轉換的瞬間,或者電路中有電容性負載時,例如TTL門電路約有5PF的輸入電容,由于電容的充、放電過程,將增加電路的損耗。

對于TTL門電路來說,靜態功耗是主要的。

7.延時一功耗積

理想的數字電路或系統,要求它既具有高速度,同時功耗又低。在工程實踐中,要實現這種理想情況是較難的。高速數字電路往往需要付出較大的功耗為代價。一種綜合性的指標叫做延時一功耗積,用符號DP表示,單位為焦耳,即DP=tPdPD。

式中tpd=(tPLH+tHL)/2,PD為門電路的功耗,一個邏輯門器件的DP的值愈小,表明它的特性愈接于理想情況。

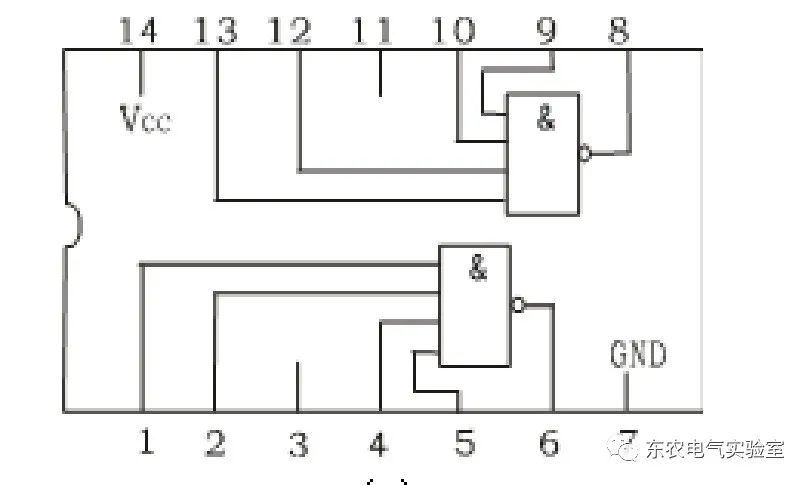

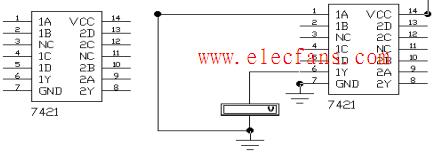

8. TTL集成門電路的封裝

(a)

(b)

圖(a)為14腳TTL集成門電路的封裝圖,圖(b)為其內部結構圖。

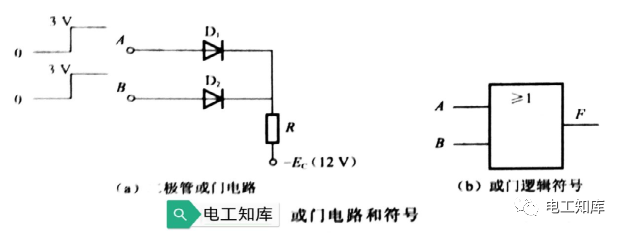

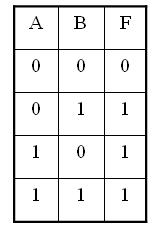

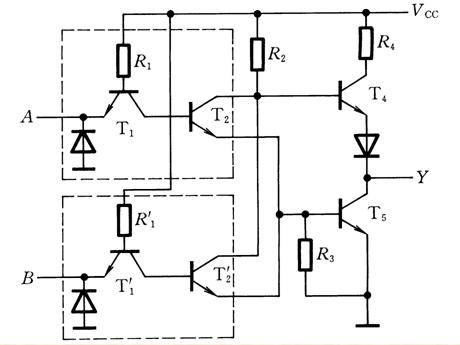

1.TTL或非門

下圖為TTL或非門的邏輯電路及其代表符號。

由圖可見 ,或非邏輯功能是對TTL與非門的結構改進而來,即用兩個 三極管T2A和T2B代替T2。

若兩輸入端為低電平,則T2A和T2B均將截止 ,iB3=0,輸出為高電平。

若A、B兩輸入端中有一個為高電平 ,則T2A或T2B將飽和 ,導致iB3>0,iB3便使T3飽和 ,輸出為低電平。這就實現了或非功能。即 。

。

2.集電極開路門

在工程實踐中將兩個門的輸出端并聯以實現與邏輯的功能稱為線與。

考察下圖所示的情況。當將圖中所示的兩個邏輯門的輸出連接在一起,并且當第一個門的輸出為高電平(第一個門的T4導通),第二個門的輸出為低電平(第二個門的T3導通)時,正如圖中紅線所示將出現一個大電流通道,很可能導致晶體管的損壞。

為了避免線與時的產生大電流,可以采用集電極開路門(簡稱OC門)來解決 。所謂集電極開路是指從TTL與非門電路的推挽式輸出級中刪去電壓跟隨器,如下圖所示:

對于一個兩輸入端的OC門,其在電路中的符號可用下圖來表示:

為了實現線與的邏輯功能,可將多個門電路輸出管T3的集電極至電源VCC之間,加一公共的上拉電阻RP,如下圖所示。為了簡明起見,圖中以兩個OC門并聯為例,其中圖標“ ”表示集電極開路之意。

”表示集電極開路之意。

上拉電阻Rp的值可以這樣來計算,主要考慮OC門必須驅動一定的拉電流或灌電流負載。有關這兩類負載的概念前已討論,這里仍然適用 ,所不同的是驅動門是由多個TTL門的輸出端直接并聯而成。當OC門中的一個TTL門的輸出為低電平 ,其他為高電平時,灌電流將由一個輸出BJT(如T1或T2)承擔 ,這是一種極限情況,此時上拉電阻RP具有限制電流的作用。為保證IOL不超過額定值IOL(max),必須合理選用RP的值。例如VCC=5V,RP=1kΩ,則IOL=5mA。

另一方面,由于門電路的輸出、輸入電容和接線電容的存在,RP的大小必將影響OC門的開關速度。RP的值愈大,負載電容的充電時間常數亦愈大,因而開關速度愈慢。RP的最小值RP(min)可按下式來確定

:

RP的最大值RP(max)可按下式來確定:

實際上,RP的值選在RP(min)和RP(max)之間,并且選用靠近RP(min)的標準值。

例:設TTL與非門74LS01(OC)驅動8個74LS04(反相器),試確定一合適大小的上拉電阻RP,設VCC=5V。

由以上計算可知Rp的值可在985Ω至18.75kΩ之間選擇 。為使電路有較快的開關速度,可選用一標準值為1kΩ的電阻器為宜。

集電極開路門除了可以實現多門的線與邏輯關系外,還可用于直接驅動較大電流的負載。

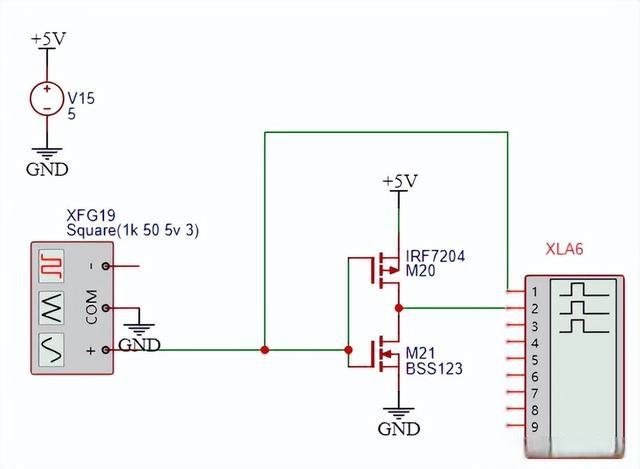

3.三態與非門(TSL)

利用OC門雖然可以實現線與的功能,但外接電阻Rp的選擇要受到一定的限制而不能取得太小,因此影響了工作速度。同時它省去了有源負載,使得帶負載能力下降。為保持推拉式輸出級的優點,還能作線與聯接,人們又開發了一種三態與非門,它的輸出除了具有一般與非門的兩種狀態,即輸出電阻較小的高、低電平狀態外,還具有高輸出電阻的第三狀態,稱為高阻態,又稱為禁止態。

一個簡單的TSL門的電路如上圖所示。其中CS為片選信號輸入端,A、B為數據輸入端。

當CS=1時,TSL門電路中的T5處于倒置放大狀態 ,T6飽和,T7截止,即其集電極相當于開路。此時輸出狀態將完全取決于數據輸入端A、B的狀態,電路輸出與輸入的邏輯關系與一般與非門相同。這種狀態稱為TSL的工作狀態。

當CS=0時T7導通,使T4的基極鉗制于低電平。同時由于低電平的信號送到T1的輸入端,迫使T2和T3截止 。這樣T3和T4均截止,門的輸出端L出現開路,既不是低電平,又不是高電平 ,這就是第三工作狀態。這樣,當CS為高電平時,TSL門的輸出信號送到總線 ,而當CS為低電平時,門的輸出與數據總線斷開,此時數據總線的狀態由其他門電路的輸出所決定。

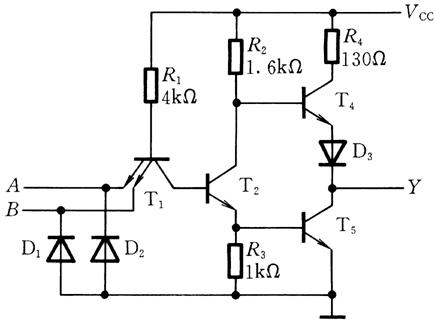

抗飽和TTL電路是目前傳輸速度較高的一類TTL電路。這種電路由于采用肖特基勢壘二極管SBD鉗位方法來達到抗飽和的效果 ,一般稱為SBDTTL電路(簡稱STTL電路),其傳輸速度遠比基本TTL電路為高。

肖特基勢壘二極管的工作特點如下:

(1)它和PN結一樣,同樣具有單向導電性,這種鋁-硅勢壘二極管導通電流的方向是從鋁到硅。

(2)AL-SiSBD的導通閾值電壓較低,約為0.4~0.5V ,比普通硅PN結約低0.2V。

(3)勢壘二極管的導電機構是多數載流子 ,因而電荷存儲效應很小。

根據前面的學習,我們已經知道,BJT工作在飽和時 ,發射結和集電結都處在正向偏置,集電結正向偏置電壓越大,則表明飽和程度越深。

為了限制BJT的飽和深度,在BJT的基極和集電極并聯上一個導通閾值電壓較低的肖特基二極管,如下圖所示。

當沒有SBD時,隨著基級電壓的升高,電流沿著藍線方向流動。由于SBD的作用,當基級電壓大于0.4V時, SBD首先電導通,電流沿著紅線方向流動(如下圖所示),從而使T的基極電流不會過大(而且使T的集電結正向偏壓將被鉗制在0.4V左右),因此SBD起到抵抗過飽和的作用,因而又將這種電路稱為抗飽和電路,使電路的開關時間大為縮短。

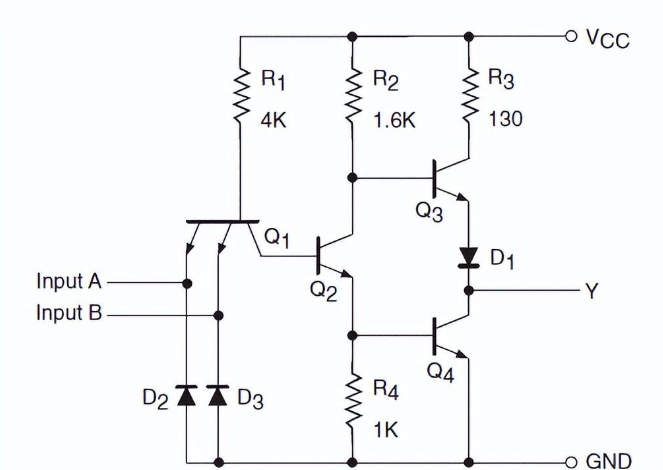

下圖為肖特基TTL(STTL)與非門的典型電路。與基本TTL與非門電路相比,作了若干改進。在基本的TTL電路中 ,T1、T2和T3工作在深度飽和區,管內電荷存儲效應對電路的開關速度影響很大。現在除T4外,其余的BJT均采用SBD鉗位,以達到明顯的抗飽和效果。其次,基本電路中的所有電阻值這里幾乎都減半。這兩項改進導致門電路的開關時間大為縮短。由于電阻值的減小也必然會引起門電路功耗的增加。

STTL門電路還有以下三點對基本TTL電路的性能作了改進:

(1)二極管D被由T4和T5所組成的復合管所代替,當輸出由低電平向高電平過渡時,由于復合管電路的電流增益很大,輸出電阻很小

,從而減小了電路對負載電容的充電時間。

(2)電路輸入端所加的SBD—DA和DB,用來減小由門電路之間的連線而引起的雜散信號。

(3)基本電路中的Re2(1kΩ)改為由T6與Rc6 、Rb6的組合電路所代替。這個組合電路是有源非線性電阻。當其兩端的電壓(發射極e2對地)較低時,呈現很大的電阻,而當其兩端的電壓達到0.7V左右時,則呈現很小的電阻。這樣,當與非門的全部輸入端由低電平轉向高電平時,有源電阻開始不導通使T3很快達到飽和;反之,當電路的全部輸入端(或其中之一)由高電平轉向低電平時,T2和T3將截止,由于T3飽和時,VBE=0.7V,在轉換開始的瞬間,有源電阻的阻值很小

T3基區存儲的電荷通過此低阻回路很快消散。由于這個緣故,有源非線性電路稱為有源下拉電路 ,它與有源上拉電路是對應的 。意即將 VBE3從0.7 V很快拉到0V,從而使輸出電壓很快升高,即提高了開關速度。

基于上述特點,STTL與非門具有較為理想的傳輸特性。與基本TTL反相器的傳輸特性相比,C點不再存在了,由B點直接下降到D點,即傳輸特性變化非常陡峭,見下圖。

除典型的肖特基型(STTL)外,尚有低功耗肖特基型(LSTTL)、先進的肖特基型(ASTTL),先進的低功耗型(ALSTTL)等,它們的技術參數各有特點,是在TTL工藝的發展過程中逐步形成的。

TTL門電路的各種系列的性能比較

|

電子發燒友App

電子發燒友App

評論