LeonardoSpectrum 是Mentor Graphics公司設計的功能強大的EPLD/FPGA/ASIC綜合工具,支持大部分EPLD/FPGA廠商的產品。LeonardoSpectrum支持VHDL、Verilog、EDIF的綜合、優化和定時分析,可以運行在Windows 98/2000/NT/XP和HP、SUN 的UNIX平臺上。

LeonardoSpectrum通過名為exemplar的庫,可以在用HDL設計FPGA/EPLD時使用與原理圖設計相同的功能。LeonardoSpectrum對于Xilinx公司的EPLD/FPGA支持尤其完善,使得用HDL的設計在效率和功能上可以和原理圖的設計相當。本文總結了使用LeonardoSpectrum過程一些有用的設計方法。

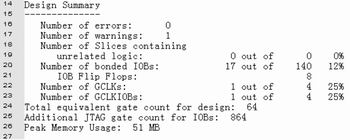

圖1 全局時鐘使用的map結果

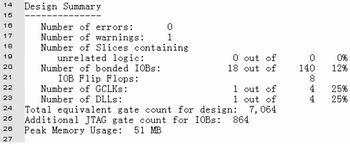

圖2 延遲鎖相環使用map結果

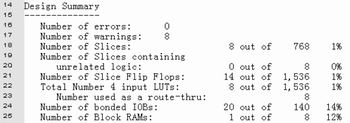

圖3 塊狀RAM的map結果

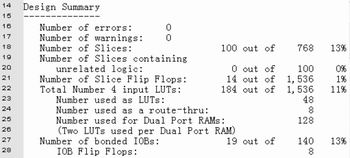

圖4 分布式RAM的map結果

屬性的使用

在LeonardoSpectrum中,可以在程序中對信號賦予屬性來對綜合結果進行控制。在使用LeonardoSpectrum綜合時,除了LeonardoSpectrum提供的屬性外,可以把Xilinx原理圖設計中的某些元件作為屬性來賦予信號,主要限于雙端口的元件,例如IBUFG,BUFG等等。LeonardoSpectrum所提供的屬性可以參看使用手冊。

如果使用LeonardoSpectrum來綜合,建議調用exemplar庫,以獲得更多的功能支持,本文介紹的程序都需要使用exemplar庫。下面是對程序中一個信號通過賦予bufg的屬性而定義該信號為全局時鐘的例子。

......

ARCHITECTURE rtl of bufg IS

SIGNAL clk :td_logic;

attribute buffer_sig of clk: signal is "bufg";

BEGIN

clk<=clkin;

clkout<=clk;

process(clk)

begin

if(clk'event and clk='1') then

end if;

end process;

END rtl;

這個程序選用的芯片是Xilinx的spartanII 系列XC2S50-5QP208,經LeonardoSpectrum綜合后,用Xilinx ISE5.1進行map后的結果如圖1所示,可以看到使用了1個全局時鐘。

元件的引用

在Xilinx的FPGA/EPLD的原理圖設計中需要用到元件庫,元件庫中包含一些特殊功能的元件,例如延遲鎖相環(DLL)、全局時鐘BUF、邊界掃描電路、數字時鐘管理器(DCM)、內置SRAM等。LeonardoSpectrum提供的exemplar庫中的程序包使得設計者可以在VHDL程序中直接引用原理圖庫中所包含的元件。引用元件時,先調用exemplar庫,對要引用的元件按照原理圖庫中的描述進行聲明。引用元件時可以只使用其中一部分參數,不必對元件所有的參數進行映射。

下面是引用Xilinx的FPGA的延遲鎖相環〔DLL〕的例子。

............

ARCHITECTURE rtl of pll IS

SIGNAL clk :std_logic;

component clkdll --鎖相環

port(clkin,clkfb,rst :in std_logic;clk0,clk90, clk180,clk270,clkdv,locked :out std_logic);

end component;

BEGIN

CLK1: clkdll port map(clkin=>clkin,clkfb=>clk,rst=>'0', clk0=>clk,clk90=>clkout );

process(clk)

begin

if(clk'event and clk='1') then

data_out<=data_in;

end if;

end process;

END rtl;

這個程序也選用Xilinx的XC2S50-5QP208,經LeonardoSpectrum綜合后,用Xilinx ISE5.1進行map后的結果如圖2所示,可以看到使用了一個DLL。

RAM的綜合

RAM設計是Xilinx FPGA的一個特色,按照在芯片內的分布情況可以分為分布式RAM和塊狀RAM,分布式RAM分布在每個LC中,可以將一個LC作為16×1的同步RAM使用,也可以將兩個LC聯合起來作為16×2、32×1的同步RAM或者16×1的雙口RAM使用,塊狀RAM是專用的分布FPGA邊緣的RAM塊。RAM使用時又可以作為ROM,單口RAM、雙口RAM等。如果是原理圖設計,可以在選擇元件時選擇不同的元件來選擇不同類型的RAM,但是對于用描述語言來進行RAM設計時,就需要綜合工具的支持,不同的綜合工具,對相同的語句,可能就綜合成不同類型的RAM。LeonardoSpectrum對VHDL的支持達到相當的高度,除了提供屬性的方法來使用分布式RAM和塊狀RAM外,還可以在設計時使用不同的描述語句來產生分布式RAM和塊狀RAM。下面是一個綜合成塊狀RAM的例子。

......

ARCHITECTURE rtl of blockram IS

TYPE RAM IS ARRAY ( 0 TO 127 ) OF STD_LOGIC_VECTOR( 7 DOWNTO 0 );

SIGNAL testram :ram;

SIGNAL cc1,cc2 :std_logic_vector(6 downto 0);

SIGNAL addr1,addr2 :integer range 0 to 127;

BEGIN

......

process(clkout) --從RAM中讀出數據

begin

if(clkout'event and clkout='1') then

data_out<=testram(addr2);

end if;

end process;

END rtl;

該程序也選用Xilinx的XC2S50-5QP208,經LeonardoSpectrum綜合后,用Xilinx ISE5.1進行map后的結果如圖3所示,可以看到生成了塊狀RAM。

下面程序是綜合成分布式RAM的例子。

......

ARCHITECTURE rtl of disram IS

TYPE RAM IS ARRAY ( 0 TO 127 ) OF STD_LOGIC_VECTOR( 7 DOWNTO 0 );

SIGNAL testram :ram;

SIGNAL cc1,cc2 :std_logic_ vector(6 downto 0);

SIGNAL addr1,addr2 :integer range 0 to 127;

BEGIN

......

process(clkout) --從RAM中讀出數據

begin if(clkout'event and clkout='1') then

if(ramsel='1') then data_out<=testram(addr2); end if; end if;

end process;

END rtl;

選用XC2S50-5QP208,經LeonardoSpectrum綜合后,用Xilinx ISE5.1進行map后的結果如圖4所示,可以看到生成了分布式雙口RAM。

比較上面兩段程序,可以看到它們的差別就在于生成分布式RAM的程序中,數據輸出時有一個selram信號,也就是說,如果直接用時鐘讀出RAM中的數據,就綜合成塊狀RAM;如果是用帶使能的方式輸出RAM中的數據,就綜合成分布式RAM。

結語

綜上所述, LeonardoSpectrum對于用VHDL寫的用于Xilinx FPGA的程序支持是非常到位的,可以充分利用Xilinx的優勢,用語言設計出與原理圖設計相當功能的程序。

- 使用Le(5699)

- DL程序(5404)

相關推薦

Vivado 高層次綜合

2582

2582Xilinx ISE Design Suite 14.2 安裝圖解

61264

61264

Xilinx FPGA案例學習之Vivado設計綜合約束

4238

4238

2NBS14-RG3-221331LF

2NBS14-RJ1-472LF

2NBS16-RF1-472LF

2NBS16-TF1-472LF

2NBS16-TF3-221331LF

2NBS16-TJ1-472LF

2NBS8-RF1-472LF

2NBS8-RG3-221331LF

2NBS8-RJ1-472LF

2NBS8-TF1-472LF

2NBS8-TF3-221331LF

2NBS8-TG1-472LF

2NBS8-TJ1-472LF

LeonardoSpectrum Level 3Synplify 6.0以及Synopsys Express3.4三種綜合工具對比分析,哪個好?

Xilinx 9.2i實施不起作用

Xilinx FPGA入門連載13:PWM蜂鳴器驅動之綜合、實現與配置文件產生

Xilinx FPGA無痛入門,海量教程免費下載

Xilinx ISE中的報告未更新

Xilinx Platform Cable USB

xilinx EDF已經綜合過的網表文件怎樣添加到Vivado工程中?

FPGA開發工具----ISE 開發工具、簡介、作用

FPGA的邏輯仿真以及邏輯綜合的一些原則

FPGA設計高級技巧Xilinx篇

FPGA高級時序綜合教程

GSM給您解釋解釋XILINX XST綜合的選項的含義(完成)

ISE 自帶可綜合模塊的問題

ISE 自帶可綜合模塊的問題

Synplify 綜合 UDP 模塊

verilog 循環以及@(clock)的綜合

介紹FPGA的綜合(轉)

基于 FPAG xilinx vivado 仿真模式介紹

如何使用Xilinx工具進行自下而上的合成?

如何使用DCNXT實現物理綜合?

如何理解Xilinx的RTL圖

如何設計完整的FPGA?需要經過哪些流程?

是否有Xilinx或任何其他實例提供的編碼風格指南?

是否有可能在不修改代碼的情況下按順序操作Xilinx綜合選項?

有關verilog的綜合

物理綜合期間未定義的符號

程師分析實例,帶你走近Xilinx FPGA設計[轉]

請問Xilinx FIFO支持virtex5嗎?

UART 4 UART參考設計,Xilinx提供Verilo

156

156usb xilinx源代碼

41

41FPGA CPLD設計工具——Xilinx ISE使用

197

197在PLD開發中提高VHDL的綜合質量

22

22在PLD開發中提高VHDL的綜合質量

395

395

在PLD開發中提高VHDL的綜合質量

579

579

Xilinx宣布收購高層綜合技術領先的AutoESL

957

957Xilinx FPGA開發實用教程(第2版)-徐文波、田耘

11268

11268

關于高阻態和OOC(out of context)綜合方式

5424

5424威視銳&Xilinx

3934

3934Xilinx FPGA開發工具總結

8910

8910設計輸入、C 仿真、C 綜合以及 C/RTL 協同仿真

3506

3506Vivado使用技巧分享:OOC綜合技術運行流程

3081

3081

Xilinx 7系列FPGA介紹

14064

14064NBS橡膠磨耗試驗機的用途都有哪些

551

551FPGA的設計流程指南詳細資料說明

9

9FPGA的綜合詳細教程

26

26Xilinx FPGA時序約束設計和分析

768

768 電子發燒友App

電子發燒友App

評論