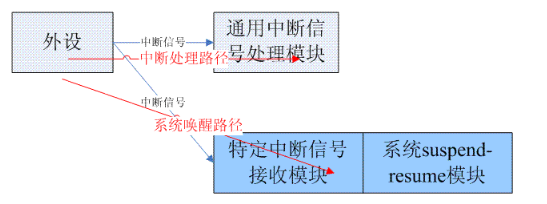

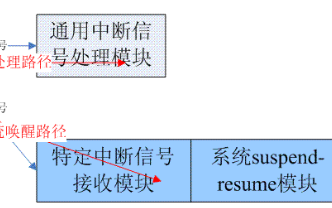

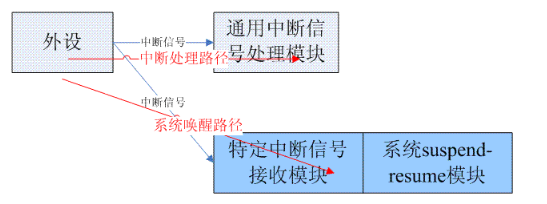

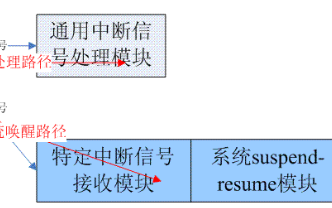

在中斷申請的時候,IRQF_NO_SUSPEND flag可以用來告知IRQ subsystem,這個中斷就是上一段文字中描述的那種中斷:需要在系統的suspend-resume過程中保持enable狀態。

2020-09-21 14:29:27 5897

5897

ARM處理器是一種流行的處理器架構,用于許多現代移動設備和嵌入式系統中。中斷和異常是ARM處理器中的兩個重要概念,它們是處理器中斷程序執行的關鍵機制。

2023-09-05 15:45:30 695

695

的優先級等,而處理器則由寄存器設置用來響應中斷。二、GIC作為 ARM 系統中通用中斷控制器的是 GIC(Generic Interrupt Controller),目前有四個版本,V1~V4(V2最多

2021-05-14 06:30:00

對于ARM的處理器,中斷給處理器提供了觸覺,使處理器能夠感知到外界的變化,從而實時的處理。本系列博文,是以ARM cortex-A系列處理器,來介紹ARM的soc中,中斷的處理。ARM

2022-04-06 10:12:14

在嵌入式系統中常用的RISC處理器是ARM核,它具有體積小、功耗低、成本低、性價比高的特點。然而,不管是哪種型號的ARM處理器,也無論該嵌入式系統中是否有操作系統,中斷處理,特別是IRQ中斷,始終是

2011-05-04 16:06:07

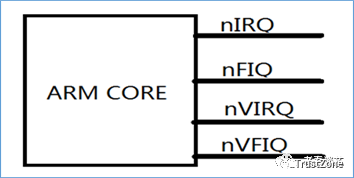

pin, 一根叫fiq pin。在ARM的cpsr中,有一個I位和一個F位,分別用來禁止IRQ和FIQ。先不說中斷控制器,只說ARM核心。正常情況下,ARM核都只是機械地隨著pc的指示去做事情,當

2017-10-13 21:16:06

,CPU此時正在處理其他事情,當接收到這個信號會打斷當前cpu正在處理的事情。1)ARM有兩級外部中斷,FIQ和IRQ2)基于ARM系統的大多數有兩個中斷源中斷控制器:使cpu和外面可以接多個中斷源,作中斷

2022-05-05 10:16:31

此時正在處理其他事情,當接收到這個信號會打斷當前cpu正在處理的事情。1)ARM有兩級外部中斷,FIQ和IRQ2)基于ARM系統的大多數有兩個中斷源中斷控制器:使cpu和外面可以接多個中斷源,作中斷

2022-04-26 09:37:10

ARM中斷機制 當事件發生時,通過一種機制告訴CPU現在發生什么事件,CPU停下現在所做的工作進行處理。中斷處理流程:中斷控制器匯集各類外設發出的中斷信號,經過一段處理,選出一個信號,然后通知CPU

2014-03-05 09:48:38

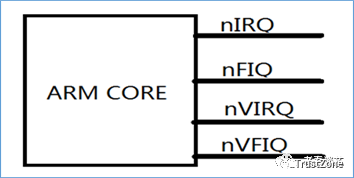

1、ARM中斷硬件機制ARM 有兩級外部中斷 FIQ,IRQ.可是大多數的基于ARM 的系統有 >2個的中斷源!因此需要一個中斷控制器(通常是地址映射的)來控制中斷是怎樣傳遞給ARM

2022-05-30 11:03:03

※ 概念 IRQ(Interrupt Request):指中斷模式。 FIQ(Fast Interrupt Request):指快速中斷模式。 IRQ與FIQ是ARM處理器的兩種不同編程模式(ARM

2014-10-13 10:43:58

ARM處理器中斷處理的理解

2012-08-20 12:36:05

ARM處理器中斷處理的編程是怎么實現的?

2021-04-27 06:46:53

、設備 初始化用戶程序執行環境 改變處理器模式 呼叫主應用程序 5.IRQ 和 FIQ 之間的區別 IRQ和FIQ是ARM處理器的兩種編程模式。IRQ是指中斷模式,FIR是指快速中斷模式

2020-11-17 16:13:49

。ARM處理器模式ARM微處理器支持7種運行模式,分別為:用戶模式(usr):ARM處理器正常的程序執行狀態。快速中斷模式(fiq):用于高速數據傳輸或通道處理。外部中斷模式(irq):用于通用的中斷

2011-01-27 11:13:20

。ARM處理器模式ARM微處理器支持7種運行模式,分別為:用戶模式(usr):ARM處理器正常的程序執行狀態。快速中斷模式(fiq):用于高速數據傳輸或通道處理。外部中斷模式(irq):用于通用的中斷

2011-01-27 14:19:05

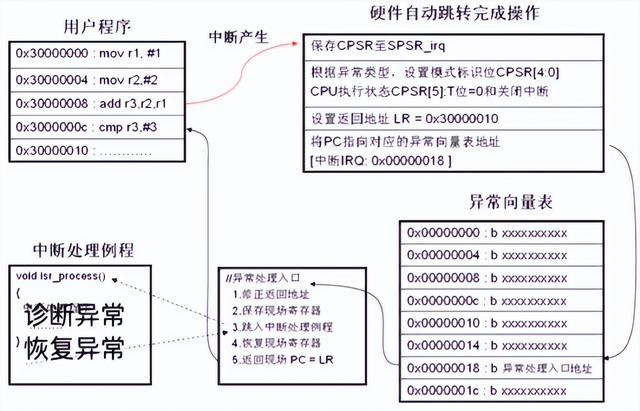

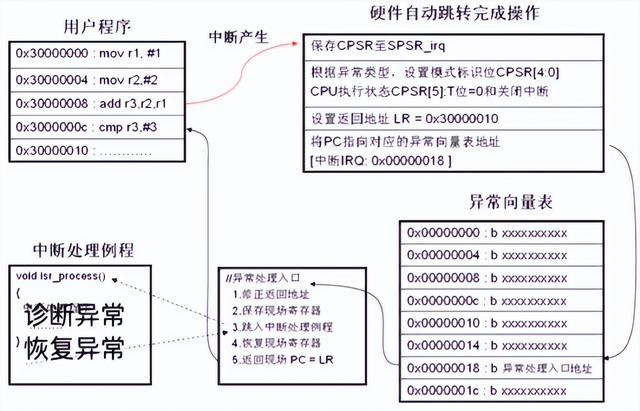

ARM處理器異常相應過程:1、保存處理器當前狀態、中斷屏蔽位以及各個條件標志位。將當前程序狀態寄存器CPSR保存到對應的SPSR寄存器中實現。每個異常中斷都有對應的物理SPSR寄存器。2、設置

2021-12-14 08:57:34

1.“站的高尿的遠” GIC為中斷控制器,不要和ARM core的中斷搞混了,這些中斷都是連接到ARM core的IRQ或者FIQ上的。 要了解arm中斷系統,GIC絕對不容錯過,好先付

2018-11-26 13:50:47

1、通用中斷處理器的介紹今天來看一下中斷及ARM體系中對中斷的處理,直接進入正題。中斷是指計算機運行過程中,出現某些意外情況需主機干預時,機器能自動停止正在運行的程序并轉入處理新情況的程序,處理

2022-04-13 18:09:18

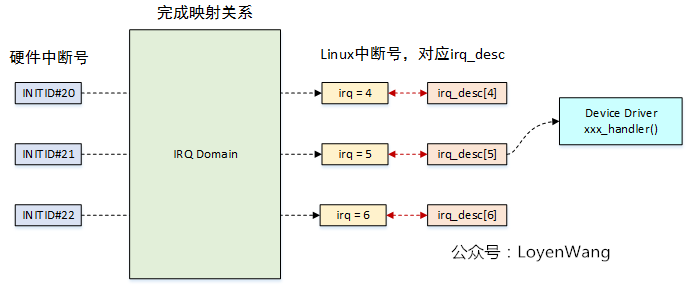

是linux內核程序來讀取寄存器),寄存器返回硬件中斷號;第六步,CPU處理完中斷后寫GICC_EOIR寄存器來通知CPU interface。硬件中斷號與Linux軟件中斷號的映射每一款ARM SOC在

2022-04-21 10:01:17

:中斷向量表初始化存儲器系統初始化堆棧初始化有特殊要求的端口、設備初始化用戶程序執行環境改變處理器模式呼叫主應用程序5.IRQ 和 FIQ 之間的區別答:IRQ和FIQ是arm處理器的兩種編程模式。IRQ是指

2016-08-05 10:45:04

現場,在從異常中斷處理程序退出時,要恢復被中斷的程序的執行現場。本文討論ARM體系中的異常中斷機制。ARM體系中異常中斷種類:ARM體系中異常中斷如下面的介紹。復位(Reset):當處理器的復位引腳有效

2020-08-28 08:09:17

,#4PC+4數據中止SUBSPC,R14_abt,#8PC+8中斷處理當外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發生時,ARM核完成一部分工作。當然,這些

2013-05-24 10:30:42

,#4PC+4數據中止SUBSPC,R14_abt,#8PC+8中斷處理當外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發生時,ARM核完成一部分工作。當然,這些

2013-08-09 16:15:24

,R14_abt,#8PC+8中斷處理當外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發生時,ARM核完成一部分工作。當然,這些工作是任何異常發生時都必須要做的,所以

2013-04-08 10:53:07

在學習與開發ARM處理器的過程中,一個不能繞開的話題就是異常處理流程。它在ARM的體系架構中,占據著不可動搖的重要地位。此處就以Coterx-A系列的ARM處理器簡單分析一下異常中斷處理流程。說異常

2016-11-11 09:55:57

在學習與開發ARM處理器的過程中,一個不能繞開的話題就是異常處理流程。它在ARM的體系架構中,占據著不可動搖的重要地位。此處就以Coterx-A系列的ARM處理器簡單分析一下異常中斷處理流程。說異常

2016-10-14 16:15:42

經典ARM微處理器包括7種異常:1、 復位異常2、 未定義指令異常3、 軟件中斷異常4、 預取指令異常5、 數據異常6、 IRQ(中斷)7、 FIQ(快速中斷)異常,單片機為中斷,籠統來講可以把異常

2021-07-16 07:04:57

ARM的中斷系統可分為5個步驟:1.初始化:端口設置FIQ、IRQ開關:PSR的F(IQ)、I(RQ)位進行設置。1表示禁止,0表示允許。屏蔽中斷源:INTMAST寄存器的讀寫,其中1為禁止,0為

2014-10-09 09:33:50

低于FIQ。對于FIQ序列它是被屏蔽的。任何時候在一個特權模式下,都可通過置位CPSR中的I 位來禁止IRQ。不管異常入口是來自ARM狀態還是Thumb狀態,FIQ處理程序都會通過執行下面的指令從中斷返回

2020-04-20 10:52:02

M0內核支持的資源Cortex-M0處理器最多支持32個外部中斷(通常稱作IRQ),還有一個被稱作不可屏蔽中斷的特殊中斷。中斷事件的異常處理通常被稱作中斷服務程序(ISR)。除此之外,M0處理器還

2021-12-21 06:50:48

接下來的時鐘里(處理器向0x1C取指令),ARM核使R14_irq減4 ②ARM內核進入IRQ模式 ③當指令LDR PC,[PC,#&F20]得到執行(ARM為流水線結構,當前PC之前還有兩條

2011-05-31 09:53:07

最近在學習LPC2294的ARM,想通過中斷來實現UART0的讀寫,現在一直不能進入中斷處理程序,資料上的關于IRQ中斷的部分也沒有看明白,不知道該怎么把VICVectAdd6(我選擇的是6的優先級

2015-10-14 22:02:53

!= IRQ_TYPE_EDGE_RISING) return -EINVAL; 在這種情況下,SPI 表示“共享處理器中斷”(來自 ARM GIC 手冊......我不得不查找它的含義),但我在

2023-03-24 06:45:09

NRF24L01 使用IRQ中斷處理收發中斷,六發一收。

2018-01-01 19:38:59

上一節講了如何實現運行中斷,這些都是系統給做好的,當我們想自己寫個中斷處理程序,去執行自己的代碼,就需要寫irq_desc->action->handler,然后通過

2022-01-25 07:20:23

IRQ_OSMR0為最高優先級, IRQ_KEYPAD為最低優先級. 2.2 設置ICCR,在空閑模式時只對有效的,非屏蔽的中斷響應. 2.3 BSPIntrInit().該函數對BSP中需要處理的中斷進行

2011-03-01 10:57:02

,R14_abt,#8PC+8中斷處理當外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發生時,ARM核完成一部分工作。當然,這些工作是任何異常發生時都必須要做的,所以

2015-07-27 15:31:14

程序的地址賦給該指針,從而將中斷與中斷服務程序聯系起來。 為了方便使用高級語言編寫異常處理函數,ARM編譯器對異常處理函數作了特定的擴展,只要使用關鍵字__irq,編譯出來的函數就滿足異常響應對現場

2019-07-29 04:30:00

,R14_abt,#8PC+8中斷處理當外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發生時,ARM核完成一部分工作。當然,這些工作是任何異常發生時都必須要做的,所以

2013-03-22 16:20:47

,R14_abt,#8PC+8中斷處理當外部中斷IRQ和FIQ(Fast Interrpt Request,快速中斷請求)發生時,ARM核完成一部分工作。當然,這些工作是任何異常發生時都必須要做的,所以

2013-03-22 16:34:17

0; }四.ARM Linux中斷處理過程分析(3)在之前的文章中,我分析了進入IRQ之前處理器模式為SVC的情況,在本篇文章中,將要討論的是進入IRQ之前處理器模式為USR的情形。843

2020-08-27 10:48:39

因為項目要通過485傳送數據,所以要用到串口,在調試串口的時候接收用的是中斷,發送準備用查詢模式。發送的中斷用的是下面一段程序:__irq __arm void IRQ_Handler(void

2018-11-21 09:31:18

因為項目要通過485傳送數據,所以要用到串口,在調試串口的時候接收用的是中斷,發送準備用查詢模式。發送的中斷用的是下面一段程序:

__irq

__arm void IRQ_Handler(void

2024-01-15 08:06:05

5.IRQ 和 FIQ 之間的區別 答:IRQ和FIQ是ARM處理器的兩種編程模式。IRQ是指中斷模式,FIR是指快速中斷模式。對于 FIQ 你必須盡快處理你的事情并離開這個模式。IRQ 可以被 FIQ

2018-08-18 04:43:09

半部的處理過程中,中斷是被禁止的;在下半部處理耗時的事情,在下半部的處理過程中,中斷是使能的。根據處理時間不同引用的中斷下半部函數驅動編寫分配tasklet為每個按鍵分配一個tasklet,用于處理

2022-05-17 10:16:50

。 這樣的原理其實也沒什么不妥,我接觸過的低端的CPU都是這個樣子工作的。其實中端的ARM soc也是這么工作的,只是比較復雜罷了。 現代的中高端arm芯片都有PIC(可編程中斷控制器),所有

2022-05-30 09:23:57

好所有的保存動作了,并不需要多關心。但是這個是 ARM-CC 編譯器的關鍵字,GCC中并沒有這個東西,所以GCC處理中斷的時候最好還是自己保存一下。

2016-12-02 16:34:39

好所有的保存動作了,并不需要多關心。但是這個是 ARM-CC 編譯器的關鍵字,GCC中并沒有這個東西,所以GCC處理中斷的時候最好還是自己保存一下。深圳專業嵌入式ARM、Linux、單片機專業技術實訓,學習顧問郭老師:QQ754634522

2013-11-11 15:40:18

小步保存執行狀態:將CPSR復制到發生的異常模式下SPSR中;模式切換:CPSR模式位強制設置為與異常類型相對應的值,處理器進入到ARM執行模式,禁止所有IRQ中斷,當進入FIQ快速中斷模式時禁止

2022-08-18 15:26:04

有IRQ發生,而在該周中,正在預取 SUB減法指令,在下一2周期中即2周期中EI(處理中斷),而該2周期中,預取指令已經預取到了X指令,所以PC的值為0x00C,該值被備份到了LR中。當中斷返回后因

2022-04-26 09:29:21

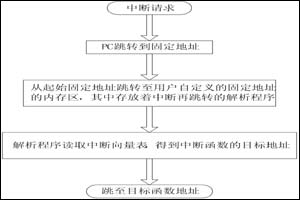

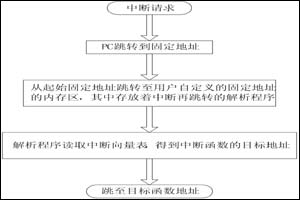

下面講講ARM9中斷控制器的控制流程:1.首先能識別觸發的中斷(對應中斷源必須打開,然后查詢當前中斷狀態寄存器),硬件會操控PC跳到中斷向量入口(IRQ_HANDLE,硬件控制的只要是IRQ中斷類型

2020-08-29 08:25:23

看到開發版原理圖上phy的中斷連接到了cpu的外部中斷IRQ7 IRQ8,在芯片手冊上看到該外部中斷屬于programable interrupt controller(PIC),但是沒找到更詳細

2022-01-05 07:38:44

我在設計中要利用__disable_irq();__enable_irq()來實現原子操作,防止中斷與正常運行程序同時訪問數據造成不一致,但是這個是暫時屏蔽全局中斷的。我系統中有個最高優先級的是不能

2018-08-27 10:15:06

這里只討論SVC、IRQ和FIQ模式。 我們可以假設ARM核心有兩根中斷引腳(實際上是看不見的),一根叫 irq pin, 一根叫fiq pin。在ARM的cpsr中,有一個I位和一個F位,分別

2017-09-21 21:00:09

以 ARM7TDMI處理器為例,詳細介紹 ARM內核的三種中斷:常規中斷、快中斷和軟件中斷;結合應用,給出優化的中斷處理程序的ARM指令代碼,對電子設計人員有較大的參考價值。

2009-04-09 10:01:19 18

18 針對ARM7微控制器的IRQ中斷向量地址動態分配在中斷向量寄存器中的特點,提出將中斷向量固化到ROM中的思路,構建IRQ中斷防御體系,從而增強了系統的可靠性和安全性。

2010-12-11 15:51:03 26

26 摘要:本文首先簡要概述了ARM處理器的異常中斷種類、響應和返回過程;然后重點討論了中斷解析程序的原理和實現,并分別給出了普通中斷和向量中斷的處理示例流程圖和詳細

2006-03-11 12:18:54 760

760

一、了解IRQ家族??IRQ全稱為Interrupt Request,即是“中斷請求”的意思(以下使用IRQ稱呼)。IRQ的作

2006-04-17 22:51:00 1794

1794 s3c2410中斷程序在此要注意的是區別中斷向量表和異常向量表。中斷發生后總是從IRQ 或者FIQ 異常

2008-09-11 18:49:40 2188

2188 uCOS II在ARM處理器上移植過程中的中斷處理

uCOS II是一個源碼公開、可移植、可固化、可剪裁和搶占式的實時多任務操作系統,其大部分源碼是用ANSI C編寫,與處理器硬

2010-01-25 11:14:24 1532

1532 在ARM體系結構中,硬件產生的外部中斷( IRQ) 具有單一的程序入口。為了識別中籽源,進而運行對應的中斷服務例程( ISR) ,程序需讀取中斷懸掛寄存器,獲得中斷號。在這種方式中,程序必須通

2011-06-27 15:45:24 64

64 對ARM處理器的普通中斷處理、任務切換中斷處理、可重人中斷處理和基于優先級的可重人性中斷處理的上下文保存技術進行分析與總結。為保證理論的正確性,核心的程序代碼都經過了

2011-07-06 12:08:09 4166

4166

以三星的 S3C4510 嵌入式平臺為基礎,討論了ARM7系統的中斷設計方案,包括ARM7中斷系統的特點、三星S3C4510的配置、中斷向量表的建立等,提出了中斷處理的一些優化措施

2011-08-16 14:15:12 198

198 1、ARM處理器工作模式有幾種?各種工作模式下分別有什么特點? 答:ARM 處理器有7種工作模式,這7種模式及其特點是: 快速中斷模式(fiq) 支持高速數據傳輸或通道處理,外部中斷fiq信號有效

2017-09-30 11:08:37 14

14 3.4 異常中斷處理 異常或中斷是用戶程序中最基本的一種執行流程和形態。這部分主要對ARM架構下的異常中斷做詳細說明。 ARM有7種類型的異常,按優先級從高到低的排列如下:復位異常(Reset

2017-10-18 13:29:56 1

1 在這種模式下 快速中斷模式(FIQ)fiq當一個高優先級(fast)中斷產生時將會進入這種模式,一般用于高速數據傳輸和通道處理 外部中斷模式(IRQ)irq當一個低優先級(normal)中斷產生時將會進入這種模式,一般用于通常的中斷處理 特權模式(Supervisor)svc當復位或軟中斷指令執行時進入

2017-10-18 15:57:44 2

2 本文介紹A了RM S3C4510B系統 的 異常中斷 機制,包括異常中斷的分類,響應與返回;中斷處理程序的安裝與調用;SWI,IRQ中斷的實例與關鍵代碼。隨著人們對于電子產品的要求越來越高

2018-02-03 05:32:01 1561

1561

不同的,個人感覺 LPC 的要難一些,很多地方感覺上是在和 ARM 的規范打擦邊球,下面具體說一下相關內容。 基礎知識: LPC2294 的 EXT 中斷分為了三類,包括 FIQ , Vectored IRQ

2018-05-30 01:22:00 4923

4923 可見,ARM Linux最初進入IRQ模式后,比較快速地從IRQ模式切換到了SVC模式,但是這個時候,并沒有使能CPSR的I bit,所以仍然是禁止其他中斷嵌套進入的。

2018-07-27 14:54:49 4111

4111

IRQ,FIQ定義: 這就是個普通中斷,當我們程序定義了該中斷,并且在程序運行的時候產生了IRQ中斷,則此時的芯片是這樣運行的------中斷處理器吧利用IRQ請求線來高速ARM,ARM就知道

2018-10-27 11:20:47 9541

9541 阻止中斷的遞交。此外,在過去的代碼中(指interrupt handler),我們對設備共享IRQ的情況處理的不是很好,存在這樣的問題:在共享IRQ的設備們完成suspend之后,如果有中斷觸發,這時候設備驅動的interrupt handler并沒有準備好。

2019-05-06 16:36:34 1447

1447

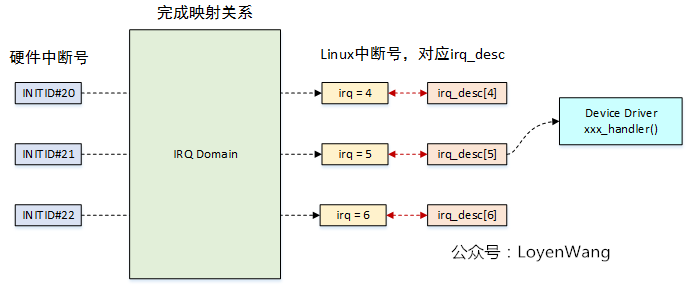

linux內核將所有的中斷統一編號,使用一個irq_desc[NR_IRQS]的結構體數組來描述這些中斷:每個數組項對應著一個中斷源(可能是一個中斷,也可能是一組中斷),記錄了中斷的入口處理函數(不是用戶注冊的處理函數)、中斷標記,并提供了中斷的底層硬件訪問函數(中斷清除、屏蔽、使能)。

2019-05-07 11:13:56 875

875 在Linux中斷子系統(generic irq)出現之前,內核使用__do_IRQ處理所有的中斷,這意味著__do_IRQ中要處理各種類型的中斷,這會導致軟件的復雜性增加,層次不分明,而且代碼的可重用性也不好。

2019-05-10 10:56:09 1325

1325 在前一個專題里曾分析過所有IRQ中斷處理流程,經過SAVE_ALL保存硬件環境后,都會進入do_IRQ()進行處理,今天接著分析do_IRQ()處理的相關東西.分為兩部中斷處理程序與軟中斷兩個大的部份進行介紹.

2019-05-10 10:57:43 2274

2274 通用中斷子系統把幾種常用的流控類型進行了抽象,并為它們實現了相應的標準函數,我們只要選擇相應的函數,賦值給irq所對應的irq_desc結構的handle_irq字段中即可。

2019-05-15 11:30:15 547

547

控制IRQ和FIQ中斷的編譯器內部函數 - 基于Keil MDK

2020-02-29 16:45:56 2024

2024 當ARM異常中斷發生時,系統執行完當前指令后,將跳轉到相應的異常中斷處理程序處執行。當異常中斷處理程序執行完成后,程序返回到發生中斷指令的下條指令處執 行。在進入異常中斷處理程序時,要保存被中斷程序的執行現場,從異常中斷處理程序退出時,要恢復被中斷程序的執行現場。

2020-06-17 10:05:12 7044

7044 外部中斷請求(IRQ) 當處理器的外部中斷請求引腳有效,而且CPSR的寄存器的I控制位被清除時,處理器產生外部中斷請求異常中斷。系統中個外設通過該異常中斷請求處理服務。

2020-08-27 14:21:29 2354

2354 ARM的FIQ模式提供了更多的banked寄存器,r8到 r14還有SPSR,而IRQ模式就沒有那么多,R8,R9,R10,R11,R12對應的banked的寄存器就沒有,這就意味著在ARM的IRQ模式下

2020-11-10 17:22:14 4856

4856 或中斷請求(IRQ)。幾乎所有的現代處理器都支持異常和中斷,微控制器的中斷可以由片上外設或軟件產生。由此可見,通常我們處理的中斷是異常的一種。 每種異常類型都有對應的優先級,有些異常的優先級是固定的,有些是可編

2021-10-12 17:14:18 4165

4165 MCU中斷嵌套總結--51,STM32,DSP,ARM一、51單片機1、默認中斷優先級(邏輯優先級)為:2、IP寄存器設置了某一位(物理優先級),比如:PS (IP.4):串行口中斷優先

2021-11-05 20:35:58 7

7 ARM的P0.25接一個LED,引腳設置時連接EINT1功能,按鈕觸發中斷。中斷服務程序另LED快速閃爍。#include <LPC2124.H>#define

2021-11-26 21:06:04 6

6 上一節講了如何實現運行中斷,這些都是系統給做好的,當我們想自己寫個中斷處理程序,去執行自己的代碼,就需要寫irq_desc->action->handler,然后通過

2021-11-30 18:36:12 13

13 導致升級失敗。ARM MDK中提供了如下兩個接口來禁用和開啟總中斷:__disable_irq(); // 關閉總中斷__enable_irq(); // 開啟總中斷 但測試發現這樣一個問題,在關閉總中斷后,如果有中斷觸發,雖然此時不會引發中斷,但在調用__enable_irq()開啟總中斷后,M

2021-12-09 09:36:05 11

11 編譯器內部函數__disable_irq、__enable_irq、__disable_fiq和__enable_fiq用于控制IRQ和FIQ中斷。

2022-01-26 17:16:53 1

1 我們可以假設ARM核心有兩根中斷引腳(實際上是看不見的),一根叫 irq pin, 一根叫fiq pin。在ARM的cpsr中,有一個I位和一個F位,分別用來禁止IRQ和FIQ。

2022-04-07 10:29:51 2918

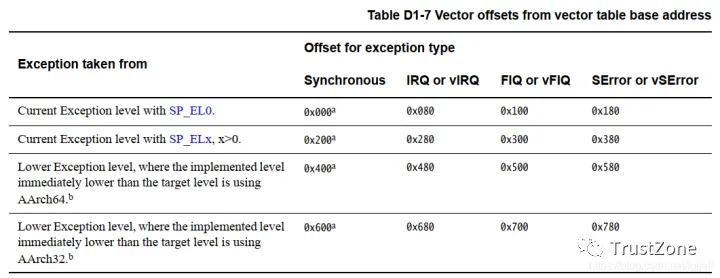

2918 routing到EL1),cpu跳轉至optee的irq中斷異常向量表, 處理完畢后再返回到secure(optee)側.

2022-04-29 10:48:19 3052

3052 的機制,能夠提高系統的實時性和可靠性。在ARM處理器中,中斷的實現主要涉及到下面的幾點。 一、中斷控制器 ARM系統中,中斷控制器是實現中斷的重要組成部分。中斷控制器的主要作用是監控外部硬件中斷請求并向CPU發出中斷請求信號,同時還需要

2023-09-05 16:22:23 618

618 正確處理,處理器可能會崩潰或數據損毀。ARM處理器有七種異常模式,即:重置模式、用戶模式、FIQ模式、IRQ模式、監督模式、中斷模式和異常模式。 1. 重置模式 當ARM處理器啟動時,它將進入重置模式。在這種模式下,處理器處于其最初狀態

2023-09-05 16:22:25 2036

2036 IRQ domain IRQ domain用于將硬件的中斷號,轉換成Linux系統中的中斷號(virtual irq, virq),來張圖: 每個中斷控制器都對應一個IRQ Domain

2023-09-28 15:21:52 280

280

arm處理器有哪些中斷源?arm處理器對異常中斷的響應過程? ARM處理器是一種廣泛使用的嵌入式處理器,運行著各種不同類型的應用程序。為了保證應用程序的穩定性和正確性,ARM處理器需要在遇到異常情況

2023-10-19 16:35:59 675

675 ARM異常返回值的合法值有哪些?各返回值分別代表什么? ARM異常返回值的合法值包括:中斷(IRQ)、中止(ABORT)、未定義指令(UND)、系統調用(SWI)、數據終端(DATA ABORT

2023-10-19 16:36:08 374

374 ARM中的異常中斷是如何實現進入中斷程序的?如何進入呢? 在計算機系統中,異常和中斷是兩個常見的概念。 在ARM中,異常和中斷的主要目的是幫助處理器響應與系統操作相關的事件。 由于處理器必須同時執行

2023-10-19 16:36:11 481

481 如何在特權模式下用arm匯編指令使能和禁止irq中斷? 在 ARM 系統中,中斷是非常常見的一種事件。在特權模式下,可以使用 ARM 匯編指令來使能或禁止 IRQ 中斷。中斷服務程序可以在中斷發生

2023-10-19 16:42:46 612

612 在ARM處理器中,當一個中斷信號被觸發時,中斷控制器會發出一個中斷請求,并將該請求傳遞給CPU。 CPU接收到中斷請求后,會根據中斷號在中斷向量表中查找對應的中斷服務程序入口地址。 中斷

2023-10-30 17:19:02 731

731 今天來看一下中斷及ARM體系中對中斷的處理,直接進入正題。 中斷是指計算機運行過程中,出現某些意外情況需主機干預時,機器能自動停止正在運行的程序并轉入處理新情況的程序,處理完畢后又返回原被暫停的程序

2023-11-07 17:11:52 217

217

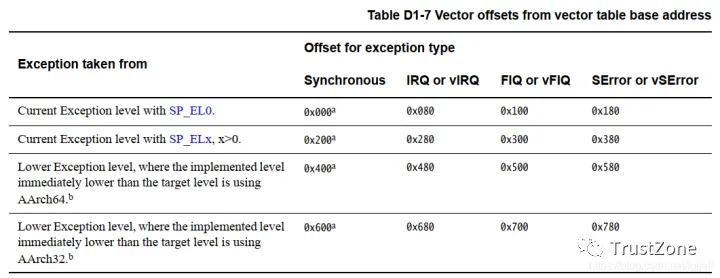

中斷處理需要軟件和硬件配合完成,GICv3根據中斷分組情況以及系統當前運行的異常等級確定中斷是以IRQ還是FIQ觸發。 CPU通過設置SCR_EL3.IRQ和SCR_EL3.FIQ確定IRQ和FIQ

2023-11-07 17:43:16 252

252

的分類 ARM中斷可以分為兩類:外部中斷和內部異常。外部中斷是指來自外部設備(如外部中斷請求線或外設)的中斷信號,而內部異常則是處理器內部出現的異常事件。 外部中斷:ARM處理器通過外部中斷引腳(如IRQ和FIQ)接收外設發送的中斷請求信號。

2024-01-05 15:18:11 206

206

電子發燒友App

電子發燒友App

評論